基于GTX 接口的宇航用高速串口设计与应用

2022-06-23肖斯雨杨凯王冠雄孙泽渝吴杰

肖斯雨 杨凯 王冠雄 孙泽渝 吴杰

(上海航天电子技术研究所, 上海, 201109)

由于宇航器搭载的载荷、 传感器等各类数据采集设备在数量和精度上的巨大提升, 空间电子系统信息流的体量和速率需求迅猛增长, 在满足宇航电子产品信号传输可靠性条件下, 实现10Gbps 量级高速信号传输成为星载高速数据通信的研究难题。 高速串行技术克服了并行设计的速度 “瓶颈”, 还节省了I/O 资源, 使印制板的布线更简单, 这些特点使其更适用于星载单机资源 有 限、 PCB 尺 寸 限 制 等 环 境。 GTX (Gigabit Transceiver, 吉比特收发器) 是一种低功耗的收发器, 配置灵活, 与FPGA 逻辑联系紧密, 可用于实现多种高速串行接口。 目前的GTX 接口线速度有效负载范围为0.8Gbps~10Gbps, 在协议支持下可以在2x、 4x、 8x 的模式下运行。 本文研究FPGA 集成的GTX 高速接口的宇航应用, 面向宇航电子产品针对GTX 接口进行电源完整性与信号完整性设计, 以保证宇航高速串行信号传输接口的可靠性。

1 GTX 收发器接口原理

目前常用同步方式有系统同步、 源同步和自同步。 “系统同步” 利用片外的晶振进行同步,由于板间线路的长度不一致, 以及片内延迟不一致, 在时钟速度较高时可能存在较大误差。 “源同步” 是在发送数据的同时发送一个时钟副本,这种设计需要更多的时钟端口。 “自同步” 将时钟包含在数据流中, 从数据流中进行时钟恢复,不仅端口使用较少, 而且不论是在高速还是低速, 时钟延迟与数据延迟都保持一致, 可以保证采样的正确性。

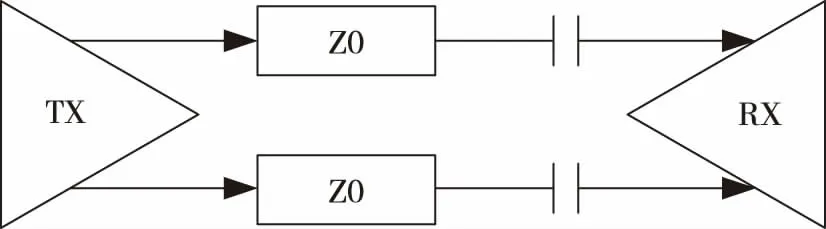

GTX 收发器采用差分信号对数据进行传输。除了利用差分信号外, GTX 采用自同步技术来解决时钟同步问题。 GTX 接口原理框图如图1所示。

图1 GTX 接口原理框图

将速率为y 的n 位宽并行数据转变成速率为n×y 的串行数据。

在输入数据发送之前, 暂时保存数据。

将数据编码成适应不同线路的格式。 编码器通常会消除长的无转变的序列, 同时还可以平衡数据中0、 1 的出现次数。常用的线路编码机制为8B/10B 编码。

与并串转换器的功能相反,将速率为n×y 的串行数据转变成速率为y 的n 位宽并行数据。

修正发送时钟和接收时钟之间的偏差, 同时也可以实现多通道间时钟歪斜的修正。

将线路上的编码数据分解成原始数据。

在接收数据被提取之前,暂时保存数据。

2 应用场景分析

GTX 是一种Serdes 接口, 基于FPGA 的GTX接口有星载板级、 单机级、 系统级等3 种高速互联应用场景。 GTX 接口的通信能力可以覆盖单板内的信号传输距离, 单板内部具有多个高速运算单元时, 采用高速串行通信GTX 接口实现高速运算单元的高速互联架构。

单机级的应用为模块间的GTX 接口高速互联, 可以通过两个Serdes 直连实现, 板间传输的传输线长度通常不超过0.5m, 5Gbps 的速率仍可保证可以接受的信道损耗。

系统级互联通过双星拓扑网络实现, 系统内各个模块均引出两路GTX 配置成的SRIO 接口,分别接入两个SRIO 交换矩阵, 从而组成双星型网络。 系统内部各个子模块在模块内部使用一块RapidIO 互联芯片用于模块内处理单元互联; 也可以将模块内处理器直接接入SRIO 交换实现与存储模块, 如支持DMA 的计算—存储模块、 实时采集模块 (高速AD)、 DSP 阵列等系统互联。

基于单板、 单机、 系统这3 种宇航用应用场景, GTX 接口主要涉及的宇航电子产品应用场景包括: 系统内不同单机间有Gbps 速率量级的数据传输需求, 单机内总线需要具备有Gbps 量级的数据交换能力, 单机内总线需要使用SRIO、PCIE、 SATA、 GbE、 10GbE 等标准化通信协议,单机内部采用网络交换的拓扑架构, 单板内部有多个高速运算单元需要互联通信。 同时, 针对特定情况需要考虑传输路径对GTX 接口的影响, 3种接口存在应用区别, 在此主要针对GTX 共性问题进行设计。

3 电路设计

电路设计主要针对GTX 收发器, 设计接口外围的电源与时钟电路, 还包括电源完整性设计、 信号完整性设计、 耦合电容设计。

3.1 供电与参考时钟设计

GTX 接口的供电标准见表1。 通过对以上轨道的电压利用计算软件XPE 中的快速估算功能计算各个电压轨道的功率, 如图2 所示。

图2 GTX 供电轨道功率估算

表1 GTX 供电端口标准

为优化GTX 接口性能, 需在MGTV、MGTAV、 MGTAV供电轨道上设置滤波电容,保证供电噪声小于10mVpp, 噪声带宽范围在10kHz~80MHz 内。

对于7 系列FPGA 的GTX, 每个Quad 有2个外部差分参考时钟源, 因此对每一个Quad 而言, 可以选择2 个不同的参考时钟, 每个CHANNEL 接收端和发送端都可以独立选择参考时钟, 一组时钟可以给相邻的2 个Quad 使用。

在时钟源与GTX 接收端口之间加0.1μF 的AC 耦合电容可以有效减小传输线路上的噪声并降低功耗, 还可以阻隔通路上的直流信号, 能够为芯片提供理想时钟源。 同时为减小时钟抖动, 在PCB 布线阶段要避免参考时钟链路上出现阻抗突变, 在信号传输路径上出现过孔、 跨层等阻抗突变时要更改设计或采取特殊工艺降低不良影响。

3.2 信号完整性与电源完整性

与电源完整性相关的主要因素为电源噪声,大多数芯片的正常工作电压范围通常在额定值±5%范围内, 而老式的稳压芯片的输出电压精度通常是±2.5%, 电源噪声的峰值幅度不应超过±2.5%。 电源噪声精度通常受各种制约条件限制, 包括负载情况、 工作温度等, 因此在电源设计时需考虑留足余量。

以3.3V 供电芯片为例, 若芯片正常工作电压范围为3.13V ~3.47V, 稳压芯片标称输出3.3V。 安装到电路板上后, 稳压芯片输出3.36V。 那么容许电压变化范围为3.47V-3.36V=0.11V=110mV。 稳 压 芯 片 输 出 精 度±1%, 即3.36V×±1%=±33.6mV。 电源噪声余量为110mV-33.6mV=76.4mV。

为保证逻辑电路能正常工作, 表征电路逻辑状态的电平值必须落在一定范围内。 比如对于3.3V 逻辑, 高电平大于2V 为逻辑1, 低电平小于0.8V 为逻辑0。

与信号完整性 (SI) 有关的因素主要有3类: 反射、 串扰和辐射。 反射是由于传输路径上的阻抗不匹配导致; 串扰是由于线间距导致; 辐射则与高速器件本身以及PCB 设计有关。 由于GTX 接口的通信链路采用了AC 耦合的方式, 因此GTX 接口信号的布线主要的设计因素即为尽量避免传输线路径上出现阻抗突变。 去耦电容设计如图3 所示。

图3 去耦电容设计

根据以上内容, PCB 设计时针对电源完整性与信号完整性作出了以下约束。

a) 信号换层时, 不要改变参考层; 信号换层时, 不改变参考层的网络属性, 减小过孔本身产生的阻抗变化影响, 减小对信号回流路径的影响; 信号换层时, 在信号过孔附近增加一个与参考层同属性的过孔; 若换层前后, 两层参考层的网路属性不同, 要求两参考层相距较近, 减小层间阻抗和返回路径上的压降; 当换层的信号较密集时, 附近的地或者电源过孔之间应保持一定距离, 换层信号很多时, 多打几个对地或者对电源的过孔。

b) 解决串扰的办法是, 高速信号、 时钟信号、 其他数据信号等间距满足3W 原则。 3W 原则是指两相邻信号线中心距不少于信号线宽度的3 倍, 当设计满足3W 原则时, 信号线间由互感、 互容产生的互扰可减少70%。

4 性能测试

本部分主要阐述宇航电子产品的GTX 接口性能测试方法, 该项测试需要地测设备的支持,地测设备连接框图如图4 所示。

图4 性能测试实验框图

地测设备向被测FPGA 发送数据, 数据为测试要求的固定码型, 并记录发送数据量; 被测FPGA 内部将收发数据总线回环, 将地测发送的数据接收后全部传回地测, 待测FPGA 发送结束后, 地测对比发送数据与接收数据, 进行误码比对和数据量比对, 得出丢包数以及数据的误码率。 并根据v=2D/t 计算有效数据速率v (bps), 其中, D 为地测发送数据量 (bit), t为地测开始发送数据到地测收到最后一个数据的耗时 (s)。

测量被测单机的有效数据速率V, V=V× -β,其中, V为有效数据速率 (bps), V为信道开关速率 (bps), 为编码开销, β 为测试误差。

数据测试量要求在全速收发模式下, 收发每个码型的时间不小于1 小时。

图5 信道误码率测试结果图

图6 信号完整性结果图

根据测试结果, GTX 高速传输接口眼图形状良好, 误码率为1e-8, 信号完整性较好, 符合标准规范。 在耦合电容为5μF, 交换速率3.125Gbps工况下, 信号完整性可以保证。

5 结论

通过对GTX 高速串行通信接口进行电路设计与信号完整性设计, 分析宇航电子产品的电路设计与应用场景, 并对GTX 高速接口的PCB 设计完成信号完整性及电源完整性2 方面设计优化后, 得到的结果: 在耦合电容为5μF, 数据吞吐量1.25Gbps 与5Gbps 条 件 下, 完 成 了4 路3.125Gbps 传输速率的信道误码率测试, 结果满足使用要求, 电源完整性及信号完整性满足宇航电子产品要求。