基于CPLD的双CPU冗余通信控制系统研究

2022-06-14肖再南曹唯一陈志强

许 爽,唐 青,肖再南,曹唯一,陈志强

(1.武汉科技大学 冶金装备及其控制省部共建教育部重点实验室,湖北 武汉 430081;2.武汉科技大学 机械传动与制造工程湖北省重点实验室,湖北 武汉 430081;3.武汉科技大学 精密制造研究院,湖北 武汉 430081)

0 引 言

在通信系统中,可靠性是一项重要的技术性能指标,可以保证数据信息在通信过程中高效、连续、安全地运行。在卫星、舰船等复杂系统中,可靠的数据通信可以有效提高工作效率,保障设备安全。随着通信系统复杂度的提高,其技术和保障要求也越来越高,提高其可靠性便具有更加重要的意义。

通信系统的可靠性取决于构成该系统的各部件可靠性以及系统本身的结构,使用可靠性较高的元部件可以有效延长通信系统的平均无故障间隔时间,但一旦部件出现故障,系统就会停机,甚至丢失通信数据。采用容错技术是通过改进通信系统自身结构的方式来提高可靠性的一种常见手段。在容错技术中,可以通过增加具有相同功能的元部件来增加通信系统的冗余度,使系统可以在某个元部件出现故障时仍然可以正常工作。

目前研究中常用的冗余技术有双CPU 冗余控制技术,比如早在2010 年,为了保证单一部件的失效不影响整个通信系统的运行,文献[9]中采用了一种基于Device Net 总线的双CPU 冗余技术来提高系统的可靠性。同样,为了满足通信系统能稳定可靠地完成数据通信,本文采用结构简单明了的双CPU 冗余通信技术。

在通信系统中,常用静态随机存储器SRAM 进行双CPU 的信息数据共享,但两个CPU 直接读/写SRAM 时容易造成冲突。为了完成双CPU 之间的总线切换,同时解决SRAM 的读/写冲突问题,需要引入仲裁模块。本文采用复杂可编程逻辑器件CPLD 作为仲裁模块,分别与两个CPU 连接,完成对双CPU 的故障监测和自动切换,并连接SRAM 作为数据存储器,使双CPU 通过CPLD 对SRAM 进行读/写操作,避免冲突,实现双CPU之间的高速通信和数据共享。

在网络结构上,本文采用以太网网络接口、RS 232通信接口以及RS 422 通信接口,完成控制中心、上位机以及下位机之间的人机交互通信和数据信息传输,构建由双以太网与双RS 422 组成的冗余网络,提高通信的实时性和可靠性。

1 双CPU 冗余结构

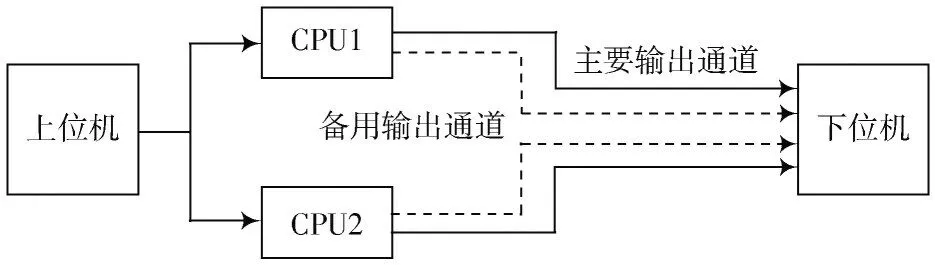

在通信系统中,传统的双机热备份方式是指主、从机同时工作,由主机负责接收数据并进行处理,而从机处于备份运行状态,在主机发生故障时,从机立刻接替工作,提高系统运行的稳定性,待主机恢复正常后,系统又切换至主机运行,不影响其他相关设备。在这种方式下,即使从机处于正常状态,在主机故障修复成功后,仍然要将工作交回给主机运行,在主机故障率高的情况下,系统工作交接频繁,不利于通信的实时性和系统的稳定。为了改善这一情况,本文在传统的双CPU主从热备份方式的基础上对其进行改进,图1 为改进的双CPU 热备份结构图。

图1 改进的双CPU 热备份结构图

在交互通信系统中,上位机传输数据信号给主机,两个CPU 同步接收相关数据,但只有一个CPU 负责主要输出信号到下位机,另一个CPU 则处于监控准备状态,随时准备接管工作。当负责主要输出的CPU 发生故障时,另一个CPU 接管工作,成为主要输出,而原来负责主要输出的CPU 在故障修复后就自动成为备用输出,随时待命。这种方式可以减少主机切换频率,提高通信系统的实时性。

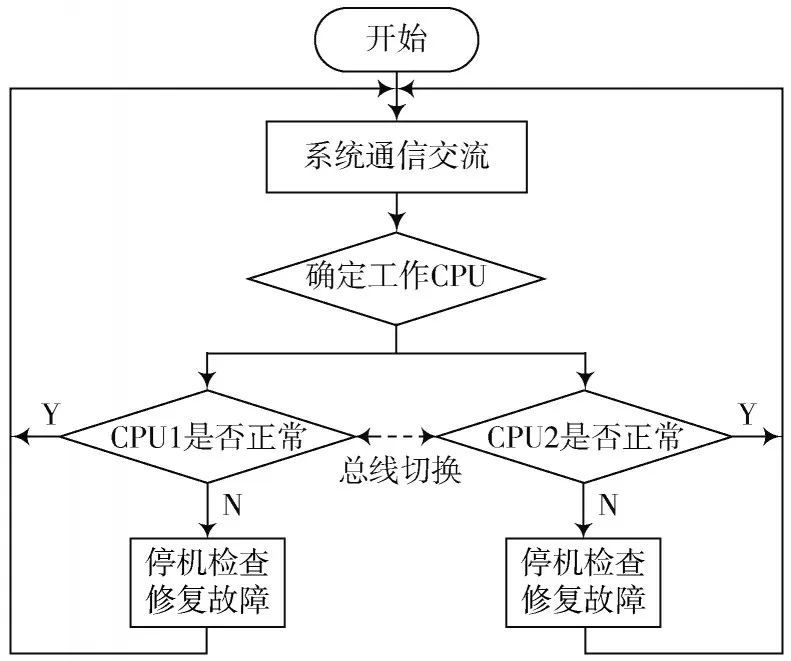

通信系统在正常工作时,两个CPU 将其状态信息上报给仲裁模块CPLD,由CPLD 确认CPU 的工作状态并且实现总线切换。当工作CPU 出现故障时,由CPLD将总线切换到另一个CPU,使整个系统得以继续执行原来的工作,保证通信系统正确、不间断地运行,而原来的工作CPU 在停机检查、修复故障后成为备用CPU,其工作流程如图2 所示。

图2 通信系统中双CPU 工作流程图

2 交互通信系统的可靠性设计

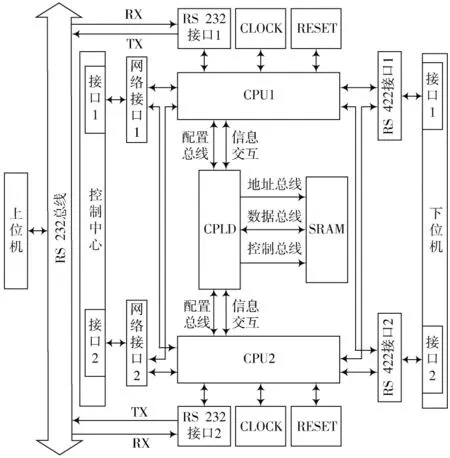

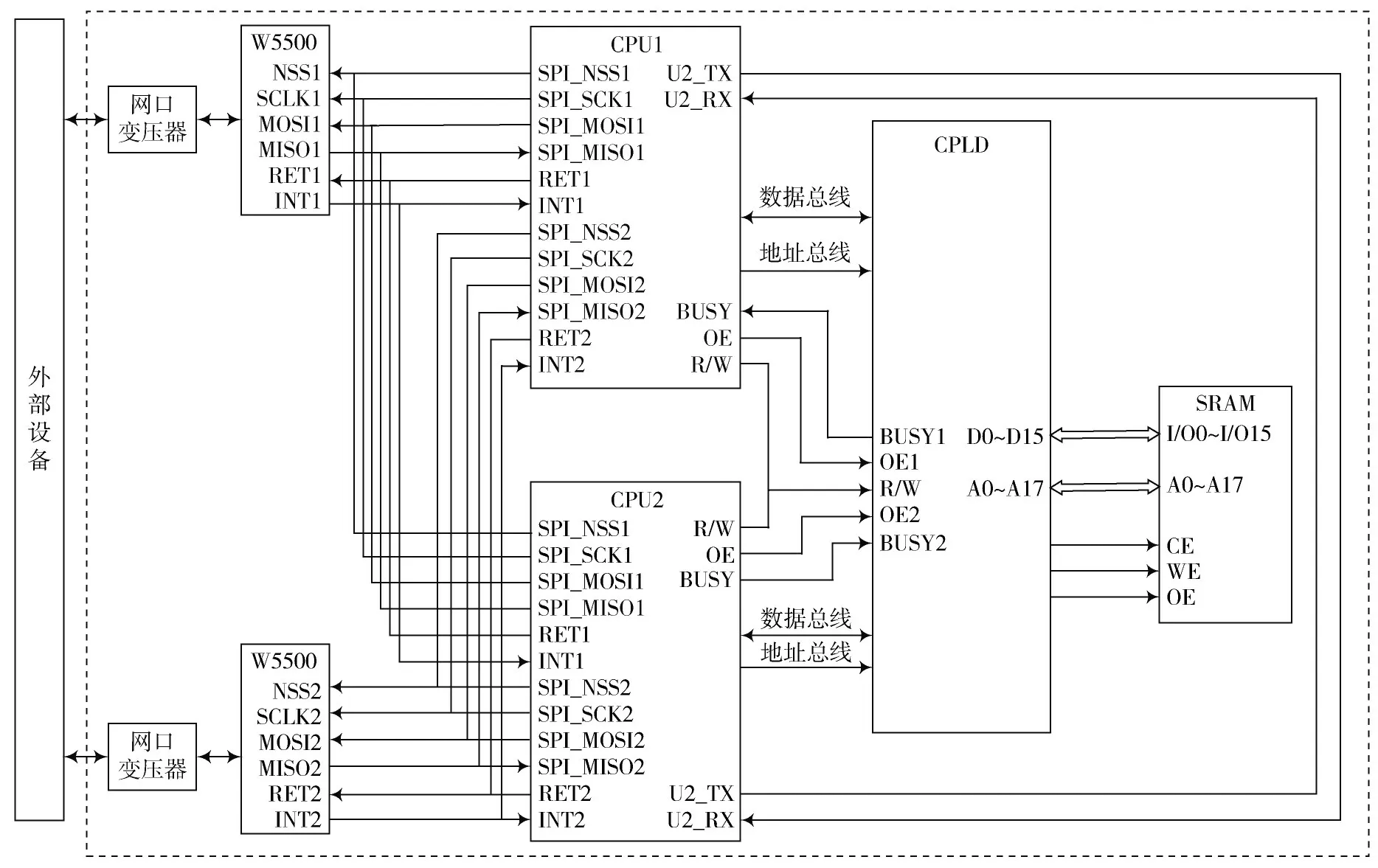

为了提高交互通信系统中数据通信的可靠性,选择通过增加关键元部件和网络结构的冗余度来实现,硬件系统的总体构架如图3 所示。

图3 硬件系统的总体构架

本文的两个CPU 选用的是TI 公司C2000 系列的TMS320F28335,采用C28X+FPU 的 结 构,在C28X 定点系列的基础上增加了浮点运算单元,既保持了原有DSP 芯片性能好、可靠性高的优点,又能更高效、更精准、更迅速地执行复杂的浮点运算,使其在通信系统的应用中具有更大的优势。

在双CPU 冗余通信系统中,实现两个CPU 之间的实时切换是保证通信系统可靠性的重要条件。设计选用CPLD 进行双CPU 之间的仲裁切换,由CPLD 实时监控两个CPU 的状态,并通过逻辑判断实现双CPU 之间的实时切换。本文选用Altera 公司MAX Ⅱ系列的EPM1270T144C5N 型号芯片,该芯片具有116 个通用I/O 管脚,支持3.3 V 直流供电,具有编程灵活、集成度高、适用范围广等优点,而且可以多次反复擦写。

CPLD 在切换CPU 时,备份CPU 需要获取主CPU运行时储存的信息数据,因此需要外接一个存储器SRAM 来储存CPU 的实时运算数据,使系统在切换CPU 时能保证数据信息的完整,进一步提高通信系统数据传输的可靠性。本文的SRAM芯片选用ISSI公司的IS61LV25616AL 芯片,这款芯片具有256 KB 的容量,容量大,读/写速度高,而且能恒常保持其储存的数据,有效保障了通信系统的数据安全。

如图3所示,系统的通信接口模块主要包括三部分:

1)以太网网络通信接口模块,主要实现双CPU 与控制中心之间的双向通信,选用W5500 作为以太网控制器,分别与两个CPU 连接,构成双以太网冗余通信网络。两个以太网控制器同时接收控制中心的数据信息,将其中一条通道设置为工作网口,完成数据信息的传输,当出现网络连接超时或网口中断等故障时,系统切换至另一备份网口继续稳定传输数据信息,并上报故障,保证数据传输的可靠性以及实时性。

2)RS 232 总线,用于实现双CPU 与上位机之间的交互数据通信,主要用于读取故障数据,监测系统的运行状况、监控相关设备的使用寿命以及更新相关软件,当系统出现故障时,可以利用该通信接口将系统故障信息传送到上位机,实时实现人机交互。

3)RS 422 通信接口模块,主要用于实现主机与下位机之间的外部总线通信,下位机接收并响应控制中心和上位机发送的数据信息和指令,完成相应工作。

3 CPLD 的逻辑仲裁

本文选用CPLD 作为通信系统的仲裁模块主要是因为其能够实时响应通信系统中上位机的需求,减少总线切换的反应时间,具有良好的稳定性。在通信系统中,CPLD 与两个CPU 通过I/O 管脚直接连接并互相驱动,接收来自两个CPU 自检、互检的状态信息以及系统的强制接管信号,一旦任意一个CPU 出现问题,CPLD可以迅速做出判断进行仲裁切换,使系统在不丢失通信数据的情况下将总线切换至另一个正常CPU,保证系统通信的实时性和可靠性。

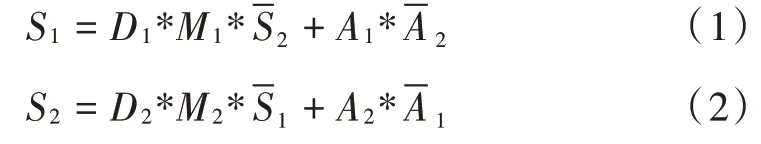

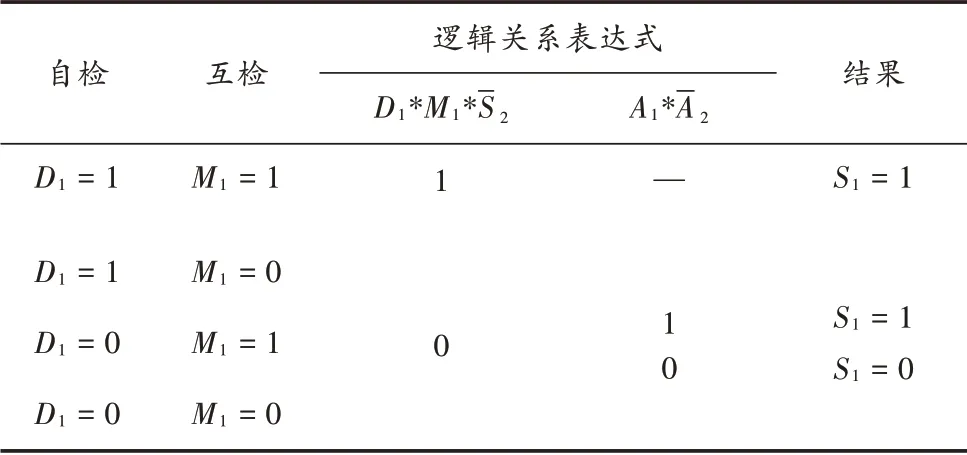

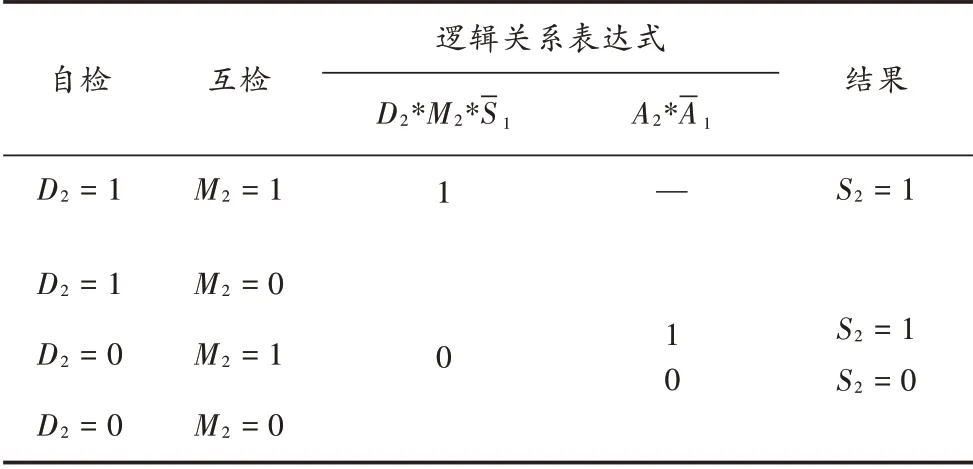

通信系统在工作时,CPLD 根据一定的逻辑完成双CPU 之间的仲裁,其逻辑关系表达式为:

表1 CPU1 为主CPU 时的仲裁切换结果

表2 CPU2 为主CPU 时的仲裁切换结果

同理,当CPU2 为主CPU 时,CPLD 以同样的逻辑完成总线的切换。CPLD 的仲裁结果如表2 所示,将S作为逻辑仲裁的结果传输给对应的CPU,完成双CPU 之间的实时切换。

CPLD 的工作原理图如图4 所示,CPLD 与两个CPU直接通过管脚连接,接收由CPU 上报的状态信息以及处理的数据信息。首先,CPLD 根据逻辑关系表达式判断两个CPU 的工作状况,并将仲裁结果传输给对应的CPU;另外,CPLD 对CPU 的读/写操作进行分析并通时钟驱动完成CPU 对SRAM 的读/写操作,实时获取并储存CPU 的工作数据,保证数据的完整性。在CPU 对SRAM 进 行读/写操作时,CPLD 对SRAM 的操作主要有读/写控制、数据的存/取以及读/写地址的产生,双CPU通过CPLD 向SRAM 写入或者读取数据,极大地提高了通信系统数据采集以及提取的速度。

图4 CPLD 的工作原理图

4 通信系统的电路设计

为了避免外界信号对系统通信造成干扰,在以太网控制器W5500 与外部设备之间添加网口变压器以实现信号的电平耦合,避免由信号电平波动导致的系统稳定性问题,通信系统的电路设计如图5 所示。

图5 交互通信系统电路设计图

在通信过程中,CPU 通过CPLD 对SRAM 进行读/写操作时,首先要读取对应侧CPLD 的BUSY 管脚电平,当BUSY 为高电平时,对应侧的CPU 执行对SRAM 的读/写操作,该CPU 向CPLD 写入使能控制信号,但只有当使能信号OE 和BUSY 信号均为低电平时该侧CPU 才能对SRAM 进行读/写操作。当信号R/W 为低电平时,CPU 向SRAM 写入数据;当信号R/W 为高电平时,CPU 从SRAM读取数据。CPU 在对SRAM 进行读/写操作时,通过CPLD 的数据总线和地址总线发送16 位数据和16 位地址,由CPLD 完成地址和数据转换,进而操作SRAM。

由上述分析可知,BUSY 管脚是确保两个CPU 与SRAM 在通信时不发生冲突的关键,本文中两个CPU 通过CPLD 对SRAM 进行读/写操作时,可能存在两种情况:两个CPU 在不同时刻对SRAM 进行读/写操作;两个CPU 同时对SRAM 进行读/写操作。在第一种情况下,两个CPU 分别在不同的时间对SRAM 进行操作,不会影响系统的工作;而在第二种情况下,两个CPU 同时对SRAM 进行读/写操作时,可能会由于数据的争用造成冲突,此时CPLD 根据两个CPU 读/写操作指令到达的先后进行竞争仲裁,将先发出指令的CPU 的BUSY 管脚置为高电平,并将另一个CPU 的BUSY 管脚强制拉低,直到先发出指令的CPU 完成相应操作后,再将另一个CPU的BUSY 管脚拉高,完成其未完成的操作。通过这种竞争机制,CPLD 可以确保正确执行两个CPU 对SRAM 的读/写操作,保证了通信系统信息数据传输的可靠性。

5 结 论

本文对如何提高通信系统的可靠性进行了研究,提出了新型的双CPU 冗余技术,并且构建了基于CPLD 的双CPU 冗余通信系统。系统采用CPLD 作为双CPU 之间的仲裁模块,CPLD 稳定可靠、反应迅速,能准确实现双CPU 之间的总线切换。同时,系统采用SRAM 对通信系统中双CPU 的工作数据进行备份,使双CPU 可以通过CPLD 对SRAM 进行读/写操作,保证双CPU 在互相切换后仍能准确获取对方之前运行的工作数据,确保系统连续稳定可靠地运行,实现信息数据的实时交互。该通信系统能稳定有效地提高通信可靠性,适用于各种工业场所,在日常的电力通信、条件苛刻的航天航空通信以及复杂工作环境的舰船通信等通信领域中都具有非常高的应用价值。当然,在信息技术不断发展的当下,优化通信系统的性能仍有很多的发展空间,通信系统正在向速度更快、效率更高、通信范围更广的方向不断进步。