漫谈苹果M1全系列:半导体新时代!

2022-06-08林亦

林亦

在2022年的春季发布会上,苹果公司发布了M1系列芯片的新成员——M1 Ultra。一直讲究命名独创性的苹果,这回跟三星的Ultra手机&平板系列撞了个结结实实。当然三星也没错过这个机会,不到一个小时就发了条推特说自己赢了,现在全世界都知道三星的运营部门上班时间看苹果发布会了。

说完这个小插曲咱们回到正题,M1 Ultra是一张意义深远的芯片,对苹果乃至整个半导体产业,都是如此。虽然大部分人用不上这张芯片,但这不影响我们对它台前幕后的故事感兴趣。

對苹果来说,这标志着第一代M系列芯片全部发布完毕。这一点在发布会上,得到了苹果负责硬件工程的高级副总裁John Ternus的确认。作为最后也是最强大的一张M1,M1 Ultra走在了半导体产业先进封装这个新方向的前列。对整个半导体产业来说,这也是一张有里程碑意义的芯片,率先为我们勾勒出了摩尔定律2.0时代的轮廓。

关于半导体新时代,我们先从M1 Ultra芯片谈起。这张芯片的特点是由两块M1 Max缝合出来的,M1 Ultra最大能达到20个CPU核心、64个GPU核心,128GB统一内存。对比M1 Max的参数刚好翻倍。

芯片缝合参数翻倍这种事,以前也有,比如05、06年英特尔的奔腾D处理器,然而实际效果欠佳——虽然两晶片被缝合在一起,但两者却不能通信。大家小时候应该都经历过这种情况,就是跟好朋友闹翻了,谁也不跟谁讲话,所有事呢,都得靠一个共同的朋友来传话。当年奔腾D的两个晶片就是同样的情况,所以虽然参数翻倍了,但性能提升主要还是靠用户对自己进行心理暗示,我称之为“精神超频”。因此这种方案不仅没有发展成主流,反而衍生出了“胶水双核”这么个梗,专指这类骗自己的多晶片方案。所以今天常见的多核处理器、都是把CPU核心刻在同一块晶片上,保证核心与核心之间的高速通信。

不过这次两块M1 Max缝合出来的M1 Ultra又有了新变化,关键就是UltraFusion。UItraFusion的通信速度达到了2.5TB/s,而且这个TB的B是大写的、不是小写的。笔者十多年间收集的影视资源也就区区4个T,UltraFusion不到两秒就能给传完,这个速度是PCIe4.0 x16插槽的78倍、入门级M1统一内存的36倍。M1 Max的内存通信速度达到了400 GB/s,不到UltraFusion的1/6。实际上M1 Ultra自己的内存通信速度是800 GB/s,也不到UltraFusion的1/3。

这是一个值得讨论的话题。首先M1 Ultra内存800 GB/s这个数,是很说明问题的。MI Ultra里面有两个M1 Max,每个M1 Max的内存带宽是400 GB/s,假如上半部分一个CPU核心同时访问所有内存,它享受的带宽就应该是上面这块M1 Max的带宽、加上下半部分的内存被UltraFusion卡了一下之后剩下来的带宽。现在这个800 GB/s刚好是上下两部分加起来,400加400,所以这就侧面反映出UltraFusion的带宽确实是给够了,至少没耽误内存。

有国外博主提出另一种看法,他认为根据这个数字来说,应该还会有一款两块M1 Ultra两层叠起来的设计,总共四块M1 Max缝合到一起,原因就是UltraFusion这个2.5 TB/s的带宽是M1 Ultra内存800GB/s的三倍多,给两个M1 Ultra用也是足够的。

对此,笔者持怀疑态度。按苹果在发布会上的描述,M1 Ultra在软件实际调用的时候会被识别为一块单一芯片,不需要程序员额外注明任务怎么分配,两块M1 Max自己就能协调好,对外表现是一整块20核的处理器,而不是两块10核处理器。实际跑分结果也印证了苹果的这个说法。M1 Max的Geekbench多核跑分是1.2万,M1 Ultra是2.4万,实际性能上确实是翻倍效果。想要把融合效果做到这种程度,两张M1 Max之间的信号传输就不能只限于内存了。CPU、GPU、缓存,还有神经引擎、媒体引擎这些元件之间应该都要有信号传输,到极限情况M1 Ultra一起工作,2.5 TB/s可能也只是刚好够用而已,所以我对这套通过带宽反推新芯片结构的逻辑表示怀疑,但大家可以对四块M1 Max缝合这个事留个印象。

言归正传,回到M1 UItra本身。上文我们提到M1 UItra里两块M1 Max,可谓珠联壁合,宛若一体。再回看更早英特尔奔腾D的“胶水双核”,理念还是一个理念,但实际效果是天壤之别。从目前的Geekbench跑分来看,M1 Ultra超过了Mac Pro中英特尔的28核至强处理器,甚至接近了AMD 64核的线程撕裂者3990X,同时功耗却比这两者低得多。那为什么同样的理念,今天的效果却突飞猛进?答案就是半导体产业这些年的一个新动向:先进封装。

什么是封装呢?半导体工艺流程分前段制程和后段制程。顾名思义,前段就是前面在晶圆上刻晶片、做电路的这些步骤,后段就是后面的步骤,封装就属于后段制程。这一步简单点讲,就是把前段制程里切下来的小晶片装到电路板上,扣上盖子,做成咱们日常能买到的比如英特尔i5、i7这些CPU。

这几年封装技术进步特别快,举个侧面的例子,就是“CPU”这个名词都开始有歧义了,像以前我们说CPU指的就是这一整块芯片,但是现在随着封装技术的进步,芯片这个盖子里集成的功能越来越多,CPU反而只是其中的一块了。尤其是像M1 Ultra,你说CPU具体指M1 Max里的CPU区域,是M1 Max,还是整个M1 Ultra呢?

这就是人类语言追不上技术的一个典型例子,也侧面反映了先进封装技术对半导体产业的颠覆性。先进封装,就是把今天复杂、大型的晶片封成一块芯片的技术,也是半导体产业的一条新赛道。长期以来,半导体产业的主要精力都在前段制程上,通过缩小晶片上的晶体管尺寸来提高晶片性能,但晶体管越小,再往下缩面临的物理限制就越多,难度可以说是指数级上升。当年英特尔就是因为低估了问题的难度,高估了自己的能力,在加号地狱里无限轮回,最终导致了苹果的跑路,如今换了一个技术出身的CEO才终于又有了起色。不过从整个半导体产业来看,晶体管尺寸的物理限制是所有人都要面对的难题。无论英特尔、台积电还是三星,近年的制程升级节奏都在变慢。所以前段卡住,发力后段做先进封装,就成了行业的共识。除了今天的这张M1 Ultra,英特尔也在做EMIB和Foveros 3D封装,而AMD的3D封装芯片、R7 5800X3D将在4月20日面世。

M1 Ultra芯片由两块M1 Max强强合体,给你磅礴动力,处理各种庞大艰巨的工作。运行复杂的粒子模拟,或是执行过去难以实现的大型三维场景渲染,现在都得心应手。M1 Ultra的媒体处理引擎资源也同样翻倍,可支持同时播放多达18条8K ProRes 422视频流,这在个人电脑上是极具颠覆性的。

其实摩尔定律本来就是说每18个月芯片上的晶体管数目翻一番,就没提过晶体管尺寸。今天的晶片已经很小很小了,借助先进封装技术扩大芯片面积,从而增加晶体管数目,同样可以维持摩尔定律,支撑半导体产业的发展,因为不同于长期以来缩小晶体管尺寸的思路,所以封装产业将这个新方向称作是摩尔定律的2.0阶段,今天的M1UItra,包括即将开卖的AMD 5800X3D,都在证明这个方向的可行性,而这两款产品的制造企业其实是同一家,就是台积电,包括摩尔定律2.0这个概念,也是台积电的工程人员提出来的。

讲先进封装,一定绕不开台积电。台积电在先进封装技术上是起步最早的企业之一,这背后也有段故事。

2011年,重新执掌台积电刚刚两年的张忠谋,宣布要做先进封装。2011年的时候英特尔还在32纳米制程上,那时提到先进封装大家想到的也是拉胯的胶水双核,所以老先生的这句话很多人想不通。封测大厂日月光的财务长董宏思就评价说“这种技术只会被用在极少数的特定高端产品中,影响有限”。当时在台积电负责先进封装研发的人,是今天的台积电副总经理余振华,他就回击说“先进封装这个技术,以后所有高阶产品都会用,市场很大”,说自此专注于先进封装的研发。

到了2013年,FPGA厂商赛灵思成为了台积电先进封装技术的第一个客户。一年之后,英特尔正式进入14纳米制程,开启了一场以加号为主题的奇妙旅程,制程困局的倒计时,正式开始。今天回头来看,张忠谋可谓慧眼如炬。再看看苹果的M1 Ultra、AMD的5800X3D,余振华当年的话也在逐渐成为现实。

话说回来,台积电的先进封装在M1 Ultra的制造上,到底干了啥?根据当年电子时报的报道,UltraFusion使用的大概率是台积电的CoWoS-S技术,也有可能是成本更低的InFO-LSI、类似英特尔的EMIB。这里我们以CoWoS为例解释一下,这几个技术主要区别是材料的用量不一样,相应地成本也不一样,但原理相通。CoWoS的全名是chip 0n Wafer on Substrate,名字很直白,描述的就是这么个三层结构,Chip是晶片,在最上面,Wafer指的是硅介质层,夹在中间,英文叫Silicon Interposer。蘋果发布会上Johny Srouji讲UltraFusion的时候,左一个interposer、右一个inte rposer,说的就是夹在中间的这个硅介质层。最下面一层就是Substrate——载板,通俗点叫电路板。这三层里面最创新的是中间这层。它的作用是缩体积、降功耗。硅介质层和晶片的材料一样都是硅,内部电路结构可以比下面的电路板更细、更密,电路宽度可以做到1/10甚至更细。M1 Ultra有大量的功能电路和通信电路,晶片放不下的就可以由中间这个介质层来分担,但如果没有介质层,让电路板来分担,那体积和功耗都要成倍增加,因为电路板的线太粗了。形象点说,如果没有这种先进封装技术,那MI Ultra根本放不进Mac Studi0这个小盒里,如果硬要把这些信号通道刻在电路板上,M1 Ultra的尺寸可能比苹果的27寸显示器还大,耗电量可能超过家用空调和冰箱的用电之和。所以这就是台积电先进封装的意义,因此M1 Ultra才成为了可能。

那么问题来了,即使是有台积电的先进封装,但M1 Ultra上面有1140亿个晶体管,为了让两块M1Max珠联璧合,宛若一体,这些晶体管之间又要有无比复杂的通信电路。若干晶体管和电路的故障是大概率事件,就算有冗余设计,像M1 UItra这么复杂的晶片,良品率也有限。生产成本这么高、再加上新芯片巨大的设计成本,售价必然高不可攀。不过不用担心,咱们看看苹果的CEO是谁?Tim Cook,工业工程出身,资源优化大师。1998年3月临危受命来到苹果,七个月后把产品库存量从30天减少到6天,到1999年又进一步减少到惊人的两天。“库存克星”这个称号对库克是一种羞辱,因为有库存才需要克星,而库克的目标是“没有库存”。当年库克在lBM学的就是JIT制造模式,“Just in Time”,需要多少做多少,不留库存。有这样一个领导者,你可以相信苹果能解决M1 Ultra的成本问题。

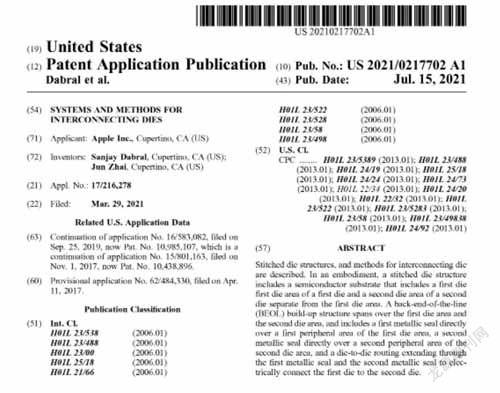

接下来,咱们就来讲一讲苹果的20210217702A1号专利,全名是“晶片连接的系统与方法”,这里面有UltraFusion的结构描述,也有上文提到的成本问题的解决思路,更有下一代大型芯片的预先规划,我称之为“苹果自研芯片全面剧透”专利。

这篇专利公开于2021年7月15日,相比M1 Ultra的发布提前了半年多。芯片投产前就做专利保护是很正常的,但为什么提前这么多?听我慢慢道来。

首先关于ultraFusion的具体结构方面,专利书第31段、第37段,第42到48段,以及结尾部分的20条专利主张都进行了描述。首先两块M1 Max晶片在分界线两边各有一条信号缓冲带,M1 Max上需要通信的元件,比如CPU、GPU、内存都与信号缓冲带连接,信号从这些元件走到缓冲带,再经由缓冲带上的通道穿过分界线,到达对面的缓冲带,最后到达目标元件。

搞清楚结构,我们就可以讲前面的成本问题了。根据专利书上的描述,芯片生产过程中,工厂会先在晶圆上排满M1Max晶片,然后逐一检查,把相邻且内部电路完好的晶片找出来,在这些晶片之间搭建信号通道、填充电介质,连上之后,一对对儿切下来,M1 Ultra就成了。剩下的晶片,如果只是负责跨晶片通信的电路有问题,就单独切下来,当M1 Max来卖,这就是为什么去年的M1 Max芯片下面,全都额外有一条信号缓冲带,这个并没有什么用的结构,我称之为“库克的微笑”。这也是为什么苹果去年七月就要公开专利,因为10月M1 Max就要发布了,生产M1 Max其实就是在生产M1 Ultra,所以要提前保护。不过降成本这条路走到这儿还没完,M1 Max的结构也挺复杂,万一也做坏了呢?没关系,库克也做了预案。如果生产缺陷是在下半部分,横着来一刀,它就变M1 Pro了,照样卖。这些都是很优秀的成本控制设计。这样一来呢,良品率变高,生产成本和设计成本却被摊薄了。再进一步,设计成本其实还能往下摊。虽然M1 Pro没法直接砍成M1,但是像CPU、GPU核心、雷电控制器等,很多元件都可以在M1上原樣复用,每卖出去一张M1,同样也是在分摊整个M系列芯片的设计成本。如此来看,我们可以理解为M1 Ultra才是整个系列的主角,其余产品都是为了它的诞生而服务。顺着这个思路,iPad Pro和iPad Alr为什么上M1芯片,也就终于有答案了。我之前觉得苹果上M1是想用iPad取代电脑,现在我觉着我判断错了,至少是因果关系反了。对苹果来说,只要iPad散热压得住,上M1之后都是好事。性能强、有噱头、有关注度,还能分摊M系列芯片的设计成本,而且还省了设计iPad芯片的成本,所以对苹果来说没什么理由不给iPad上M1。让iPad取代电脑,最多就是有了上M1这个打算之后的想法,或者干脆就没有这个想法。照这个思路,未来基础版iPad、甚至iPad mini,只要散热压得住,很可能都会上M系列芯片。再往外推一步呢,苹果的长期目标,很可能就是把手机、平板和电脑的芯片都统一到同一个芯片产品线上,理论上来说这样可以最大程度地减少浪费,还能增加生产线运营的灵活性。比如说某段时间iPad Air的销量远高于MacBook Air,那就把给MacBook准备的M1芯片,调给iPad Air,这种极致的优化,刚好是今天的苹果CEO库克最擅长也最喜欢的事。假如真有那么一天,苹果就会变成一个运营效率极高的科技工业体,能不能做出改变世界的产品要靠运气,但每年的财报绝对会非常好看。那时,苹果就真的是库克的苹果了。

这件事到底有没有可能呢?我们再回到苹果的专利书。专利书的本质就是通过公开来换取保护,把你想做的和有可能会做的事都写上去,写得越全,获得的专利保护才能越全面。苹果这篇专利书的第39段(找原文标记)介绍了这套晶片缝合方案的潜力。这套方案并不局限于两块晶片,任何数量都可以,比如三块、四块。晶片的缝合边也不必局限于一条,最多可以给四条边都加上信号缓冲带,这样四条边都可以与其他晶片缝合。这就是明确说了四块晶片合体是可行的,而且合体方式不是叠放、也不是通过插槽中转,而是多边缝合。有了这个信息,首先可以确认M1 Max不可能四块合体了,因为M1 Max上只有一条信号缓冲带,如果想四块晶片合体,按照苹果专利书里的方案,每块晶片至少要有两条缓冲带,明显M1 Max就不行了。然后就是刚才说的手机、平板、电脑全线芯片统一,这事的可能性是存在的。今天手机跟电脑芯片的性能差距已经没那么悬殊了,未来手机用单晶片,平板和轻薄本用双晶片,专业本和台式机用四晶片,好像也不是不可以,那就真成摩尔定律2.0了,但是在这种缝合方案的成本降下来之前,这都只是猜想。

今天我们从M1 Ultra的参数谈起,先追溯了老一代封装方案“胶水双核”的黑历史,然后就M1 Ultra的实际性能结合半导体产业的现状,讲了封装技术的“老树开新花”,那讲到了先进封装,就不能不提台积电和摩尔定律2.0,以及台积电先进封装如何让M1 Ultra成为了现实。翻阅苹果的UltraFusion专利书,从M1 Ultra的成本控制出发,梳理了M系列全产品线的关系,展望苹果未来,我们一起等待时间验证。