基于SOC的高实时全景拼接技术研究

2022-05-30吴岳

关键词:光电侦察;实时性;全景拼接;SOC

中图法分类号:TP312 文献标识码:A

1引言

在光电侦察领域,全景图像拼接理论、技术和方法一直是研究重点[1~4],在军事、安防等方面具有重大的价值及应用前景。它将同一场景获得的多幅局部图像拼接为一副宽视角的图像[5],解决了单目摄像机不能完整显示广角360°图像的问题,提高了图像信息采集的完整度,增加了关键信息捕获的效率与质量。

然而,现有的全景拼接方案大都采用软件处理的方式[6],该方式存在存储图像分辨率不足、实时性得不到保障[7~8]、拼接延迟较大、无法在拼接的基础上引入其他复杂的图像处理算法等局限,为了满足上述需求,提出并设计一种高实时性、灵活的软硬件解决方案变得愈发迫切。

本文提出并实现的全景拼接技术依托ZynqUltraScale为硬件设计平台,采用FPGA逻辑与高速DDR4存储模块完成了图像处理及复杂计算,延迟低,可实现任意拼接图像大小以及任意拼接行列数的切换功能,具备广阔的应用前景。

2全景拼接技术系统框架

本文所述全景拼接技术采用“UltraScale+ZU9EG”逻辑芯片为主处理器,图像输入采用1K高清紅外相机,并以HDMI作为拼接显示,硬件平台如图1所示。

通过片上FPGA系统开发,完成了全景拼接技术部署,分为三大部分,即图像预处理模块、全景拼接模块和HDMI显示模块。

图像预处理模块完成电子变倍功能,级实现1K图像的缩放显示,采用的双线性插值方法极大保留原始图像的真实性;拼接模块对datamover IP核进行控制配置,分割图像读写DDR的时序,保证拼接视频的输出连续性。HDMI输出模块运用GTH IP核结合FPGA逻辑实现serdes总线协议编码输出,节约了硬件系统资源与空间。

3设计与实现

3.1预处理模块

为实现不同拼接子单元大小的改变,本文采用双线性插值算法对1K红外图像进行电子变倍预处理,该算法充分利用源图中虚拟点四周的四个像素点来共同决定目标图形中的一个像素值,实现在不损失视场前提下的图像尺寸变化。其实现公式如下:

srcX=(dstX+0.5)×(srcwidth/dstwidth)-0.5(1)

srcY=(dstY+0.5)×(srcheight/dstheight)-0.5(2)

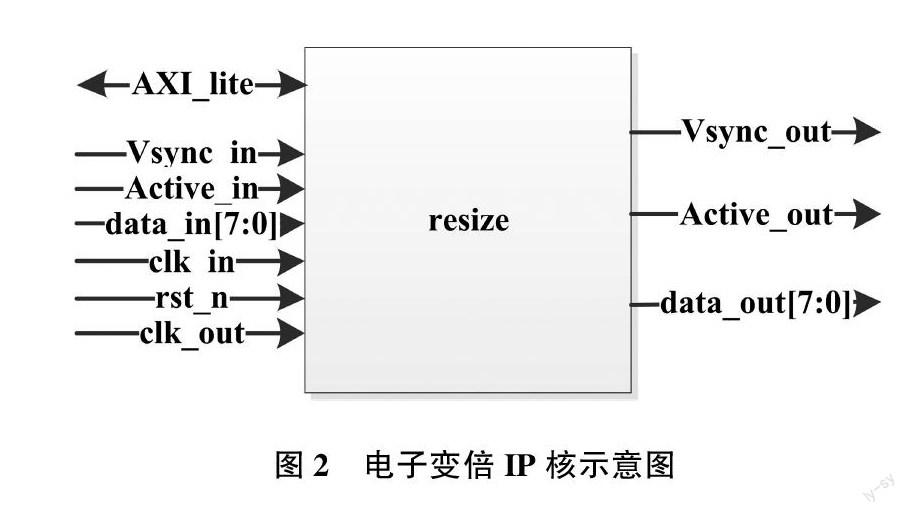

其中,srcX为源像素所在列数;srcY为源像素所在行数;dstX为目的像素所在列数;dstY为目的像素所在行数;srcwidth为源图像列;srcheight为源图像行;dstwidth为缩放后图像总列;dstheight为缩放后图像总行。最后通过verilog编码完成该算法的通用SOCIP核,其对外接口如图2所示。

接口类型采用主流图像接口帧有效vs、数据有效de、以及数据data,并通过AXI_lite总线实现ARM核的缩放倍数调度,确定srcwidth、dstwidth、srcheight、dstheight数值,实现动态缩放预处理功能。

3.2全景拼接模块

传统图像拼接技术利用上位机完成各视场子图像的拼接排序,延迟较高且GPU资源使用较高,无法满足日益增长的图像拼接需求。本文依托XILINX独有的AXI总线及交互协议,采用多级缓存、同步数据复位、高分时复用以及巧妙地信号握手、格式重组,完成了全景拼接算法的模块化设计,逻辑框架如图3所示。每个帧周期完成当前帧与上一帧图像的存储,并通过乒乓操作将上一帧的内容输出显示,从视觉上实现了动态拼接过程的刷新显示,与传统软件方式实现的全景拼接相比,实时性有显著提升。

其具体实现分为输入与输出两块,利用FPGA的并行计算特点,通过乒乓读写实现逐帧刷新。以2行2列拼接显示为例,第一步:线程一将帧号为1的行列图像输入FIFO2单元,通过FIFO2进行相应的跨时钟域操作并将图像行列参数转换为DDR_CTR所需的AXI_STREAM总线,并通过datamover IP核传递至ARM端DDR4进行缓存,将其存储于输入存储空间的“1”位置,该IP核实现对少量外设寄存器的控制以及PL中断PS,PS调用中断服务程序响应。实现PL主动通知PS,协调工作,传输连续大量的数据到DDR4存储器,控制逻辑在PL部分实现,由于片内没有足够的BLOCK RAM所以在DDR3存储芯里面共享一部分空间作为显存,PL独立于处理器主动地从DDR4存储器取数并显示。

以实现一个S2MM写为例,将1帧图像缓存于FIFO1单元以便后续乒乓输入;线程二将FIFO2中预存的上一帧(这里命名为“4”)通过与帧1同样的方式转换为AXI_STREAM总线,并通过datamoverIP核传递至ARM端DDR4进行缓存,将其存储于输入存储空间的“4”位置;线程三将输出存储空间2?2的图片以FIFO3为媒介输出。第二步:将帧号为2的行列图像依照帧号为1的图像进行流水并将其存储于步骤一中的输出缓存空间,此时读出步骤一中的输入缓存空间,视觉效果即可实现帧号1到帧号2图像的依次输出。步骤三、步骤四等后续的操作模仿以上两步进行乒乓操作,即可实现全景拼接程序流水。

3.3HDMI解码模块

传统的HDMI输出采用硬件编码芯片实现数字信号的并串转换,本文充分利用了异构SOC的并行计算特点,采用FPGA逻辑实现了HDMI差分格式数据输出,该IP核充分利用“UltraScale+”芯片特有的GTH IP核,该IP实现了并行数据信号的串行化编码,结合HDMI输出格式编写相关控制逻辑,至此完成了该通用SOCIP核的设计。

4测试结果与分析

采用该技术实现的6行24列快速周视(单幅133?220)全景效果图如图4所示。

经测试,设计的拼接延迟为1帧、实现了全景态势信息的动态更新,并可通过上方控制指令完成拼接模式切换、起停拼接任务等调度。

5结论

本文介绍了一种基于SOC硬件平台的全景拼接技术,该技术实现包括图像预处理、全景拼接、HDMI显示等模块,并依次详述了各模块的功能和实现;充分利用处理器独有的AXI交互总线,完成了ARM端DDR与FPGA之间的高速通信与拼接显示读写调度。该技术不仅可支持任意拼接图像大小,还可支持任意行列、实时拼接360°全景视频的功能,图像延迟仅1帧,具备优异的灵活性。

该研究成果可快速移植应用于SOC架构的其他硬件平台,具有较高的设计参考和应用推广价值。

作者简介:

吴岳(1994—),硕士,助理工程师,研究方向:FPGA图像。