基于NOC 系统的资源节点设计

2022-05-30全钊锋刘超娜

全钊锋 刘超娜*

(1、广西民族师范学院,广西 崇左 532200 2、广西职业技术学院,广西 南宁 530100)

1 概述

随着技术的不断更新,集成芯片的精密度越来越高,为了解决芯片内部各个模块的通信,提高芯片的性能,提出了片上系统(SOC,System On Chip)以及片上网络系统(NOC,Network On Chip)两种解决方案。这两种方案大大地提高了芯片内部的通信性能,降低通信的时延,为集成电路芯片往密度更大,规模更广,精确度更高的方向发展。片上网络是为了解决片上系统传统总线结构以及全局异步局部同步问题而提出的一种系统设计方法[1],片上网络是专门用于芯片内部互连的通信网络,它借鉴了计算机网络中分组交换的通信方法,可以根据应用灵活地采用多种网络拓扑结构互连片上系统或者IP 核[2]。为了更好地探索和研究NOC 系统的性能,本设计以2D-Mesh 网络结构为基础[3],结合FPGA 载体,设计3x3 网络拓扑结构的NOC 系统资源节点,为研究和测试NOC 系统性能提高良好的硬件平台基础。

2 NOC 系统

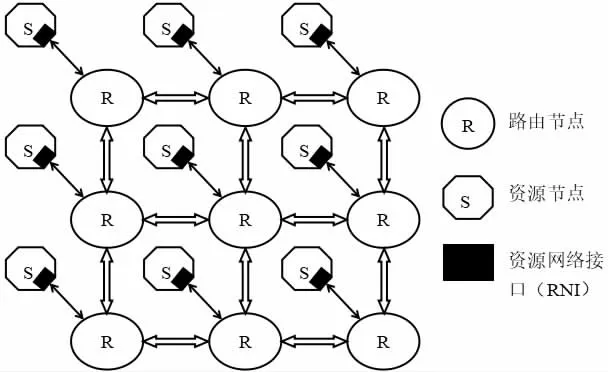

NOC 系统主要是由路由节点、资源节点、资源网络接口组成[4-5],如图1 所描述的是3x3 的2D-Mesh 网络拓扑结构,该拓扑结构中路由节点的构建主要是由FPGA利用Verilog 硬件编程语言设计而成,它的功能主要是负责路由节点之间的通信、路由节点与资源节点之间的通信以及路由决策等。而资源网络接口是介于路由节点与资源节点之间的通信接口[6],它的构建主要也是采取FPGA 内部的逻辑单元通过硬件编程语言设计而成,它的功能主要是资源节点的信息通过资源网络接口编码、打包、转换等操作发送到近端的路由节点,近端的路由节点根据路由信息查询路由决策表,发送到目的路由节点,目的路由节点通过资源网络接口进行解码、解包、转换等操作后发送到目的资源节点,从而完成数据的发送和接收,资源网络接口在期间起到搭建路由节点和资源节点的桥梁作用。资源节点是具有一定功能的完整的系统,比如高速数据采集系统、图像采集系统、以太网传输系统、温度控制系统等。NOC 系统中路由节点和资源网络接口是保障传输数据的高速有效,而NOC 系统功能的主要体现在资源节点上,资源节点处理的对象和处理的能力直接影响整个NOC 系统的功能。

图1 基于2D-Mesh 的3x3 拓扑结构

3 资源节点设计

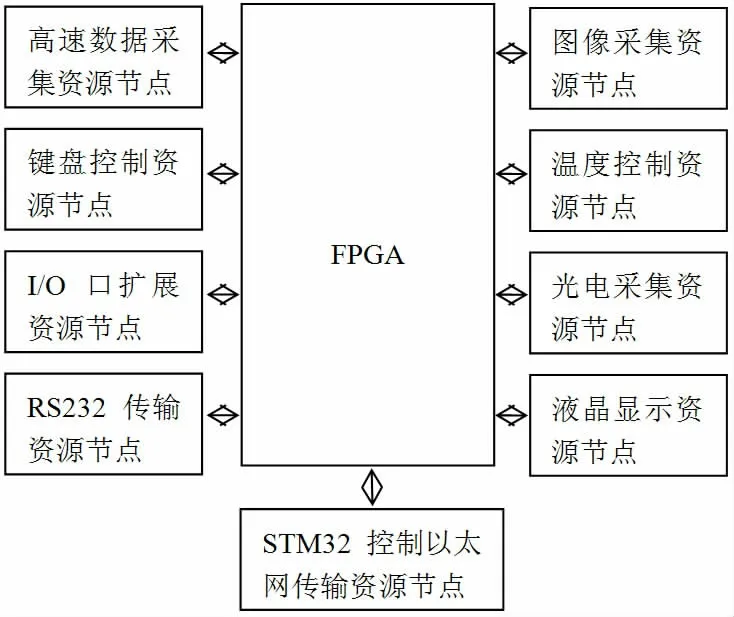

本设计的3X3 的2D-Mesh 拓扑结构的NOC 系统,路由节点与资源网络接口是由FPGA 内部逻辑单元通过Verilog 硬件编程语言设计而成,而涉及到的9 个资源节点如图2 所示,分别是高速数据采集系统、图像采集系统、以太网传输系统、温度控制系统、RS232 传输系统、光电采集系统、液晶显示系统、键盘控制系统和I/O 口扩展模块。以下以高速数据采集系统和以太网传输系统为例设计NOC 系统的资源节点。

图2 NOC 系统框图

3.1 高速数据采集资源节点设计

本设计的高速数据采集系统资源节点主要是用于测量输入信号频率在10KHz-10MHz,峰峰值在1vpp-2vpp,阻抗是50Ω 的高频正弦波模拟信号,然后将采样的数据经过资源节点接口的读取、打包成路由节点可识别传输的数据帧,然后路由节点根据数据帧中的目的地址等信息查询路由决策表完成数据的传输。如图3所示,高速数据采集资源节点主要由前置信号处理电路和采集模拟信号ADC 转换芯片组成。前置信号处理电路采用的是变压器耦合的方式将P1/P2 输入的模拟信号完整地输入到ADC 芯片的模拟输入通道中,而且为了匹配输入信号的阻抗,P1/P2 输入的信号接50Ω 到地;在ADC 转换电路设计中,选用的是转换速率65MSPS,双核14 位AD9248 高速ADC 芯片,采用双通道差分电路的方式将输入的信号输入到模拟的通道中,更好地获取信号的完整性。AD9248 芯片的模拟通道只能采样正电压的模拟信号,故在输入信号中通过AVDD 电源串联电阻分压的方式对输入的信号进行抬高电压。

图3 高速数据采集电路

在高速数据采集资源节点设计中,AD9248 模数转换芯片的控制引脚直接与FPGA 内部设计的资源网络接口相连,对ADC 进行采样、转换等操作是由资源网络接口完成,完成的同时将采集的数据打包、编码发送到近端路由节点。采样过程:高速数据采集资源节点的近端路由节点接收到远端路由节点传输过来的数据采集命令,近端路由节点将命令传输到资源网络接口,资源网络接口解码分析命令,对AD9248 进行采样,完成采样的数据原路打包传输到远端路由节点。

3.2 以太网资源节点设计

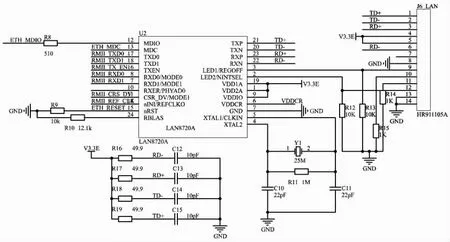

NOC 系统与外界建立联系,通信设备必不可少,常见的通信总线设备有USB 串口、I2C 总线、CAN 总线、SPI总线等,基于物联网时代的到来,设计了NOC 系统的以太网资源节点。该以太网资源节点主要采用了LAN8720A 的芯片,配置以一定的外围电路,就能完成100M的传输速率。如图4 所示,HR911105A 是采取封装RJ45 的连接器,从LAN8720A 管脚4、5 接入外部时钟晶振 25M,RD-、RD+、TD-、TD+ 传 输 数 据 的 引 脚,LAN8720A 本身是一款低功耗的器件,输出带负载能力较差,为了使输出RD-、RD+、TD-、TD+的数据信号增强,直接与R16、R17、R18、R29 电阻上拉到电源端。

图4 以太网电路

在以太网资源节点设计中,考虑到嵌入式芯片STM32 在实时监控方面的优势,而且STM32 的可以支持移植UC/OS II 系统,采用STM32 作为LAN8720A 以太网芯片的主控器件。在控制上采取UC/OS II 实时多任务操作系统,通过修改UC/OS II 上的函数,配置相应的任务优先级、任务堆栈等完成对LAN8720A 的实时控制。NOC 系统通过以太网资源节点访问外界的过程:以太网资源节点的近端路由节点接收到远端路由节点传输过来的访问命令,近端路由节点将命令传输到资源网络接口,资源网络接口解码分析命令,对外界符合以太网协议的信息通过STM32 控制LAN8720A 芯片读取数据后,STM32 将读取的数据传输到近端的资源网络接口,资源网络接口将信息打包、编码原路传输到远端路由节点。

4 资源节点测试结果

NOC 系统的测试主要包括链路测试、路由节点测试和资源节点测试,本文在已经完成链路测试和路由节点测试的基础上主要对NOC 系统中高速数据采集资源节点和以太网资源节点功能进行测试,测试的过程如图5 所示,上位机通过以太网发送高速数据采集命令,在FPGA 内部固定的路由路径传输(实线箭头为路径)到高速数据采集资源节点,采集数据后原路传输数据经以太网资源节点到上位机。

图5 测试指示图

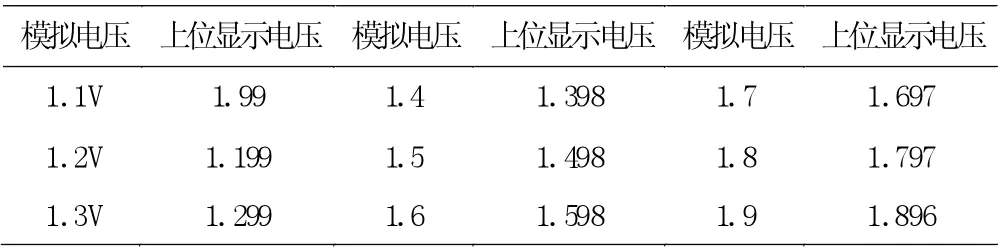

如表1 所示,设置高速数据采集资源节点采集的是多个不同的模拟直流电压,通过与传输到上位机的电压对比,以太网传输数据正确,功能正常。

表1 以太网资源节点传输数据功能测试结果

如图6 所示,右侧正弦波是进入高速数据采集资源节点模拟通道A 或者B 的实测波形,左侧是AD9248 模数转换芯片采集后经路由节点传输回以太网资源节点,以太网资源节点上抛到上位机的绘制的图形,两者波形无明显失真,上位机绘制的波形与实测的波形基本吻合。

图6 实测波形与上位机显示波形对比图

如表2 是改变输入正弦波的频率、峰峰值,利用上位机监测到的数据,通过实测与上位机测量的数据两者比较峰峰值、频率,误差β=(实测- 上位机监测)/实测,可见误差很小,高速采集数据资源节点功能正常。

表2 上位机监测输入正弦波形的参数

5 结论

本文以FPGA 为核心器件实现了以3x3 2D-Mesh网络拓扑结构的NOC 系统的资源节点设计,通过对资源节点功能测试表明该设计完成了预期的设计效果,为今后研究NOC 路由算法和测试NOC 系统故障提供了良好的硬件平台。