基于FPGA的FMCW雷达收发机系统

2022-05-28张景璐岳增龙

王 硕 张景璐 岳增龙

(北京电子科技职业学院 电信工程学院,北京 100176)

雷达是利用电磁波探测目标的电子装备。雷达发射的电磁波照射目标并接收回波,由此发现目标并测定目标的位置、运动方向、速度及其他特性。近年来,随着物联网技术的高速发展,进行近距离目标探测的小型毫米波雷达的应用得到了极大拓展[1]。调频 连 续 波(Frequency Modulated Continuous Wave,FMCW)雷达具有辐射功率小、测距测速精度高、设备相对简单以及易于实现固化设计等优点,被广泛应用于汽车防撞[2]、行人检测[3]以及手势识别等领域。

本文采用24 GHz雷达模块搭建了一个信号收发机硬件系统,能够实现信号发射、接收、中频调理与基带信号提取,并配合后端上位机软件实现了测距功能。该系统由自行设计的中频电路模块和基带处理现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)开发板组成,具有低成本、灵活可配置以及实现高效的优点。

1 系统构成

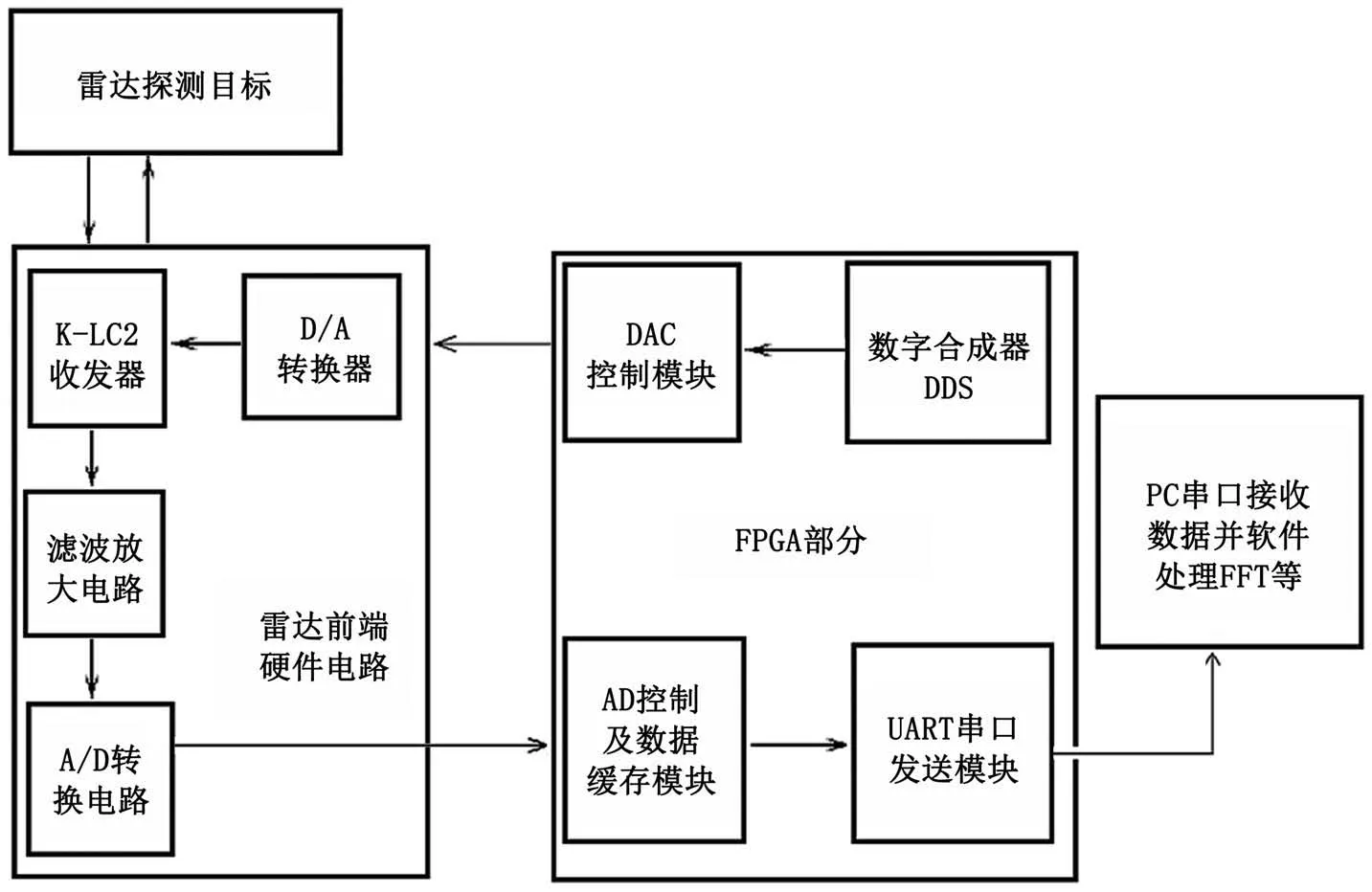

系统采用Rfbeam公司的24 GHz低成本雷达收发器K-LC2,集成了射频的收发功能与混频,可以在锯齿波或三角波的调制方式下发射连续波。回波信号在模块内部与发射信号通过混频器的混频,得到带有目标距离信息的正交差频信号(I/Q)。原始中频信号由于带有泄露的调制信号和外部的高频噪声干扰,需要经过带通滤波。此外,为了增大信号的信噪比,充分利用模/数转换器(Analog-to-Digital Converter,ADC)的动态范围,要对信号进行放大。在经过A/D模数转换为数字信号后,采用Xilinx公司的Nexys4开发板对信号进行采集,并送入个人计算机(Personal Computer,PC)提取距离信息,同时FPGA还配合数模转换器(Digital Analog Converter,DAC)产生调制信号。系统构成和工作流程如图1所示。

2 雷达前端硬件电路设计

2.1 中频信号调理电路参数

中频调理电路的设计是雷达系统设计中的关键部分。它的性能好坏直接影响基带信号处理的效果,从而对整个系统的精度产生了较大影响。雷达模块输出的差频信号中混有泄露的调制信号和高频噪声干扰[4],如果不能滤除,有可能会因为总的信号过大而在放大后产生饱和失真,或者是有用信号太弱而被噪声淹没。中频电路需要尽可能滤除这些噪声的干扰和放大有用信号,所以设计的中频电路核心是一个带有一定增益的高低通滤波器[3]。

图1 系统构成

为方便计算中频频率,选择1 kHz为调制信号频率。利用距离测算公式,可得出中频信号频率范围fb:

式中:R为目标距离;fM为调制信号带宽;TM为调制周期,取1 ms;c为光速。将相关数值代入式(1),可得距离R在0.5~10 m范围时的频率范围fb为5.3~106.6 kHz。

2.2 中频信号调理电路设计

根据结果可以确定中频的主要参数。高通滤波器的截止频率为6 kHz,是调制信号频率的6倍,可以有效消除调制信号的泄露,同时衰减近距离目标回波的信号幅度,避免溢出。低通滤波器截止频率采用120 kHz,略高于频率范围上限,以保证目标距离较远、信号较弱时有用信号尽量不被衰减,同时滤除系统中混有的高频干扰[5]。因此,滤波器采用高通和低通级联的形式,增益在60 dB左右,负载阻抗为1 kΩ左右,通带为6~120 kHz。

3 FPGA部分设计

3.1 FPGA设计结构

FPGA设计分为调制信号产生和信号采集两个主要模块。调制信号产生模块包括直接数字合成器(Direct Digital Synthesizer,DDS)模块、波形存储ROM、预置频率和相位字的寄存器以及控制频率字的按键。信号采集模块包括AD控制模块、采样缓存器、通用异步收发(Universal Asynchronous Receiver/Transmitter,UART)模块、波特率设置按键以及使能模块。另外,FPGA中还有系统时钟控制模块,将系统时钟分频提供的不同频率分配给各个模块。

3.2 调制信号产生模块

发射信号的调制三角波信号由FPGA产生的数字信号经过数模转换(DAC)产生。

由FMCW雷达测距原理可知,探测目标越近,所需调制信号频率越高。探测远距离目标(30~100 m)时,通常采用100~200 Hz的调制频率;探测近距离目标(10~20 m)时,通常采用500~1 000 Hz的调制频率。因此,为了扩大收发机的适用范围,希望调制信号的参数可以根据实际应用场景灵活调节。

为了满足不同距离的应用需要,设计采用可以改变调制信号频率和相位的数字合成器(DDS)作为发射信号的产生装置。DDS主要由基准时钟源、相位累加器、相位调制器、存储了波形数据的ROM表以及D/A转换器构成。其中,DDS的主要模块除DAC外,均由FPGA编写硬件实现。

3.3 信号采集模块

信号采集部分主要是搭建一个数据通路,将ADC采样到的数据发送到PC,因此采用了一个简单的结构。AD9280芯片的数字信号接口是由8根数据传输线和1根时钟线组成的专用通信接口。在FPGA中编写一个与ADC通信的接口电路,并将接收的ADC数据暂存在片内的缓存器中。FPGA与PC之间通过串口通信,在ISE软件中调用UART模块,从缓存器中读取数据并发送至PC。将串口的波特率设置为115 200 Baud,以保证在不丢包的情况下最快发送数据。

4 功能测试

将测试长50 cm、宽50 cm、厚约2 cm的正方形硬纸板作为雷达的检测目标,放在距离雷达天线0.5 m处,正对贴片天线阵列静置,以保证最大面积被电磁波照射。清除在电磁波照射范围内的其他物体,以减少背景噪声源。给系统上电,同时启动发射和采集模块,接收并采集回波基带信号。在PC端对串口进行配置,波特率设为115 200 Baud。打开串口接收数据,以十六进制存储于文档。数据采集10 s左右,由于初始化系统工作需要1~2 s,为保证数据的准确性,将5 s之前的数据清除,并将之后的数据每5 000个保存在一个文档中作为原始数据包,依次编号。

用MATLAB软件处理接收的原始数据。因为FMCW雷达测距的实质是对差频信号的频率进行估计,然后利用差频信号和距离之间的线性关系达到测距的目的,所以在采集到的一个数据包中选择两个调制周期内的中频波形数据进行1 024点的快速傅立叶变换(Fast Fourier Transform,FFT),得到的频谱结果如图2所示。可以看出,频率集中在5.5 kHz附近,因此差频信号为5.5 kHz。可以得出,目标距离0.52 m,误差为0.02 m,较好地实现了测距功能。

图2 回波信号频谱图

5 结语

本文采用24 GHz雷达模块,设计了一个三角波FMCW雷达收发机系统。该系统中频处理模块可以完成中频信号的滤波、放大、数模转换、调制信号的模数转换及滤波,基带处理部分则由FPGA和上位机完成。其中,FPGA实现了调制信号的产生和回波基带信号的采集与传输,采用DDS变频设计,可以根据测距范围调整调制信号频率,设计灵活性强,且相比于基于处理器的软件实现方式效率更高。开发的基带信号处理程序,还能够实现目标的距离计算。此外,基于此平台可以开发更加丰富的雷达功能。