基于ZYNQ的高清视频与图形叠加显示技术

2022-05-09连成哲翟东奇蒋沅嵩孙建华李家齐

连成哲,翟东奇,蒋沅嵩,孙建华,李家齐

(华中光电技术研究所-武汉光电国家研究中心,湖北 武汉 430223)

0 引 言

高清视频与图形控制界面的叠加显示技术在很多领域有所应用[1],如直升机的视频监控中,不仅要求实时显示侦察目标的状况,并且需要同时显示直升机在飞行过程中的速度、位置、高度等信息,并提供人机操作控制[2],此时就需要视频图形叠加显示技术。此外,在舰船、海军光电、汽车等领域的显控终端也需要此项技术[3]。

传统的显示与控制系统在有高清视频显示需求时,往往采用专用的图形处理硬件如显卡、GPU或者专用于视频显示的芯片满足高清视频显示的需求[4],显示与控制软件通常部署在工控机中,在桌面操作系统环境下开发和运行人机交互界面。

ZYNQ是Xilinx公司推出的一款可扩展处理平台,其结合了处理器系统(Processing System)以及可编程逻辑(Programmable Logic)两部分,是一款ARM+FPGA的异构芯片,通过AXI数据交互协议进行片内处理器与可编程逻辑的高速互联[5],PS部分支持Linux、VxWorks、μCos等多种嵌入式操作系统,可以很方便地使用图形库提供人机交互界面,同时通过PL部分对图像、视频等进行处理、显示。基于ZYNQ SoC的高清视频与图形界面叠加方案相较于传统方式,将图形采集、人机交互、视频与图形界面叠加、高清视频显示等功能集成在一个芯片上,具有灵活、低功耗、体积小等优势。

基于ZYNQ SoC平台,该文研究了高清视频与图形界面叠加的关键技术,包括Video DMA视频直接内存访问技术、DRM显示子系统技术、DMA-buf内存共享技术等。通过ZYNQ的PS端Linux系统下基于Qt产生图形界面,在PL端进行高清图像的采集、与Qt图形界面进行叠加并通过PL端HDMI接口进行显示输出,采用DRM显示框架对显示设备进行驱动和控制,进行同屏图层切换、多屏互动。

1 基于ZYNQ SoC的高清视频与图形界面叠加显示技术原理

在多个领域都有视频监控的需求,如海军光电显控终端,需要实时采集摄像头传感器的图像数据进行显示,并提供操控界面供用户使用,同时,需要在实时图像上叠加波门、目标信息等图形和文字[6],这需要在保证图像流畅度和清晰度的基础上进行多个显示图层的叠加。

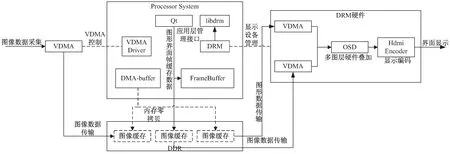

基于ZYNQ SoC的高清视频与图形界面叠加显示技术的原理如图1所示。在数据流中,由PL端资源VDMA进行高清图像的实时采集,并缓存在PS端的DDR中;同时,由Qt图形界面库生成图像上的叠加图形与文字,以及鼠标、按钮等人机交互图形界面,通过帧缓存(FrameBuffer)对图形帧数据进行存储。在显示阶段,通过PL端的两路VDMA分别对图形和图像数据进行搬运,并在PL端的OSD(Video on Screen Display)IP核进行硬件叠加,通过编/解码IP进行HDMI编码后显示输出。而在PS端运行集成了VDMA控制驱动VDMA Driver、内存零拷贝驱动DMA-buf、显示设备管理驱动DRM以及图形库Qt的嵌入式Linux操作系统,并通过libdrm应用接口库对多个图层进行管理。该方案中,高清图像的采集、图像和图形数据的输出以及多图层叠加和显示编码都通过ZYNQ的可编程逻辑部分实现,ARM处理器仅需对PL端初始化与配置即可实现高清图像与人机交互界面的显示,大大减轻了CPU的负载,提高视频的显示帧率与人机交互界面的流畅度。

图1 叠加显示技术原理

2 基于SoC的显示控制相关技术研究

2.1 Video DMA视频直接内存访问

AXI Video Direct Memory Access(VDMA)是一个IP软核,提供了存储器与AXI-Stream视频类型目标外围设备之间的高带宽的直接内存访问。许多视频应用程序都需要帧缓冲区来处理帧速率变更或图像缩放和裁剪,AXI VDMA旨在允许视频接口和AXI接口之间进行高效的高带宽访问[7]。

其结构如图2所示,VDMA分为S2MM写通道和MM2S读通道,分别表示将stream视频流数据通过AXI总线写入内存和将视频数据通过AXI总线从内存中读出,而不需要CPU过多的参与[8],从而降低CPU的开销。

图2 VDMA结构框图

2.2 Direct Rending Manager显示架构

DRM是Linux下的图形渲染架构,是一种对GPU显卡等显示设备的管理和封装技术。DRM驱动架构主要包括以下几个元素:画布(FrameBuffer)、显示控制器(CRTC)、编码器(ENCODER)、连接器(CONNECTOR)和平面(PLANES)[9]。其关系如图3所示。

图3 DRM驱动架构

(1)DRM FrameBuffer。

FrameBuffer是一片用户程序和驱动都能访问的内存的抽象定义,表示了单个图层显示的内容,是与硬件无关的基本元素。DRM显示架构与传统的FrameBuffer显示架构在Linux系统正常加载后都会在设备节点下生成/dev/fb*节点,从而为用户应用提供接口,Linux常用的图形界面库如GTK、Qt等都是基于FrameBuffer接口实现的[10]。

(2)CRTC。

CRTC是CRT Controller的缩写,是扫描输出缓冲的抽象表示,负责读取帧缓冲中的数据。CRTC可以连接多个编码器(ENCODER),用于复制屏幕,并管理各种显示时序参数,是显示器配置的中心环节。

(3)ENCODER。

ENCODER将从CRTC中取得的像素数据转换为目标CONNECTOR支持的格式。

(4)CONNECTOR。

CONNECTOR是与物理显示设备的连接器,如HDMI、DisplayPort、DSI总线。

(5)PLANES。

PLANE代表一个可合成扫描输出缓冲的图像源,也称为硬件图层,用以实现Overlay的应用。

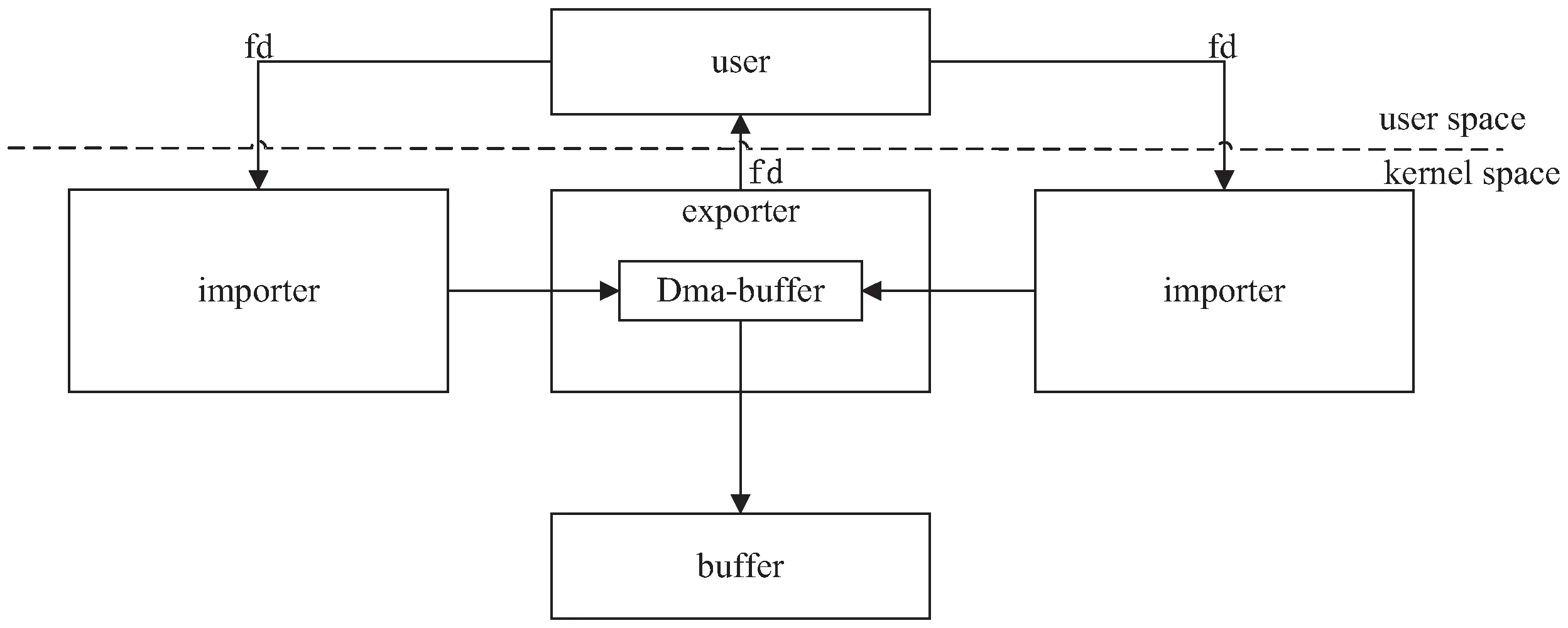

2.3 DMA-buf内存共享技术

高清图像的采集与显示需要将系统中采集到的图像缓存拷贝至显示设备的缓存buffer中,当针对高清图像这种大数据量的应用来说,简单地依靠memcpy会消耗CPU大量的负载,DMA-buf为不同设备、子系统之间进行内存共享提供了统一的机制[11]。典型的DMA-buf应用框图如图4所示。

图4 DMA-buf应用框图

DMA-buf框架下主要有两个角色对象,一个是exporter,相当于buffer缓存的生产者,对应的是importer,即buffer的使用者。各主要功能如下:

Exporter:

实现DMA-buf驱动框架中缓存管理回调函数;

允许其他使用者通过DMA-buf的API来使用共享缓存;

管理共享缓存的分配、包装等细节工作;

决策共享缓存的实际后端内存的来源;

管理scatterlist的迁移工作。

Importer:

是共享缓存的使用者之一;

访问共享缓存的scatterlist,并提供将共享缓存映射到自己地址空间的机制。

3 基于ZYNQ SoC的光电系统显示控制平台设计与实现

3.1 ZYNQ SoC程序设计

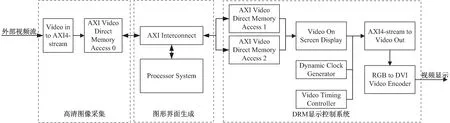

在ZYNQ SoC中,高清图像采集、编码、图形图像叠加与显示在PL端具体实现,PS端则通过图形库生成人机交互界面与叠加图形和文字,并通过AXI总线控制PL端软核对各功能进行配置。基于ZYNQ SoC的高清视频与图形界面叠加显示方案程序设计原理图如图5所示。

对图5所示程序中各功能模块做简单介绍。在高清图像采集中,由Video in to AXI4-stream的IP核将视频图像信息转换为AXI总线类型的视频流,通过AXI Video Direct Memory Access(VDMA0)写入至ARM端的缓存地址中。在图形界面生成模块中,由ARM中Qt图形界面库生成对应的人机交互图形界面和图像的叠加图形与文字,也存储在缓存中。在DRM显示子系统中,由两路VDMA组成DRM系统的多层PLANES,分别从对应缓存区中读取图形和图像数据,并在Video on Screen Display的IP核中进行硬件叠加,并通过HDMI或DVI接口输出显示。

图5 ZYNQ SoC程序设计

3.2 图像采集驱动

图像采集驱动主要通过控制VDMA将视频流数据写入缓存中,驱动流程如图6所示。

图像采集驱动对VDMA的操作在file_operation结构体中实现,通过axicdma_ioctl函数对VDMA支持的配置如表1所示。

图6 图像采集驱动框架 表1 图像采集驱动支持的功能

参数功能RD_S2MM_VSIZE/RD_S2MM_HSIZE/RD_S2MM_FRAME_STRIDE读取S2MM通道行/列/跨度WR_S2MM_VSIZE/WR_S2MM_HSIZE/WR_S2MM_FRAME_STRIDE设置S2MM通道行/列/跨度START_MM2S_TX/STOP_AXIVDMA_TX开始/停止读出图像START_S2MM_RX/STOP_AXIVDMA_RX开始/停止采集图像RD_MM2S_VSIZE/RD_MM2S_HSIZE/RD_MM2S_FRAME_STRIDE读取MM2S通道行/列/跨度WR_MM2S_VSIZE/WR_MM2S_HSIZE/WR_MM2S_FRAME_STRIDE设置MM2S通道行/列/跨度WR_MM2S_WROKMODE/RD_MM2S_WROKMODE设置/读取MM2S通道工作模式WR_S2MM_WROKMODE/RD_S2MM_WROKMODE设置/读取S2MM通道工作模式READ_BUFFER/WRITE_BUFFER读取/写入缓存

3.3 多图层DRM配置

Xilinx为DRM相关的硬件IP核提供了驱动,并集成在了Linux内核中,相关驱动代码在Linux内核目录的drivers/gpu/drm/xilinx路径下。在3.1节SoC程序设计的基础上,需要配置DRM设备树,为Linux正常使用该设备提供支持。

DRM的设备树配置如下,对应2.2节所述,两路VDMA对应DRM显示系统的PLANES,xlnx,encoder-slave节点对应ENCODER,xlnx,connector-type节点对应CONNECTOR。

xilinx_drm {

compatible = "xlnx,drm";

xlnx,vtc = <&v_tc_0>;

xlnx,connector-type = "HDMIA";

xlnx,osd = <&v_osd_0>;

xlnx,encoder-slave = <&hdmi_encoder_0>;

clocks = <&axi_dynclk_0>;

planes {

xlnx,pixel-format = "argb8888";

plane0 {

dmas = <&axi_vdma_1 0>;

dma-names = "axi_vdma_1";

};

plane1 {

dmas = <&axi_vdma_2 0>;

dma-names = "axi_vdma_2";

};

};

};

3.4 嵌入式操作系统与运行环境移植

操作系统与运行环境移植主要包含以下步骤:

操作系统制作:

PetaLinux工具提供在Xilinx处理系统上定制、构建和调配嵌入式 Linux 解决方案所需的所有组件,简化Linux产品的开发[12]。在Linux内核中将3.2节所述的图像采集驱动添加进内核并修改对应的配置文件,同时修改system-user.dtsi设备树文件,对图像采集驱动与DRM显示系统进行配置后,经过编译生成对应的系统镜像。

Qt图形库移植:

Qt是一个开源的跨平台C++图形界面应用程序框架[13],源码可在官网获取,通过赛灵思提供的交叉编译链进行交叉编译后,将对应的库文件拷贝至嵌入式Linux的文件系统中,并配置Qt库的环境变量从而支持Qt程序的运行。

libdrm库移植:

libdrm库是DRM系统的应用层封装,提供图层配置、显示链路配置、显存管理等,通过libdrm,用户可以间接调用DRM系统[14]。libdrm源码可在https://dri.freedesktop.org/libdrm/下载,交叉编译后存储在linux的文件系统中,并配置环境变量从而支持libdrm程序的运行。

3.5 测试用例设计

以光电跟踪设备为例,在光电跟踪设备中,通常有图像传感器接收的真实图像数据并在图像上叠加对应的目标识别信息、波门、目标状态等信息,并提供设备操控界面[15]。在上述设计搭建的显示方案基础上,测试用例通过Qt生成图形数据,与实时采集的高清图像数据进行叠加显示,并动态的配置多个图层的显示关系,程序设计流程如图7所示。

图7 测试程序设计流程

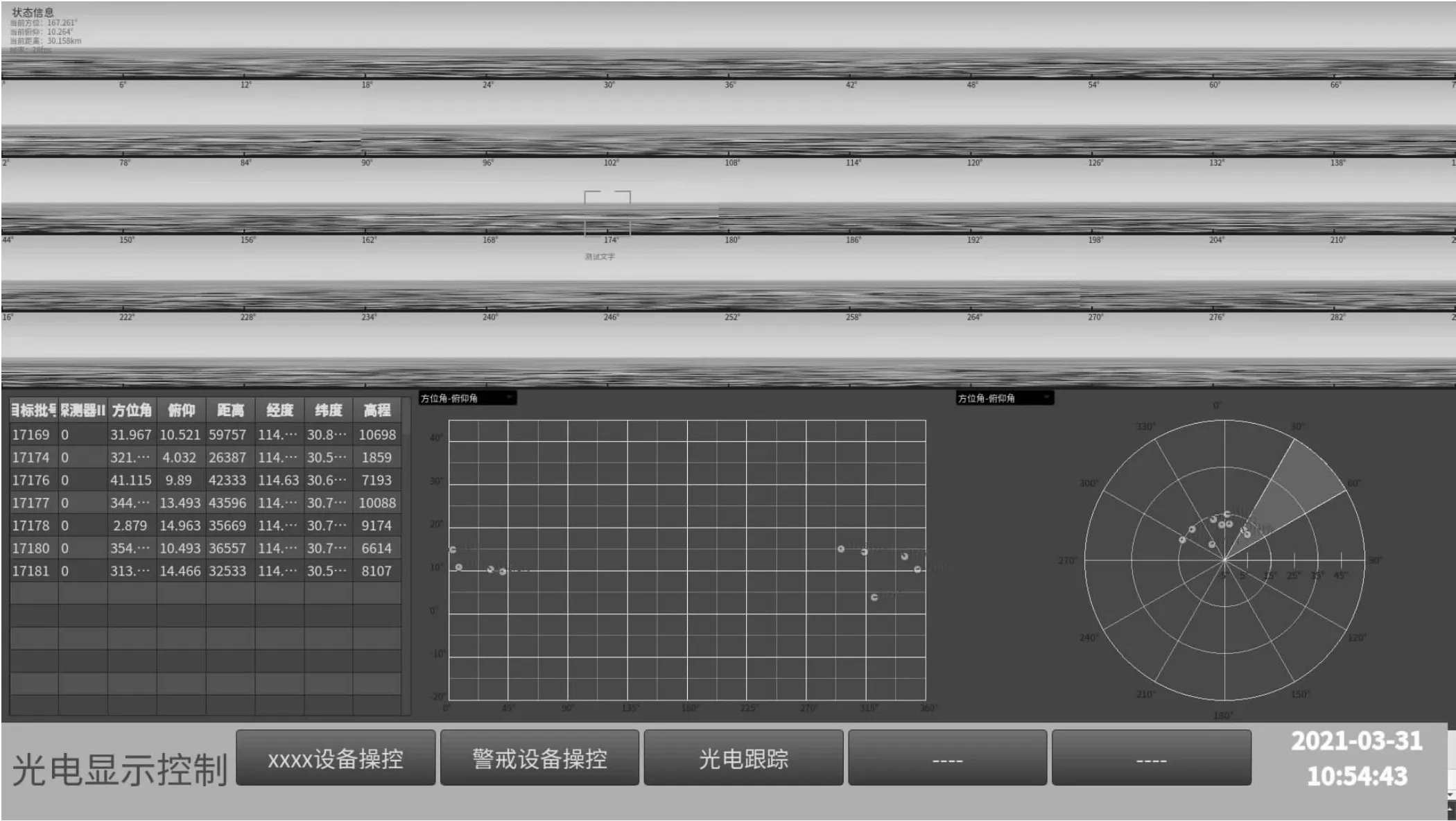

测试程序将采集的图像层作为DRM子系统的plane1,Qt产生的图形界面作为plane0,同时配置plane0作为Overlay叠加图层,并禁用了该图层的全局透明度,从而支持各个像素点透明度的配置,在Qt中将需要显示视频图像的像素部分Alpha通道设置为0。程序运行现场如图8所示。其中,屏幕上半部分1 920*512像素位置底图为实时仿真海面图像数据,标尺与刻度、波门以及状态信息文字等由Qt产生,并将1 920*512位置背景像素的透明度置为0,下半部分同样由Qt产生的人机操控界面,背景不透明。

图8 程序运行现场图

4 结束语

基于ZYNQ SoC提出了一种高清视频与图形界面叠加的显示技术。通过dma-buf机制共享图像采集设备与DRM显示设备之间的图像帧缓存,且图像的采集、图像缓存区至硬件显示接口的数据传输、图像编码都通过SoC的PL端完成,不需要CPU过多的参与,大大减少了CPU的负担,提高了高清图像的显示速率。通过实测,在显示同一分辨率的图像下,通过该叠加方案显示时与通过CPU直接叠加显示时CPU占用率从89%降至13%,帧率从11 fps提升至30 fps左右,满足常用的显示需求。