多核DNN处理器访存指令数据宽度的混合策略

2022-04-29刘元旭张方正王永昶王宝生

刘元旭 张方正 王永昶 王宝生

关键词:DNN处理器;片上网络;访存指令;混合访存数据宽度

1引言

近年来,DNN在计算机视觉、自然语言处理等领域得到了广泛应用。DNN任务具有计算密集和访存密集的特点,通用处理器在处理DNN任务时的性能较为不足。为了提升DNN任务的执行效率,涌现了一批DNN专用处理器,它们大多采用片上网络架构,通过在片上设置大量并行计算单元来加速DNN任务。随着芯片工艺的发展,DNN处理器的计算性能已得到很大提升,但访存性能却一直滞后于计算性能的发展,产生了“内存墙”问题[3]。“内存墙”正成为制约DNN处理器性能提升的一个关键问题。

已有的DNN处理器的访存指令采用的访存数据宽度的访存效率较低。访存数据宽度通常由处理器中的load—store类指令决定。在通用处理器领域特别是RISC架构下,由于其所面临的任务具有不确定性,其load—store指令中数据宽度往往是固定的。然而,DNN任务的数据类型往往是可以预见的,为了加快访存,有必要设计专用的load—store指令以及访存数据宽度。本文提出了一种将定长/变长访存数据宽度进行混合的策略,该策略保留了可变长访存指令的灵活性,同时具有定长访存指令的简洁。实验证明,本文提出的混合访存数据宽度设计策略能够提升DNN数据的访存效率。

2相关工作

DNN任务具有访存密集的特点,在对10种神经网络进行指令统计中发现,访存指令占比达38.00-/0。不同的平台在DNN任务中使用的访存指令各有不同。

通用CPU上通常使用SIMD方式的load-store指令来实现数据级并行[6]。但SIMD指令在访存DNN不同规模数据时不具有灵活性:GPU[7]上对不同类型的内存采用不同的LD/ST指令,这是GPU访存指令的一个特色:一些DNN处理器使用可变长度的向量/矩阵load-store指令来加快访存,其load-store指令操作数宽度可以取在寄存器容量范围内的任意值来适应DNN不同类型数据的变化。但其需要更多不同规格的乘加单元以及数据拆分/合并单元,增加了计算单元硬件实现的复杂度,且在访问不同规模的数据时易造成片上传输资源的浪费。

综合考虑,设计DNN处理器访存指令既要考虑使用可变长的向量/矩阵访存指令的灵活,也应该考虑硬件实现的复杂性。

3load-store指令數据宽度混合策略

DNN训练中的数据按照其在网络层中的作用分为四种,即输入神经元数据、权重数据、偏置数据和输出神经元数据。在数据规模上,权重数据在卷积层表现为规模较小的卷积核,在全连接层则表现为规模较大的全连接权重,后者对访存性能的需求远远大于前者;在连续性上,卷积核具有小尺寸的局部性,可以使用匹配其尺寸的load-store指令将其一次传输,而全连接层的权重则具有大尺寸的连续性,使用具有尽可能大的访存数据宽度来传输,可以减少访存次数。因此,不同数据不宜采用具有同样指令数据宽度的load-store类指令。本文分别针对DNN不同类型数据采用不同的访存数据宽度混合策略。

3.1卷积层数据宽度混合策略

输入数据/输出数据:卷积层输入/输出特征图的访存数据宽度主要取决于特征图的行宽度,若最大数据宽度值不能容纳特征图的一行数据,则采用最大数据宽度值:否则采用的上限值为卷积核的一行数据的最小数据宽度,见式(1)和式(2):

卷积核数据:卷积核数据也可看成是一种特征图数据,其访存数据宽度设计方法参照输入/输出数据。在常见的神经网络中卷积核的行值一般为3/5/7/11且为奇数,因此在设定混合数据宽度时其对应的卷积核最大宽度上限值为64/128/256比特。

偏置数据:为了减少偏置数据访存的访存次数,计算单元每次访存要根据计算任务映射读取尽可能多的偏置数据,因此偏置数据的访存数据宽度主要取决于片上网络每个计算单元可映射的输出特征图的个数P,该值为该层输出特征图个数与片上网络PE个数的比值并向上取整。偏置数据的混合访存数据宽度设定见式(3):

3.2池化层数据宽度混合策略

由于池化层处于两个卷积层之间,因此池化层的输人数据采用其上一卷积层输出数据所采用的访存数据宽度值,输出数据采用其下一卷积层输人数据所采用的访存数据宽度值。池化层无权重数据,因此不做设定。

3.3全连接层数据宽度混合策略

在全连接层应保证单个访存指令可以访问更多的数据。因此,本文统一采用混合数据宽度的最大数据宽度值作为全连接层的输入/权重数据的访存数据宽度:偏置数据量与输出神经元数量相等,对其访存数据宽度的设定采用式(3)。

4实验

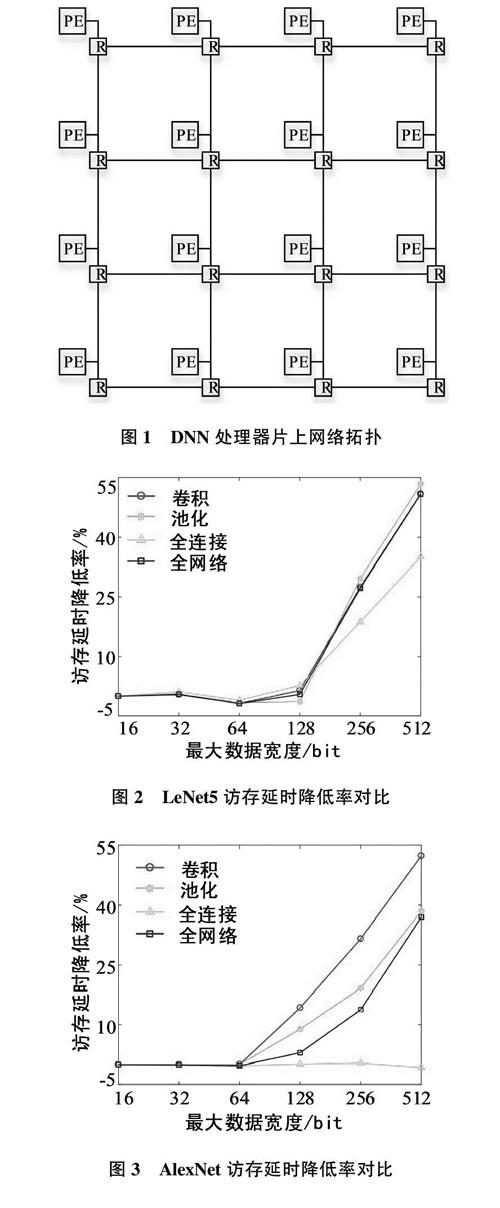

为验证使用混合访存数据宽度对访存延时的降低效果,对LeNet5和AlexNet为实验对象进行了片上网络仿真实验以及分析。实验采用的DNN处理器片上网络架构为典型的4x4拓扑结构(图1),其中R表示路由节点,PE表示计算单元。

图2和图3展示了LeNet5和AlexNet采用混合访存数据宽度比采用传统定长访存数据宽度的访存延时降低率曲线,两个网络的访存延时平均降低15.87%和11.9%,且最大数据宽度越大延时降低率越高。卷积层曲线中,LeNet5以128比特为界,超过128比特后,最大访存数据宽度越大,采用混合访存数据宽度的延时降低效果越明显,这是因为LeNet5中卷积核的尺寸全部为5x5,根据提出的混合策略其访存数据宽度的上限值为128比特:LeNet5池化层曲线可得与卷积层相似结论:在全连接曲线中,LeNet5在采用混合访存数据宽度时较好的情况是在128、256、512比特,在32比特时访存延时略微减少,在64比特时出现反效果。这是因为全连接场景中混合策略主要作用于偏置数据,在32比特和64比特时偏置主要是以16比特混合,两种情形下16比特数据的占比分别为0. 1%、0.2%,占比较低不能有效减少整体数据访存造成的延时。进一步可以看到,LeNet5和AlexNet全网络的曲线与卷积、池化层曲线高度重合,与全连接层曲线差距较大。这说明本文提出的访存指令数据宽度混合策略更有助于减少卷积场景和池化场景的片上传输延时,而对全连接场景的效果不明显。5结束语

本文提出了一种DNN处理器访存指令在访存数据宽度上的混合策略。通过对混合访存数据宽度设计与传统的定长访存数据宽度设计进行片上网络仿真实验,证明在LeNet5和AlexNet训练任务中采用混合访存数据宽度可以获得更低的访存延时,且更适用于对卷积场景进行训练加速。对于目前的DNN而言,卷积层仍处于主要地位,甚至有些DNN除了最后的输出层外已经不含全连接层,因此本文提出的混合策略对大多DNN任务都是有效的。