氢原子钟频率合成器设计

2022-04-28李锡瑞蔡勇

李锡瑞,蔡勇

(中国科学院 上海天文台,上海 200030)

0 引言

氢原子钟是一种利用氢原子能级跃迁产生的电磁波来进行计时的高精度仪器,在大型工程建设和基础科学实验中有着广泛而重要的应用。例如,在守时授时、载人航天、探月工程、空间科学、北斗卫星导航系统中,氢原子钟是支撑项目工程的关键设施;在美国的GP-A(gravity probe-A,重力红移)实验中,氢原子钟直接用于爱因斯坦相对论红移效应的测量;在欧洲的ACES (atomic clock ensemble in space,空间原子钟组)计划中,氢钟也用于进行一些基础物理理论的验证。由于氢原子钟应用领域广泛,工作环境多变,因此,如何提高氢原子钟在不同环境下的“生存能力”,保障氢原子钟稳定性,是氢原子钟发展必须面对的问题[1-5]。

近期在印度巨米波射电望远镜(giant metrewave radio telescope,GMRT)天文台安装自激型氢原子钟。自激型氢原子钟的超低相位噪声和稳定性特征将有助于甚长基线干涉测量技术(very long baseline interferometry,VLBI)观测。并且随着甚高频段信号的观测,对原子钟稳定度提出更高要求。俄罗斯正在开发用于空间天文台“Millimetron”(项目“Spectrum-M”)的更高稳定度的自激型氢原子钟(其目前自激型氢原子钟的长期稳定度指标已经达到2×10-16)。这项任务将使天文学家能够以前所未有的灵敏度和角分辨率观测宇宙[6-9]。

氢原子钟的接收、锁相系统用于接收氢脉泽信号,并把10 MHz晶体振荡器输出信号的相位锁定到氢脉泽输出信号相位上,从而得到所需的输出电平和频率。该系统由晶振、前置放大器、混频器、中频放大器、锁相倍频器、频率综合器、分频器、锁相环路、隔离放大器组成。为了使氢脉泽输出在准确的频率上,我们需要根据对氢脉泽振荡频率的影响因素进行分项修正,对综合器频率进行设置。

我们知道,氢脉泽振荡输出频率fn有如下关系式:

式(1)中,f0为氢原子钟的零场频率,等于1 420 405 751.770 Hz,Δfm为磁场修正,Δfd为二级多普勒修正,Δfw为壁移修正,Δfc为腔失谐修正。

磁场修正:根据测得的Zeeman频率fz,则Δfm=1.416 6×10-9fz2Hz;二级多普勒修正:因为恒温腔的温度T=326 k,则Δfd=-0.063 0 Hz;壁移修正:根据半经典公式,我们可以推算出Δfw=-0.021 4 Hz;腔失谐修正:因为腔体刚进行调谐,则Δfc=0。

由上述各分项修正,根据式(1),可以算出氢脉泽振荡输出频率fn,然后设置综合器读数。例如,根据测得的Zeeman频率,算得磁场修正为Δfm=+0.01 Hz,则fn=1 420 405 751.770 + 0.01 - 0.063 -0.021 4 + 0=1420 405 751.695 6 Hz,然后将综合器设置到51.695 6 Hz即可,这样就能保证氢脉泽输出频率的准确性[10-11]。

本文所研究的是氢原子钟频率综合器的设计模式,如果频率综合器数值异常将直接影响氢原子钟稳定度的指标,因此每台钟设置精准的频率综合器数值至关重要。

1 目前的设计模式

通过AT89C52单片机结合3片串入并出芯片74LS595输出氢原子钟频率综合器所需的频率数值,然后借助一根25芯的连接线接入接收机中的CPLD输入端与接收机输出的20.405 7 MHz混频产生。数字频率综合器的输出频率为405.751 ABCD kHz,A到F数字可以通过智能化面板上综合器按键来调节或修改,调节范围为405 751.000 0~405 751.999 9 Hz,即对氢原子钟输出频率影响的最小分辨率为7×10-14,输出电平为TTL电平,数字综合器的原理框图如图1所示。

图1 目前频率综合器的硬件设计模式

其中数据线传输涉及氢原子钟锁相接收机系统、氢原子钟智能化监控系统间的硬件连接;工作性能方面涉及两大系统内多个芯片的工作状况。这种设计模式电路集成度不高,外围电路繁杂,可靠性方面存在较大隐患。因此本文采用功能更加强大的 FPGA+DDS设计技术,电路集成度更高,外围电路更加简化,降低了设备故障率。

2 基于DDS和FPGA的频率合成器设计

2.1 DDS的原理及其特点

直接数字合成(direct digital synthesis,DDS)是利用数字技术产生模拟波形信号(通常是正弦波形)的一种方法和技术。DDS的基本原理:通过 D/A变换将具有一定规律(通常是正弦函数)产生的随时间连续变化的数字信号转换为相应的模拟波形信号。获得随时间连续变化的数字信号的方法有查表法和寄存器法。为了保证或改善产生的模拟波形信号的技术指标,通常还要采取滤波、放大等一些处理措施[12]。

DDS的主要优点是:

① 极低的相位噪声(优于-144 dBc/Hz)和时钟抖动(< 1 ps)。这是DDS最关键的性能优势。

② 很高的频率、相位控制分辨率。频率分辨率可达10-6Hz,相位分辨率可达0.02°。

③ 输出频率或相位转换快速准确。转换时间通常在ns量级。由于没有跟踪或锁定过程,不会出现输出频率过头或不足的情况。

④ 数字控制接口结构,能够与计算机紧密结合并充分发挥软件灵活、方便的控制功能和作用,可用于频率和相位的远距离控制。

⑤ 数字结构技术克服了由于器件老化或温度改变引起的工作参数漂移,免除了手动调节和调试。

⑥ 低成本、高性能、多功能、高集成度。

2.2 DDS芯片选择

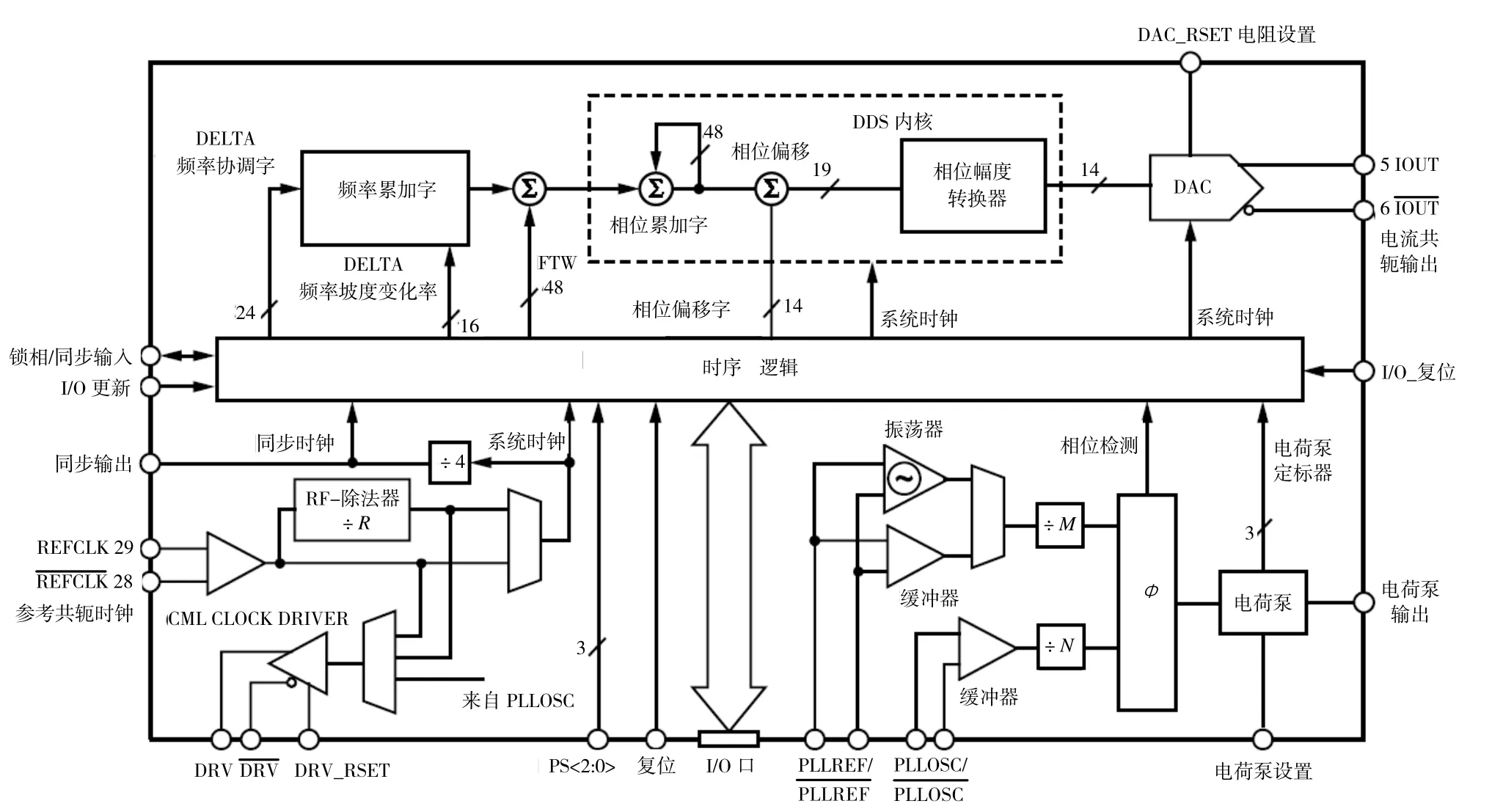

DDS作为一种成熟的技术,现有芯片有多种选择;结合氢原子钟在频率综合器控制精度的要求,在本文设计中我们采用了具有48 bit频率调谐字DDS芯片AD9956,其功能框图如图2所示[13-16]。

图2 DDS芯片AD9956功能框图

2.3 硬件框图和工作原理

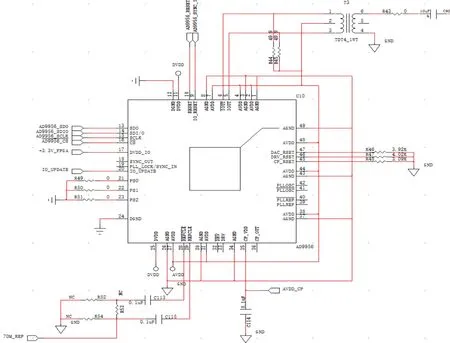

DDS系统由Cyclone II EP2C8T FPGA,DDS芯片AD9956及电源管理单元构成,如图3所示。EP2C8T为系统主控单元,负责控制AD9956和时钟分配器单元。10 MHz时钟可以由外参考提供,也可以由板载TCXO晶体提供,经过时钟分配器进行选择,给FPGA和DDS提供高稳、低相噪时钟源。

图3 AD9956 DDS系统框图

系统设计通过硬件控制AD9956的PS0,PS1,PS2的控制脚,让DDS芯片工作在固定单一频点模式,如图4所示。FPGA通过程序设置向DDS对应寄存器写入频率/相位控制字,并发出IO_UPD命令,DDS则可以输出对应所需要的频率。

图4 AD9956单元电路

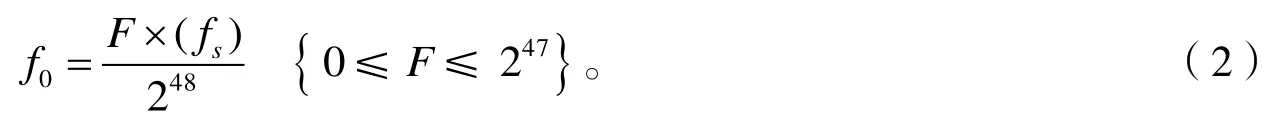

AD9956的输出频率f0可以用式(2)计算:

式(2)中,F为频率控制字。

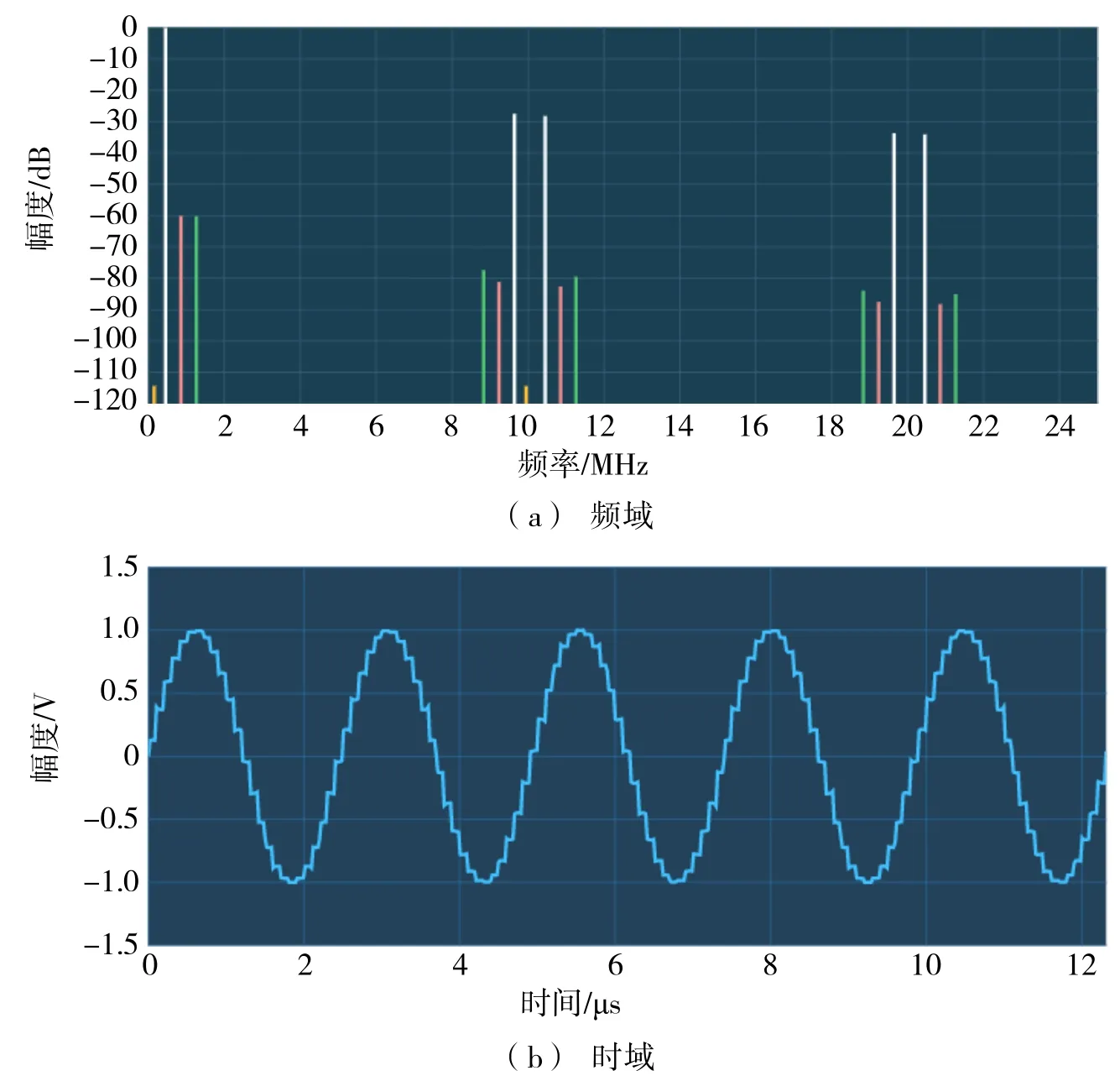

AD9956为电流型差分输出,需要将其转成电压差分信号,再经过ADT1-1WT进行差分转单端输出。图5为DDS输出仿真波形,由图可以看出输出正弦含有较高的谐杂波。

图5 DDS直接输出仿真波形

由于DDS输出信号有一定的谐波和杂散,需要在后端增加低通滤波LPF单元进行抑制。我们系统采用了7阶T形归一化巴特沃斯型低通滤波电路,通过设计计算采用合适的截止频率将谐杂波抑制到合适水平。图6是无外部滤波器时谐杂波情况,而图7则表示增加巴特沃斯型低通滤波器后谐杂波得到了大大改善。

图6 DD输出无外部滤波器时谐杂波含量

图7 外部增加巴特沃斯型低通滤波器后谐杂波含量

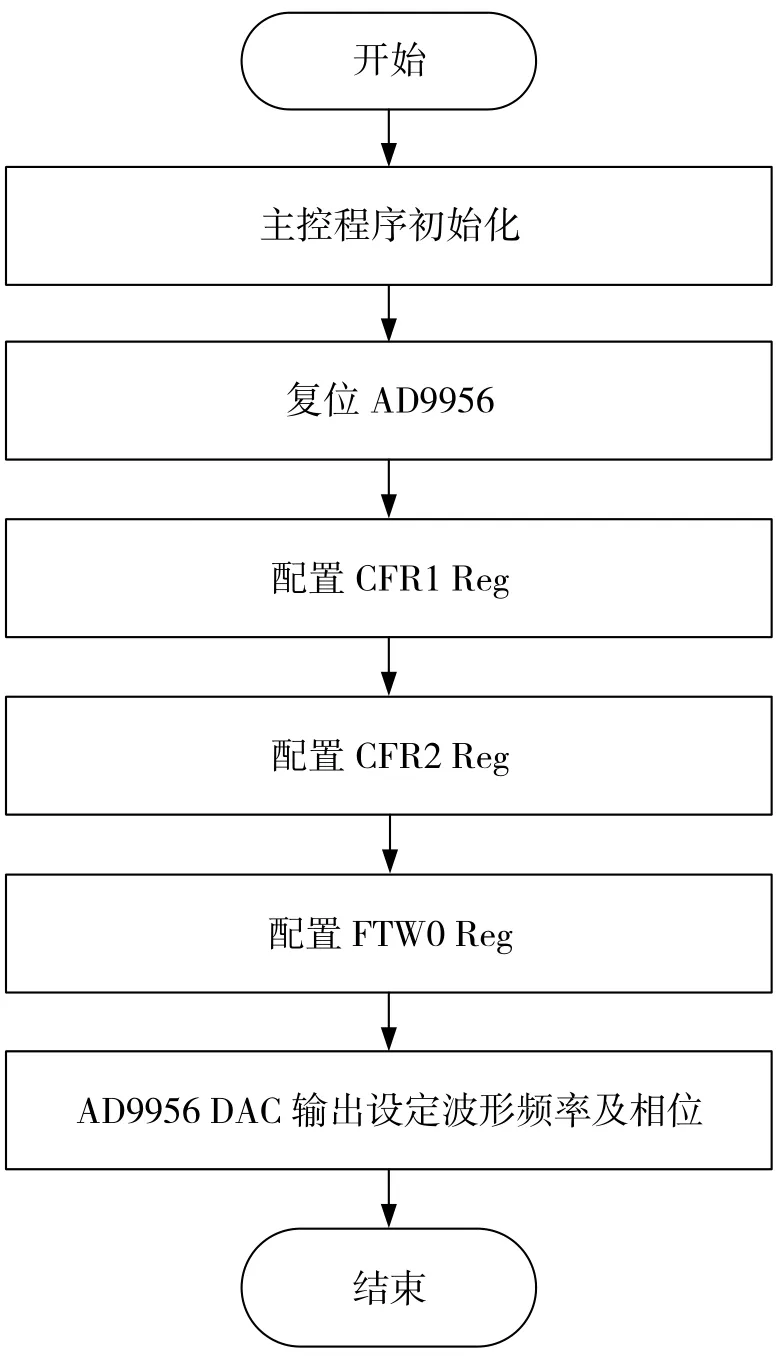

DDS系统配置流程图如图8所示。

图8 AD9956配置流程图

3 研制结果和结论

图9是研制输出氢原子钟频率综合器数值的电路板实物图。

图9 研制输出氢原子钟频率综合器电路板图

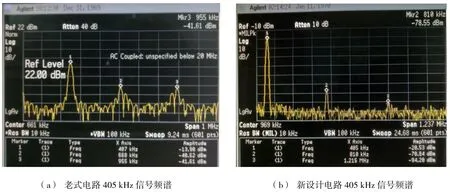

经频谱仪测试,输出频率综合器数值幅度满足氢原子钟锁相,鉴相的要求;而且谐波的幅度较小,电路设计比较理想,与之前设计的频谱对比图如图10所示,同时将装配了新设计405 kHz电路模块的氢钟(H161)与采用老式设计氢钟(H176)进行了稳定度测试,从测试数据来看,装配了新设计模块的氢钟指标好于老式设计模式。新旧405 kHz电路在氢钟稳定度测试结果如图11所示,其中橙色线代表H176氢钟的测试数据;绿色线代表H161氢钟的测试数据。

图10 频谱仪测试结果

4 结语

经测试,所设计氢原子钟频率综合器输出信号的性能满足接收机自动调谐的要求,从氢原子钟的工作状态来看达到了预期的设计要求。与原设计相比较,仅需一块电路板涵盖了原本三块电路设计所达到的设计要求,采用功能更加强大的FPGA设计技术后,电路集成度更高,外围电路更加简化,降低了设备故障率,从而提高了设备的稳定性,可靠性。