基于双端口RNI的3D NoC通信架构设计

2022-04-24胡春雷毕佳佳

胡春雷,毕佳佳,方 杰

(1.合肥工业大学 计算机与信息学院,安徽 合肥 230009;2.安徽职业技术学院 信息工程学院,安徽 合肥 230011)

随着芯片制造工艺进入深亚米时代,芯片上晶体管的集成度急剧增加,单个芯片上可集成几十个甚至上百个知识产权(Intelligent Property,IP)核,基于传统总线通信架构的片上系统(System-on-Chip,SoC)将面临全局时钟同步困难、通信效率、可扩展性等问题,从而IP核之间的通信问题成为学术界研究的热点[1]。为了解决以上问题,片上网络(Network-on-Chip,NoC)作为一种全新的IP核互连架构被提了出来[2]。NoC因具有更小的功耗开销、良好的扩展性和更高的通信吞吐量,被用于解决复杂SoC的核间通信问题。

随着单平面NoC和2D NoC中IP核数量的增加,NoC和2D NoC出现了物理连线过长和信号延迟等问题。而三维集成电路制造工艺的出现,极大地缩短了IP核间的通信链路长度。将二维片上网络架构与三维集成电路工艺有效结合而产生的三维片上网络(Three Dimension Network-on-Chip,3D NoC),以其优良的通信性能、良好的可扩展性等优势被认为是纳米工艺下最有前途的多核SoC通信架构[3-4]。

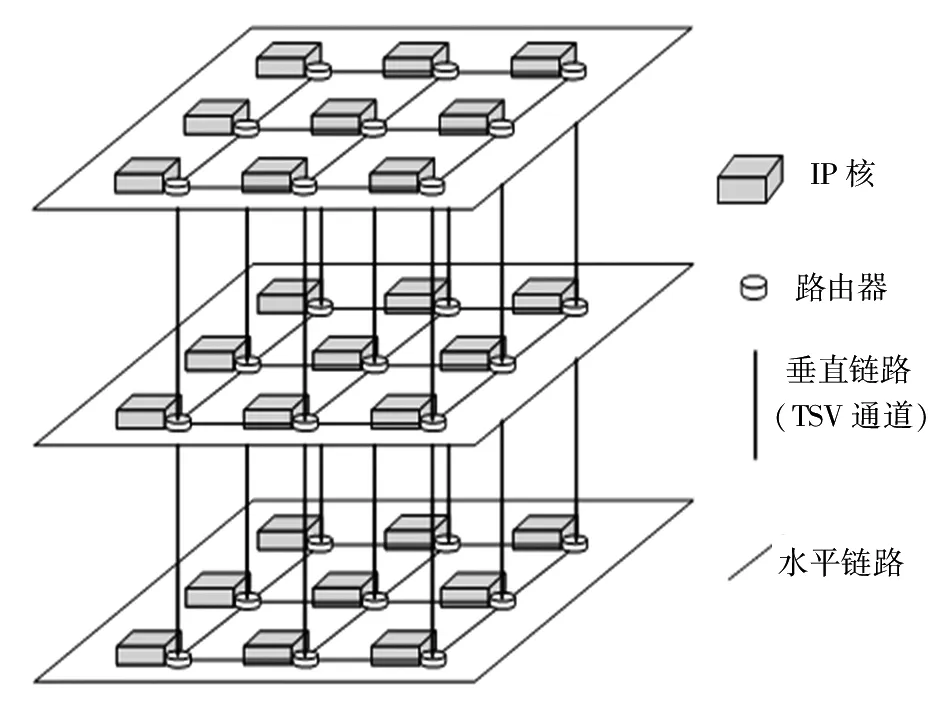

3D NoC结构如图1所示,由IP核、路由器、水平链路、垂直链路、资源网络接口(Resource Network Interface,RNI)5部分组成。3D NoC是在2D NoC基础上进行垂直方向的扩展,这种通信架构大大减小了IP核间的平均跳数,有效提高了片内通信的效率。

图1 3D NoC结构图Fig.1 The structure diagram of 3D NoC

在三维芯片制造工艺中,通常使用硅通孔(Through-Silicon-Via,TSV)技术进行层间互连,即将多个晶片在垂直方向堆叠,有效地缩短IP核间的连线长度,在减少通信时延的同时还可以大大降低通信功耗,很好地满足多核SoC系统对通信效率的要求。但是随着芯片特征尺寸的不断缩小,集成电路密度的急剧增加以及层间互联技术TSV的引入,芯片的可靠性受到一定的影响[5-6]。一方面,受芯片制造工艺水平的限制,芯片在生产过程中将存在更多缺陷;另一方面,芯片在使用过程中,可能受电子迁移、电路老化、电介质击穿等的影响,导致芯片出现故障。

除了纳米工艺下芯片所固有的可靠性问题,3D NoC还存在自身特有的可靠性问题:(1)受芯片制造工艺水平的限制,在TSV制造过程中产生的空隙、位移、表面氧化以及TSV绑定衬垫偏离标定位置等所引起的未对准问题都将带来随机开放性故障,从而导致用于芯片层间互连的TSV存在良品率不高的问题;(2)随着芯片绑定层数以及TSV数目的不断增加,芯片绑定的成品率将急剧下降[7-8];(3)三维芯片所固有的散热问题将加剧芯片出现瞬时故障和永久故障[8]。

3D NoC通信架构主要由资源网络接口、路由器、水平链路、垂直链路4部分组成,负责芯片中众多IP核之间的数据通信。3D NoC通信架构出现故障,将严重影响片内核间的通信性能,甚至导致整个系统瘫痪。3D NoC通信架构的容错成为学术界研究的热点。

1 国内外研究现状

文献[7]针对复杂3D NoC中自适应路由算法存在容错机制不完善与性能较差的问题,提出了一种转向均衡的容错路由算法。该算法将XY、XZ和YZ分为奇偶平面,在行与列上设定不同的禁止转向;设计更为均衡的转向模型,并根据内部链路故障分类设计故障模型;最后设计了全平面一跳预先感知策略的容错路由算法,提高了网络的通信性能与容错能力。针对3D NoC垂直链路故障,文献[9]提出了垂直链路容错方案。针对链路中部分TSV硬件故障导致整个链路不可用的问题,利用欧米伽网络对故障链路中的无故障TSV进行重构配置,将故障链路数据进行分片传输。此方法虽然能够在垂直链路出现部分TSV硬件故障情况下仍然可以进行数据传输,但数据传输效率明显降低。文献[10]针对3D NoC中路由器的交叉开关和输入端口故障,提出了一种容错型路由器。通过对传统3D NoC路由器进行加固设计,增加旁路总线实现对交叉开关的容错;增加冗余输入端口实现对输入端口的容错。在输入端口没故障的情况下,还可以充分利用冗余端口解决网络拥塞问题。文献[11]利用3D NoC路径多样性的特点,提出了一种拥塞感知的容错路由算法。该算法能够指导数据包绕过故障节点或在故障TSV时能够根据拥塞情况选择合适的路径进行数据传输,即容错的同时还能保持能效较优。

综合上述相关文献,可知针对3D NoC通信架构容错研究,主要分为两个方面:一是对通信架构中的垂直链路、水平链路、路由器等重要组件采用冗余设计或者旁路设计进行加固设计,使得这些组件出现故障时,能够利用冗余部件或者旁路机制来屏蔽故障点,从而保证数据包的正常传输;二是设计相应的容错路由算法,当采用一定的容错检查机制检测到3D NoC通信架构中的组件(如路由器、垂直链路、水平链路等)出现故障时,指导数据包绕过故障节点或故障链路,从而进行容错。

以上容错机制只考虑路由器出现故障时,让原本通过该路由器传输的数据包灵活地改变路径,从而绕过故障路由器进行有效传输,忽略了与故障路由器相连的IP核,导致这种IP核成为无法与外界通信的孤立的IP核。针对这一情况,本文提出了基于双端口RNI的3D NoC通信架构设计,即将每一个IP核都与Y维上相邻的两个路由器连接,当两个路由器都可用的情况下,可以根据源、目的节点的位置选择较短的路径进行数据传输,在IP核通信任务繁重时,可以在与之相连的两个路由器间进行通信流量的负载均衡;当只有一个路由器可用时,仍然可以通过它保持与其他IP核的有效通信。

2 基于双端口RNI的三维片上网络通信架构

2.1 双端口RNI的3D NoC通信架构介绍

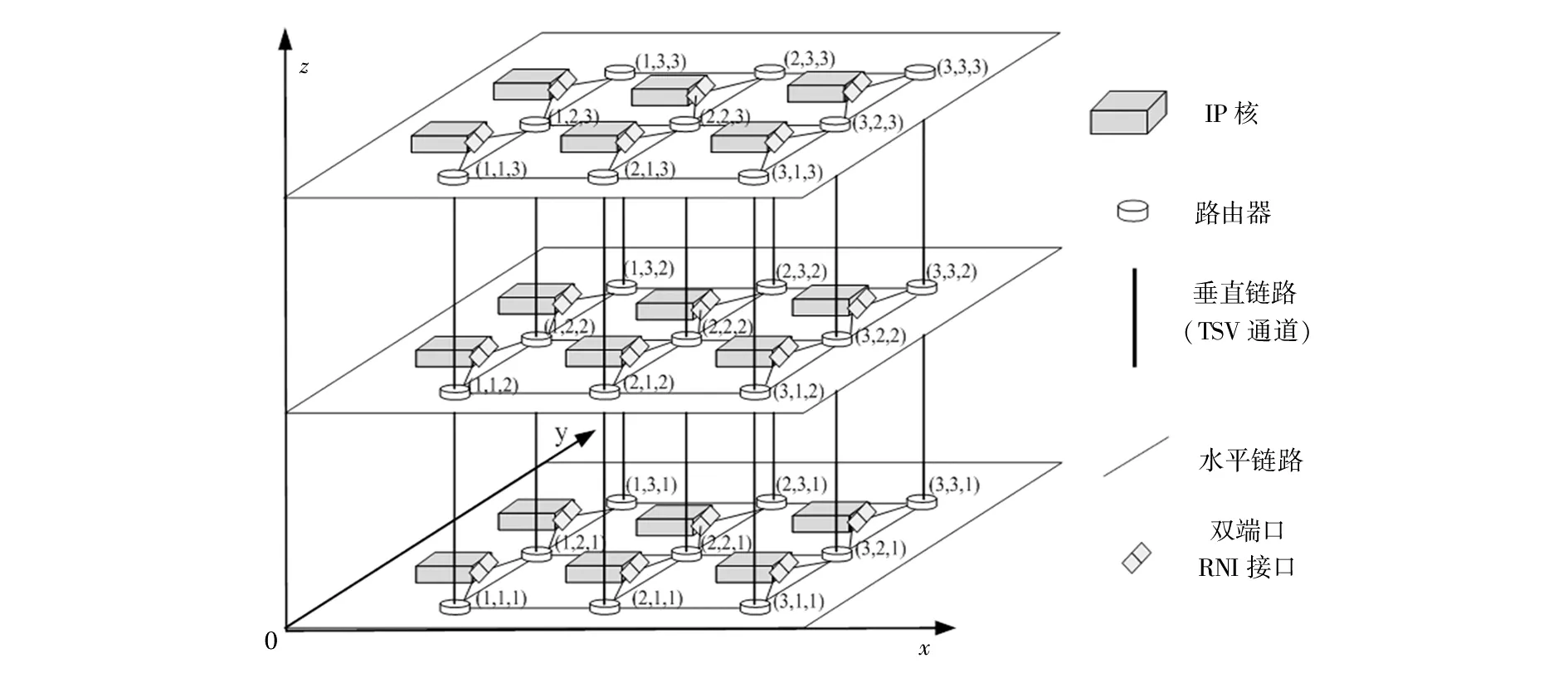

为了便于路由器和IP核的定位,采用三维直角坐标系来表示。基于双端口RNI的3D NoC三维结构如图2所示。图2中路由器的右上角采用三元组(x,y,z)标注它在坐标系中的地址,其中x、y、z分别代表该路由器在三维坐标系中X、Y、Z维的坐标值,如地址(1,2,3)代表该路由器在X、Y、Z维上对应的坐标值分别为1、2、3,即表示处于第3层上X坐标为1、Y坐标为2的路由器。

图2 基于双端口RNI的3D NoC结构图Fig.2 The 3D NoC structure based on dual port RNI

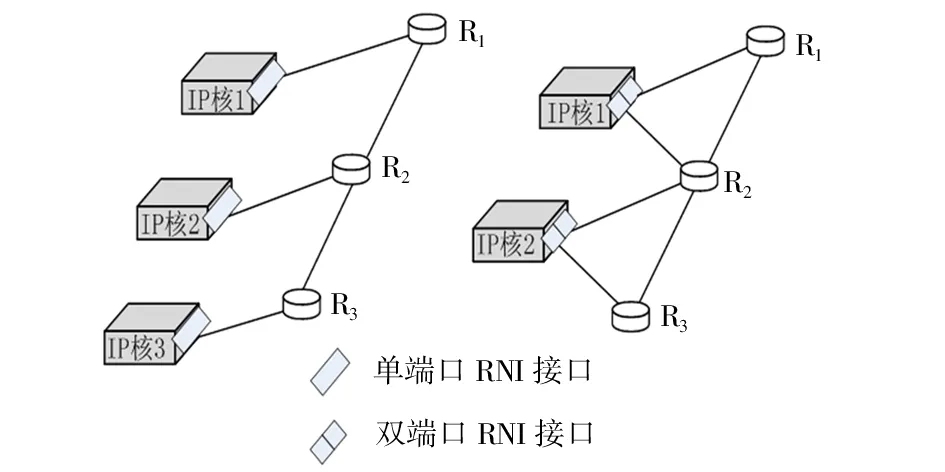

在每一个二维Mesh结构的平面上,采用双端口RNI来完成IP核与路由器的连接。使用传统RNI和使用双端口RNI进行IP核与路由器互联的结构如图3所示。图3左边为基于传统RNI的IP核与路由器的连接,每个IP核通过RNI连接到一个路由器上;右边为基于双端口RNI的IP核与路由器的连接,每个IP核通过双端口RNI分别连接至Y维上相邻的两个路由器上,实现了对IP核的加固。

图3 传统RNI与双端口RNI IP核与路由器连接图Fig.3 The traditional RNI and dual port RNI connection diagram between IP core and router

2.2 双端口RNI的设计

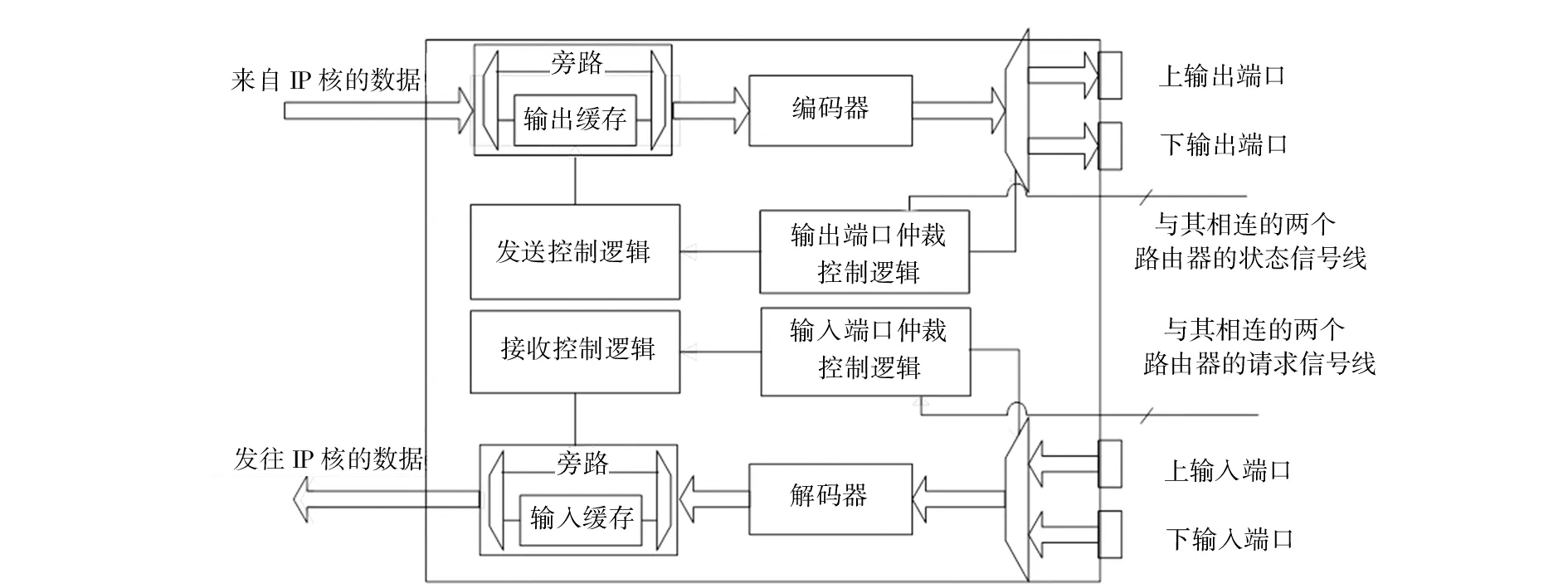

传统RNI接口只有一对输入输出接口,主要由输入接口、输出接口、输入缓存、输出缓存、编码器、解码器、发送控制逻辑和接收控制逻辑等模块组成。本文设计的双端口RNI是在传统RNI基础上添加了一对输入输出端口,增加了输入/输出端口仲裁控制、数据分配器、多路选择器和相应的控制逻辑单元,如图4所示。图4中的数据分配器用于输出端口的选择;多路选择器用于输入端口的选择;输出端口仲裁控制逻辑能够根据目的IP核的位置及所连接的2个路由器的故障状态完成数据包输出端口的选择。为了提高与IP核通信的效率,还增加输入缓存和输出缓存的旁路机制设计。当通信网络不拥塞时,IP核产生的数据通过输出缓存旁路机制跳过输出缓存直接进行输出数据微片的编码,加快了数据注入通信网络的速度;当通信网络拥塞时,借助输出缓存对待发送的数据进行排队暂存,指导数据微片依序注入网络。

2.3 数据报文的格式

本文采用普遍使用的虫孔路由机制,一个数据包被分成3种类型的微片,分别是头微片、数据微片和尾微片。数据包格式如图5所示,使用2位用作微片类型标志,分别以01代表头微片、00代表数据微片、10代表尾微片。头微片中带有地址信息,用于数据包的路由,其目的地址、备用地址和源地址各占9位,每个地址的9位中均含有X维坐标值3位、Y维坐标值3位和Z维坐标值3位,用于定位路由器的位置。头微片中目的地址和备用地址用于指明目标IP核所连接的2个路由器的地址,源地址用于指明数据包从哪个路由器发出。头微片中的IP核标志位字段用于指明路由器上的哪个IP核,该字段占3位,前2位分别用于指明目的IP核在目的地址和备用目的地址路由器上的位置,最后一位用于指明源IP核在源地址路由器上的位置。假设源地址为(x,y,z),当源地址对应的IP核标志位值为“0”时,代表IP核处于路由器(x,y,z)和路由器(x,y-1,z)之间;

图4 双端口RNI结构图Fig.4 The structure diagram of dual port RNI

图5 数据包格式Fig.5 The data packet format

如果为“1”,则代表IP核处于路由器(x,y,z)和路由器(x,y+1,z)之间。

2.4 双端口RNI的工作过程

当采用内建自测试方法测试到路由器出现硬件故障时,路由器通过状态信号线将故障状态信息发送给双端口RNI;双端口RNI的输出仲裁逻辑会根据故障信息和目的IP核的位置对输出端口进行选择,而与通信双方IP核所处的平面(Z平面)没有关系。

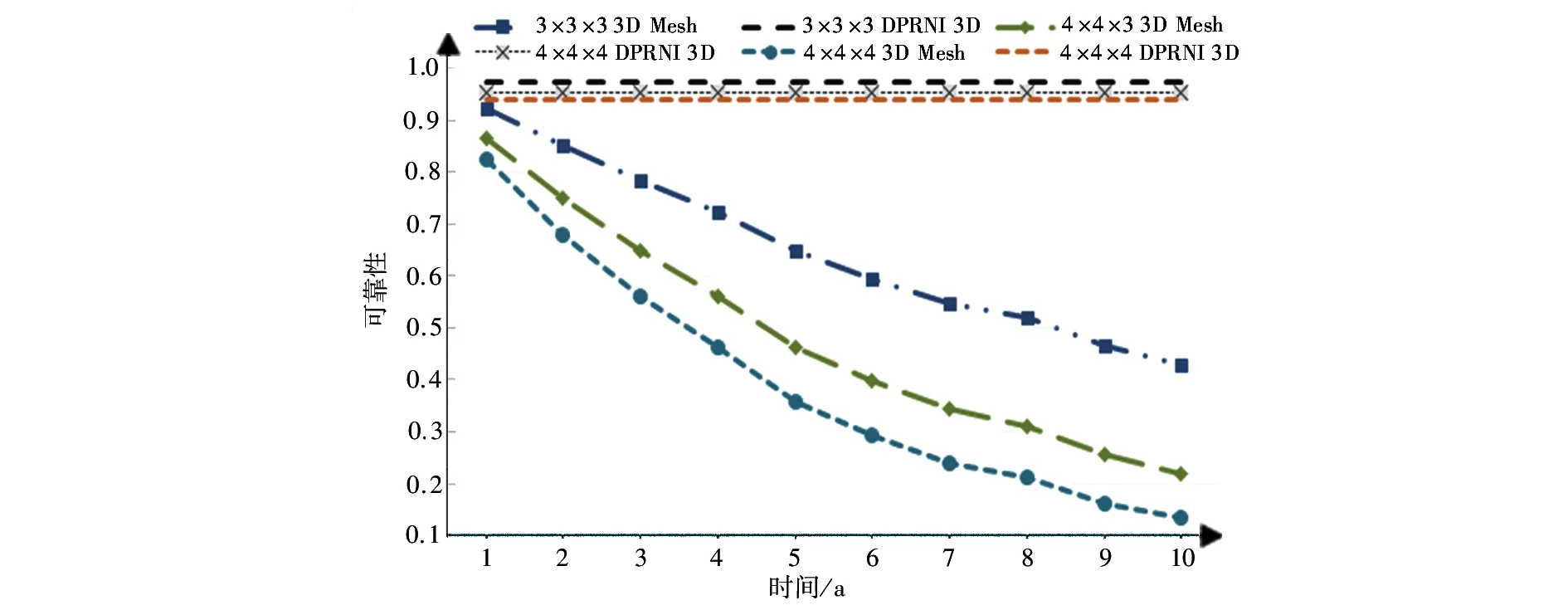

现以同一平面上2个IP核的通信过程来介绍双端口RNI的工作过程。假设源IP核连接的2个路由器地址分别为R1(x1,y1,z1)和R2(x1,y1+1,z1),目标IP核连接的2个路由器地址分别为R3(x2,y2,z1)和R4(x2,y2+1,z1),如果源IP核所连接的2个路由器中有一个出现故障,则选择无故障的路由器发送数据。当源IP核所连接的2个路由器都无故障,此时如果y1=y2,则根据R1、R2的通信繁忙程度选择当前通信任务量小的路由器作为发送路由器,从目标IP核所连接的两个路由器中选择与发送路由器y坐标值相同的路由器作为接收路由器,另外一个路由器作为备用路由器;如果y2>y1时,如图6a所示,源IP核对应的RNI会通过上端口选择R2来发送数据包,并且选择R3作为此次通信中目的IP核的接收路由器,R4作为备用目的路由器,同时在数据包头微片中将IP核标志位设置为“100”,其中第一位“1”代表目标IP核处于目标地址对应路由器的上方,第二位“0”表示目标IP核处于备用目标地址对应路由器的下方,第三位“0”表示源IP核处于源地址对应路由器的下方;如果y2 为了评估本文提出的基于双端口RNI 3D NoC(简称DPRNI 3D NoC)的通信架构的实施效果,分别对DPRNI 3D NoC和传统3D Mesh NoC两种通信架构进行可靠性分析和通信性能的模拟。系统可靠性和性能的提升必然要牺牲额外硬件开销,为此,对DPRNI 3D NoC通信架构的硬件开销情况进行了分析。 a IP1发送数据包至IP12 b IP9发送数据包至IP4图6 发送数据的IP核与接收数据的IP核的2种不同的位置关系Fig.6 Two different positional relationships between the IP core transmitting data and the IP core receiving data 路由器的可靠性可以定义为该路由器能够正常工作的概率,通常由路由器的错误率决定,可以用R来表示。单位时间内路由器发生故障的次数称为路由器的错误率,用λ表示。路由器的错误率与可靠性服从公式(1)所示的负指数分布[12]。 R=e-λt (1) 式中:R为路由器的可靠性;λ为路由器的错误率,次/a;t代表路由器的工作时间,a。 在传统的3D Mesh NoC通信架构中,每个路由器连接一个IP核,IP核正常通信的可靠性取决于所连接路由器的可靠性。在DPRNI 3D NoC中,每个IP核都连接至2个路由器,只有当所连接的2个路由器同时出现故障时该IP核才无法正常通信。因此这种通信架构中单个IP核的可靠性RD可以使用公式(2)计算得出。 RD=1-(1-R)2 (2) 上述两个公式可以分别对传统3D Mesh NoC和DPRNI 3D NoC中IP核的通信可靠性进行量化,然后再进一步地对2种架构的系统通信可靠性进行评估。 假设传统3D Mesh NoC 与DPRNI 3D NoC中IP核的数目都为n×n×n,3D NoC系统的通信可靠性则是n3个IP核都正常通信的可能性。3D NoC系统的通信可靠性Rs可以通过公式(3)计算得出。 Rs=RDn×n×n (3) 分别对3×3×3、4×4×3、4×4×4结构的3D Mesh NoC及具有相同IP核数目的DPRNI 3D NoC进行系统可靠性计算。参照文献[13],将错误率λ设为0.003 15次/a,2种架构在27核、48核、64核的情况下系统通信可靠性如图7所示。 图7 不同核数的3D Mesh与DPRNI 3D NoC的系统可靠性比较Fig.7 System reliability comparison between 3D mesh and DPRNI 3D NoC with different cores 由图7可以看出,3×3×3、4×4×3、4×4×4的3D Mesh NoC在第1年使用时的系统可靠性分别为0.92、0.87、0.83;工作到第10年时,它们的系统通信可靠性分别降低至0.43、0.22、0.13。显然,传统的3D Mesh NoC系统的整体通信可靠性不仅随着IP核数目的增加而降低,而且还会随着芯片工作年限的不断增加而急剧下降。与此形成鲜明对比的是,3×3×3、4×4×3、4×4×4的DPRNI 3D NoC在第1年使用时的系统可靠性分别为0.97、0.95、0.94;工作到第10年时,它们的系统通信可靠性保持不变,仍然是0.97、0.95、0.94。显然,本文提出的DPRNI 3D NoC通信架构具有更好的通信可靠性和稳定性。 容错性能评价指标主要有故障率、数据包时延和平均时延3个指标。其中故障率是指故障链路与故障路由器数目占所有路由器和链路总数的百分比;数据包时延是指一个数据包从它的首部进入网络开始,到该数据包的尾部离开网络所使用的时间;平均时延是指网络中传输的所有数据包的时延平均值,是衡量网络通信传输性能的重要指标。 使用Booksim 2.0模拟器对4×4×4的3D Mesh NoC和DPRNI 3D NoC的容错性能进行模拟试验。模拟时,这2种通信架构的通信方式均采用均匀随机模式,路由算法都是动态自适应容错路由算法,数据包注入率均为0.06,2种架构经模拟试验得到数据包平均时延随故障率的变化情况,如图8所示。 从图8可以发现,与传统的3D Mesh NoC通信架构相比,本文提出的DPRNI 3D NoC通信架构在不同故障率下都具有较低的数据包通信时延;随着故障率的不断增加,这种优势更加明显。DPRNI 3D NoC架构中每个IP核都连接了2个路由器,在故障率较低的情况下,可以充分利用路径的丰富性,有效缩短IP核间的通信路径长度,具有较低的数据包平均时延;随着故障率的增加,传统3D Mesh NoC架构中故障路由器所连接的IP核会存在丢包现象,而本文提出的DPRNI 3D NoC通信架构可以有效避免这种情况的发生。因此,本文提出的DPRNI 3D NoC通信架构,其数据包的平均时延要优越于传统的3D Mesh NoC架构。 图8 不同故障率下数据包平均时延比较Fig.8 Comparison of average packet delay under different failure rates 与传统的3D Mesh NoC架构相比,本文提出的DPRNI 3D NoC架构在每一个平面增加了一行路由器,即相对于3×3×3、4×4×3、4×4×4的3D Mesh NoC,与之具有相同IP核数量和布局的DPRNI 3D NoC架构分别多用了9、12、16个冗余路由器。通过计算冗余路由器占对应的3D Mesh架构中路由器总数的比率可以衡量DPRNI 3D NoC架构的硬件开销,如表1所示。 表1 不同规模DPRNI 3D NoC 冗余路由器的开销比Table 1 The overhead ratio of redundant routers base DPRNI 3D NoC of different sizes 由表1可知:与传统的3D Mesh架构相比,27核、28核、64核的DPRNI 3D NoC硬件开销分别为33%、25%、25%;随着n值的不断增大(网络规模不断扩大),在n×n×n的3D NoC中,冗余路由器数目占与之对应的3D Mesh NoC中路由器总数的比率不断下降((1/n)×100%)。因此,随着3D NoC系统规模的不断扩大,为提高片上系统IP核通信可靠性而为之增加的硬件开销将不断下降。 针对3D NoC通信架构中IP核连接单个路由器可能存在的单点故障问题,设计了一种双端口的资源网络接口,即在传统的3D Mesh结构基础上,将IP核通过双端口RNI分别连接在Y维上相邻的2个路由器上,从而得到一种新的3D NoC通信架构——DPRNI 3D NoC。实验结果表明,与传统的3D Mesh NoC通信架构相比,DPRNI 3D NoC通信架构具有更好的通信性能和较好的可靠性;而且为了提高这种可靠性和通信性能而花费的硬件开销也在可以接受的范围内,并且随着DPRNI 3D NoC规模的不断扩大,这种开销占比越来越小。3 实验分析

3.1 可靠性分析

3.2 容错性能分析

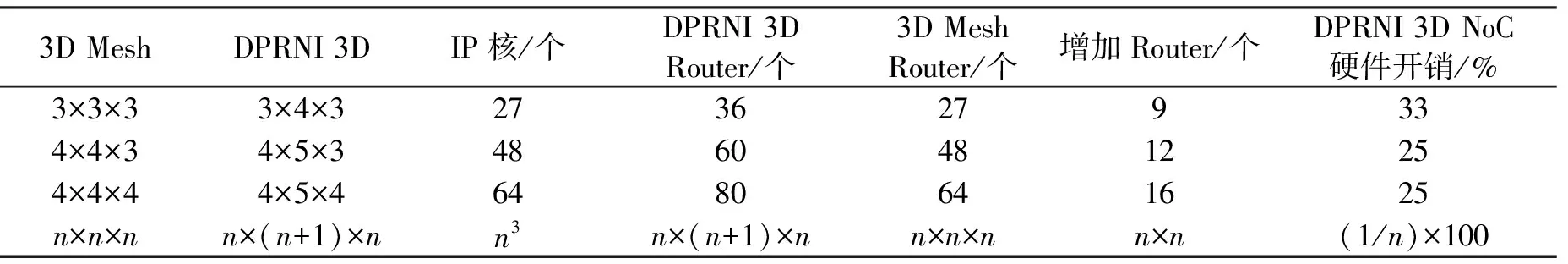

3.3 硬件开销分析

4 总结