零中频接收机的直流偏移消除和自动增益校准

2022-04-08郭慧民阎跃鹏

郭慧民 阎跃鹏

摘要:为了精确消除零中频接收机中的直流偏移并快速响应射频接收机增益调整时引入的输入直流偏移变化,提出了一种混合型直流偏移消除电路.该电路结合了模拟型和数字型直流偏移消除技术的优势,在降低输出直流偏移的同时缩短了响应时间.模拟型直流偏移消除电路用于实时地自动消除各级输入的直流偏移,数字型直流偏移消除电路通过自动校准进一步减小接收机的最终输出直流偏移.同时提出了一种接收机增益自动校准电路,能够自动校准零中频接收机I/Q通路的增益失配.采用65nmCMOS工艺实现了集成直流偏移消除的可编程增益放大器和增益自动校准电路.芯片测试结果表明,放大器最大输出直流偏移为2mV,增益调整具有严格单调性,自动校准后的输出I/Q增益失配小于0.1dB.该电路具有响应快、仅需开机自动校准和无需数字基带电路参与等优点,完全满足IEEE802.11ax-2021等宽带通信接收机的系统要求.

关键词:半导体集成电路;零中频接收机;宽带通信系统;直流偏移消除;I/Q增益失配自动校准

中图分类号:TN43

文献标志码:A

IEEE802.11ax-2021(也称作WIFI 6)[1]是下一代无线局域网通信系统,该标准于2021年2月由IEEE正式批准.符合IEEE802.11ax-2021标准的射频收发机是当前的研究热点之一.与LTE[2]和传统WLAN[3-4]等宽带系统类似,零中频射频接收机是适合于IEEE802.11ax-2021系统的射频接收机架构.但是,在射频接收机中,直流偏移会导致接收机中可编程增益放大器的输出电压饱和,使其后的模数转换器以及整个接收机功能失效.传统的用于零中频接收机的直流偏移消除技术可以分为模拟型直流偏移消除[5-7]和数字型直流偏移消除[8]两类.文献[5-7]中采用的模拟型直流偏移消除技术虽然电路形式不同,但其原理都是通过检测可编程增益放大器的输出直流偏移,利用负反馈环路实时地在放大器输入端进行补偿,以快速响应放大器的增益和输入直流偏移的变化.但是,由于模拟型直流偏移消除电路中用于检测输出直流偏移的检测放大器自身也存在直流偏移,因此仅采用模拟型直流偏移消除的可编程增益放大器的输出会存在较大的残留直流偏移.

例如,文献[5]中的残留直流偏移达到14mV.文献[8]中的数字型直流偏移消除电路通过基带输出的数字控制字可以将放大器的输出直流偏移减小至5mV,但需要数字电路根据模数转换器的输出数据计算出放大器的输出直流偏移值并消除.因此,电路响应时间长达5.7ms.本文提出了一种模数混合型直流偏移消除电路,同时实现精确的直流偏移消除和对输入直流偏移变化的快速响应.本文还提出了一种实用的接收机增益自动校准方法,并与集成混合型直流偏移消除的可编程增益放大器实现于同一测试电路中.

1集成直流偏移消除和I/Q增益失配校准的零中频接收机

图1所示为零中频接收机的典型架构.射频信号经过匹配电路进入低噪声放大器后,经过下变频混频器分为I通路和Q通路后分别经过信道选择滤波器进行信道选择.其后的可编程增益放大器通常具有较高的增益,用于将信号进一步放大至符合模数转换器(ADC)的输入量程.本文提出的混合型直流偏移消除电路集成于可编程增益放大器中.零中频接收机中通常需要I/Q增益失配消除电路,以确保模数转换器输出给数字基带的I/Q两路信号具有相同的幅度[9-12].本文在可编程增益放大器的输出设计了一种I/Q增益失配自动校准电路,无需数字基带电路参与即可实现增益失配的自动校准.

图2为集成混合型直流偏移消除电路的可编程增益放大器架构.该可编程增益放大器由五级放大级组成.其中,第一级到第三级采用相同的电路,每级实现0~15dB的增益,增益步长为5dB.第四级采用固定4dB增益加上0dB、4dB和8dB三档可调增益.第五级采用6dB增益加上0dB、1dB、2dB和3dB四档可调增益.通过适当的数字编码,可将放大器的6位增益控制位對应到各放大级的增益控制位,实现10~66dB的增益调节范围和1dB的增益调节步长.

混合型直流偏移消除电路包括模拟型直流偏移消除电路和数字型直流偏移消除电路.如图2所示,三个模拟型直流偏移消除电路分别位于第二级放大级输出与第一级放大级输入之间、第四级放大级输出与第三级放大级输入之间和第五级放大级输出与输入之间.数字型直流偏移消除电路位于第五级放大级,用于消除模拟型直流偏移电路3产生的残留直流偏移.模拟型直流偏移消除电路和数字型直流偏移消除电路将分别在第2节详细讨论.

2混合型直流偏移消除电路

2.1模拟型直流偏移消除电路

图3为可编程增益放大器的放大级和模拟型直流偏移消除电路.为了简明起见,图中以第五级放大级为例,即模拟型直流偏移消除电路位于同一放大级输出与输入之间.其它各级放大级和模拟型直流偏移消除电路采用与此类似的连接关系.如图3所示,放大级采用差分电阻反馈放大器架构,通过反馈电阻Rf与输入电阻Ri的比例确定放大级的增益,以实现精确的增益控制.控制电阻连接的开关由PMOS管和NMOS管并联组成的传输门实现,置于运算放大器的输入端.这是由于高增益的运算放大器闭环工作时,输入端为“虚地”点,信号幅度很小.因此,可以避免放大级输入的大幅度信号通过传输门开关时引起的非线性效应.保持导通状态的开关SW_dmy与反馈电阻Rf串联,以提高反馈电阻与输入电阻间的匹配精度.模拟型直流偏移消除电路由电阻、电容和检测放大器构成.检测放大器的输入和输出分别连接放大级的输出和输入,以形成负反馈网络.这个负反馈网络会在放大级的输出与输入间形

成高通频率响应,从而消除输入和放大级自身的直流偏移.通过调整电阻R1和R2值和电容C1和C2值,可以调整高通频率响应的-3dB频率点位置.在调整增益时,可以将R1和R2旁路以减小响应时间.R3和R4用于将检测放大器的输出电压转化成电流,控制放大级的输出直流偏移.

图4示出了可编程增益放大器的供电电源启动时各种工艺角(FF,TT,SS,SF,FS)和高低温度(-40°C,27°C,125°C)组合下的瞬态仿真结果.仿真时设置放大器输入为直流信号,输入直流偏移为40mV,增益为最大值,以考察最差情况下的可编程增益放大器的性能.可见,在所有工艺角和温度组合下,可编程增益放大器的差分输出电压都不会出现饱和,并且都可以在1μs内稳定到接近输出共模电压.这反映出模拟型直流偏移消除电路快速响应的特点.

虽然模拟型直流偏移消除电路具有响应时间短、无需数字基带电路参与等优点,但它是基于直流偏移消除电路中的检测放大器对放大级输出直流偏移的检测结果进行补偿的.由于器件的匹配精度所限,检测放大器并不是一个理想放大器,其自身也存在直流偏移.如图3所示,检测放大器自身的直流偏移可以等效为放大器输入端存在一个固定的直流电压VOS.它会被检测放大器放大后进入放大级反馈环路,进而被放大级放大,导致放大级输出残留的直流偏移.该残留直流偏移无法通过模拟型直流偏移消除电路消除,必须由其它校准电路对其进行补偿才能消除.而且,检测放大器的直流偏移值主要由器件的匹配精度决定,呈现随机分布的特点.实际电路设计中,即使牺牲面积,将检测放大器的晶体管尺寸设计得非常大,仍难以在量产时将所有芯片的最大输出直流偏移减至5mV以下.

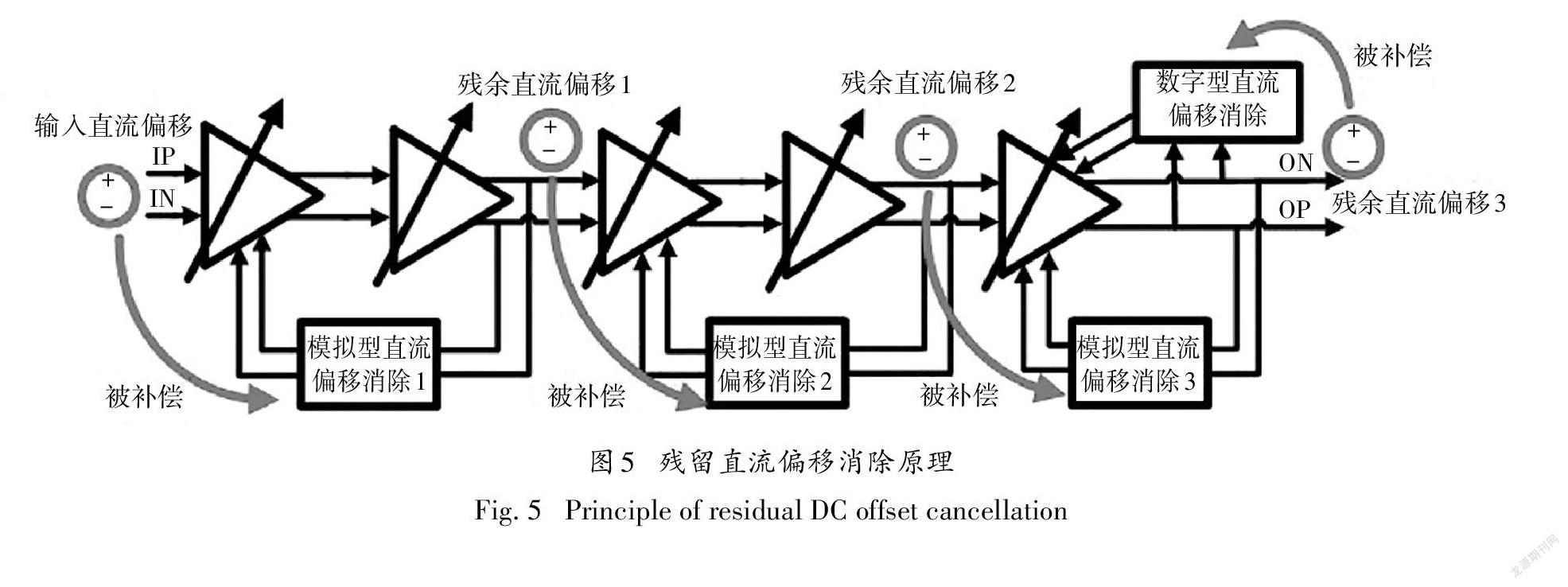

模拟型直流偏移消除电路产生的残留直流偏移不仅存在于第五级放大级输出,同样也存在于第二级和第四级放大级输出.但分析表明,它们不会对可编程增益放大器的最终输出直流偏移产生贡献.如图5所示,来自前级下变频混频器的输入直流偏移会被位于第一级和第二级之间的模拟型直流偏移消除1补偿.它产生的残留直流偏移1可以看作第三级的输入直流偏移,将会被位于第三级和第四级之间的模拟型直流偏移消除2补偿.类似地,残留直流偏移2会被位于第五级的模拟型直流偏移消除3补偿.因此,它们不会构成可编程增益放大器的最终输出直流偏移.但是,由于第五级是可编程增益放大器的最后一级放大级,其后不再有模拟型直流偏移消除电路.如果没有其它补偿措施,它产生的残留直流偏移3就是可编程增益放大器的最终输出直流偏移.如前文分析,第五级的残留直流偏移由检测放大器的输入直流偏移和放大级的增益共同决定.虽然不同芯片产生的残留直流偏移值会随机分布,但是对于每个确定的芯片,检测放大器的输入直流偏移是固定不变的.放大级的输出残留直流偏移只会随放大级增益不同而变化.由于第五级放大级只有四档增益控制,如果能够针对每档增益控制进一步补偿残留直流偏移,就可以使整个可编程增益放大器在所有增益控制下的输出直流偏移都减为最小.因此,本文在模拟型直流偏移消除电路的基础上,在最后一级设计了数字型直流偏移消除电路,通过自动校准进一步消除可编程增益放大器的输出残留直流偏移.

2.2数字型直流偏移消除电路

图6示出了可编程增益放大器的放大级和数字型直流偏移消除电路的架构.数字型直流偏移消除电路由自动归零比较器、控制状态机和数模转换器组成,仅应用于可编程增益放大器的最后一级.自动归零比较器用于比较放大级的输出OP端和ON端的电压,将比较结果经过控制状态机处理后输入8位数模转换器.数模转换器的输入连接至放大级的运算放大器输入端,以控制放大级的输出直流偏移.进行校准时,首先通过导通开关SW0连接放大级的输入IP和IN端,使校准过程中放大级不受前级输出影响.自动归零比较器比较OP端和ON端的电压,控制状态机根据比较器的输出通过二进制搜索算法将控制字输出给数模转换器,用于调整放大级的输出直流偏移.经过8次比较后可以得到优化的8位数模转换器控制字,使OP端和ON端的电压差值,也就是放大级的残留直流偏移减至最小.由于输出残留直流偏移会随放大级的增益不同而变化,所以需要针对偏移会随放大级的增益不同而变化,所以需要针对IN放大级的每档增益控制分别进行一次校准.全部校准完成之后,将得到的数模转换器的控制字存储于芯片的寄存器中.正常工作时,使用与增益控制对应的8位控制字作为数模转换器的输入,即可实现对放大器残留直流偏移的精确校准.

图7(a)示出了数字型直流偏移消除电路中的自动归零比较器电路.自动归零比较器由采样电容、放大器和由非交叠时钟CLK和CLKN控制的开关组成.相位1时,CLK为高电平,CLKN为低电平;相位2时,两者相反.相位1时,SW2断开,SW1和SW3导通,放大器闭环形成一个单位增益放大器.只要放大器的增益足够高,放大器的负极输入端就近似等于VREF,形成一个“虚地”点,将IP端的电压采样至电容上.在相位1时,放大器中的SW0也保持导通,形成密勒补偿,保证闭环放大器的稳定性.在相位2时,SW2导通,SW1和SW3断开.将IN端电压连接至采样电容左端.由于采样电容上的电荷保持守恒,IP端和IN端的电压差值将表现为放大器负极输入端和VREF的差值,实现了对IP端和IN端电压的比较.在相位2时,由于SW3断开,放大器开环工作,起到比较器的功能.同时SW0断开,密勒补偿不再起作用,提高了比较器的响应速度.

与模拟型直流偏移电路中的检测放大器类似,自動归零比较器中的放大器也存在输入直流偏移,在图7(a)中等效表示为在放大器负极输入端存在一个直流电压VOS.记VX点的电压在相位1时为VX1,在相位2时为VX2.则相位1时,运算放大器闭环工作,得到公式

相位2时,根据采样电容电荷守恒,得到公式

可见,由于在对IP和IN端电压的两次采样中都包含了放大器自身的输入直流偏移VOS,理论上可以将VOS完全消除,实现高精度的电压比较.实际电路中,自动归零比较器的比较精度可以小于1mV.

图7(b)示出了数字型直流偏移消除电路中的数模转换器电路.数模转换器采用8位差分R-2R架构,有利于减小电阻的总面积和简化放大器的设计[13-15].数模转换器的输出电压经过输出电阻RO转化为输出电流,反馈至放大级中运算放大器的输入端,以控制放大级的输出直流偏移.控制状态机采用传统的二进制搜索算法,逐次逼近到最优的输出控制字.最终的校准精度由自动归零比较器的比较精度和数模转换器的转换精度共同决定.

3I/Q增益失配自动校准

由于接收机的输入信号的功率大小会受到发射机信号发射功率变化以及信道环境变化的影响,因此接收机需要具有自动增益控制机制,以将图1中ADC的输入信号幅度调整至适合ADC采样的范围.通常,自动增益控制算法由数字基带电路实现,不包含于射频接收机中.数字基带电路根据ADC输出的多位数字码计算出ADC输入的模拟信号的幅度,通过负反馈控制系统,调整可编程增益放大器的增益值,直到ADC的输入信号幅度达到预期值.自动增益控制要求接收机的可编程增益放大器具有单调的增益控制,以形成有效的负反馈控制系统.

在零中频接收机中,I通路和Q通路的增益失配会导致I、Q两路信号发生混叠,造成有效信噪比降低.传统的增益失配补偿方法通常由数字基带电路实现[16-18].但是,数字基带电路只能处理模数转换器输出的数字信号,计算精度会受限于模数转换器的转换精度.本文提出一种无需数字基带参与的增益失配自动校准方法.图8(a)示出了该电路的架构.I通路和Q通路的可编程增益放大器的输出通过一个电压幅度检测器将放大器输出的中频信号幅度转化为直流电压.使用图7(a)所示的自动归零比较器比较I通路和Q通路中电压幅度检测器的输出直流电压的差值,就可以得到I通路和Q通路的增益差值.

在传统电阻反馈放大器中,反馈电阻或输入电阻通常与控制开关串联以实现增益控制.但是常用的传输门开关会引入随工艺和温度变化寄生电阻,进而影响增益精细调节的单调性和准确度.图8(b)示出了本文提出的采用电阻分压阵列实现的增益精细调节电路,它位于可编程增益放大器的第三级与第四级之间和第四级与第五级之间,共有5位数字控制.其中Rp1~Rp14远大于Rs.当只有开关SW1导通时,输出差分电压VOUT为

对应的电压增益G为

例如,当Rs/Rp1=1/126时,对应的增益值为约-0.07dB.由于Rp远大于与其串联的传输门开关的导通电阻,传输门开关的导通电阻值及其随温度的变化对增益的影响都可以忽略.设计中只要确保Rp14<Rp13<...<Rp1,就可以实现单调的增益精细调节.可编程增益放大器的I通路和Q通路各自具有步长约为0.07dB、调节范围约为2dB的增益精细调节功能,能够将接收机的I/Q通路的增益失配校准到小于0.1dB.

图8(c)示出了控制状态机的流程图.通过控制状态机中的二进制搜索算法,分别控制I通路和Q通路的增益精细调节电路,使增益差值达到最小.校准时,可以依次对I、Q通路进行校准,直到得到最小增益差值所对应的控制字.将控制字存储于寄存器中后,可以关闭校准电路以节省功耗.由于中频信号是由射频输入信号经过整个接收机通路产生,因此可以实现对接收机总增益失配的校准.

4测试结果

图9示出了集成直流偏移消除和增益校准的可编程增益放大器的测试样片照片,包含完全相同的I通路和Q通路电路,以对称布局排列,总面积为0.4mm2.中间部分为I/Q通路的共用电路,包括电流偏置及控制位译码器等电路.

图10(a)示出了9块样片中仅开启模拟型直流偏移消除电路和开启混合型直流偏移消除电路两种模式下测试得到的可编程增益放大器的输出直流偏移值.可见,仅开启模拟型直流偏移消除电路时,有些样片中的输出直流偏移也可以低至2mV,个别样片可以低至1mV.这是由于部分样片中模拟型直流偏移消除3中的检测放大器本身的输入直流偏移已经很小.但是,也有些样片的输出直流偏移超过2mV,甚至达到12mV.这体现出了检测放大器的输入直流偏移值受器件匹配精度影响而出现的随机分布特点,与理论分析和仿真结果一致.在开启混合型直流偏移消除电路,也就是经过数字校准后,全部样片的输出直流偏移值都不超过2mV(其中9号样片为0mV).这表明混合型直流偏移电路中的数字校准电路达到了设计预期的性能,进一步补偿了模拟型直流偏移消除电路引入的残留直流偏移.输出信号线性度是可编程增益放大器的另一个重要指标.由于放大器由多级闭环放大级组成,当每级放大级设置为最大增益时,反馈深度最小,所对应的线性度也最差.图10(b)示出了使用频谱分析仪测试得到的最大增益下可编程增益放大器的输出频谱,以评估在最差条件下放大器的线性度.可见当输出频率为8MHz,输出幅度约为4dBm时,最大谐波为三次谐波,其值小于-60dBm,谐波抑制比超过64dB,表明放大器具有良好的线性度.

如第3节所述,可编程增益放大器增益控制的单调性对接收机的自动增益控制至关重要.图11(a)示出了可编程增益放大器的增益控制单调性测试.可见,在整个增益调节范围内,增益调节步长在0.7dB到1.2dB之间,满足约1dB步长的设计要求,并且增益控制具有严格的单调性.增益步长的误差主要来自每级放大级中反馈电阻与输入电阻之间在制造工艺中的失配以及各放大级之间的绝对增益值的失配.图11(b)示出了可编程增益放大器在不同增益设置下的增益精细调节测试.可见,在各种增益下,增益精细调节都可以保证单调性,自动校准后的输出I/Q增益失配小于0.1dB.

表1示出了本文提出的混合型直流偏移消除电路与文献报道的电路關键参数性能比较.可见,由于结合了模拟型和数字型直流偏移消除技术的优点,混合型直流偏移消除电路能够同时实现最小的直流偏移和最短的响应时间.

5结论

本文提出了一种混合型直流偏移消除电路,该电路结合了模拟型直流偏移消除电路实时补偿和数字型直流偏移消除电路自动校准的优势,同时实现了精确直流偏移消除和对输入直流偏移变化的快速响应.I/Q增益失配自动校准电路能够独立工作,无需数字基带参与,只需开机自动校准即可消除I/Q增益失配.对多个样片的测试结果表明,增益放大器的最大输出直流偏移为2mV,增益步长在0.7dB到1.2dB之间,增益调整具有严格的单调性.并且放大器的频率响应和输出信号线性度都符合设计指标要求.经过自动校准后的放大器输出I/Q增益失配小于0.1dB.与传统直流偏移消除和I/Q增益失配校准电路相比,该电路具有输出直流偏移小、响应时间短、无需数字基带参与等多项优点,可以广泛应用于下一代无线局域网IEEE802.11ax-2021等宽带通信系统中.

参考文献

[1]IEEE 802.11ax-2021 IEEE Standard for Information Technol⁃ogy--Telecommunications and Information Exchange between Sys⁃tems Local and Metropolitan Area Networks--Specific Require⁃ments Part 11:Wireless LAN Medium Access Control(MAC) and Physical Layer (PHY) Specifications Amendment 1:En⁃hancements for High-Efficiency WLAN[S]. New York,IEEE Computer Society,2021:36-704.

[2]MIKHEMAR M,KAHRIZI M,LEETE J C,et al.A Rel-12 2G/ 3G/LTE-Advanced 3CC cellular receiver[J]. IEEE Journal of Solid-State Circuits,2016,51(5):1066-1079.

[3]AHOLA R,AKTAS A,WILSON J,et al.A single-chip CMOS transceiver for 802.11a/b/g wireless LANs[J].IEEE Journal of Solid-State Circuits,2004,39(12):2250-2258.

[4]VAVELIDIS K,VASSILIOU I,GEORGANTAS T,et al. A dual- band 5.15-5.35-GHz,2.4-2.5-GHz 0.18- μm CMOS transceiver for 802.11a/b/g wireless LAN[J]. IEEE Journal of Solid-State C i r c u i t s ,2 0 0 4 ,3 9( 7 ):1 1 8 0 - 1 1 8 4 .

[5] ZHENG Y J,YAN J N,XU Y P.A CMOS VGA with DC offset cancellation for direct-conversion receivers[J].IEEE Transac⁃tions on Circuits and Systems I:Regular Papers,2009,56(1): 103-113.

[6] LEE K Y,LEE S W,KOO Y,et al.Full-CMOS 2-GHz WCDMA direct conversion transmitter and receiver[J]. IEEE Journal of Solid-State Circuits,2003,38(1):43-53.

[7]GATTA F,MANSTRETTA D,ROSSI P,et al.A fully integrated 0.18- μm CMOS direct conversion receiver front-end with on- chip LO for UMTS[J]. IEEE Journal of Solid-State Circuits, 2 0 0 4 ,3 9( 1 ):1 5 - 2 3 .

[8]JIN J,LIU X M,YAN T T,et al.Fully configurable capacitor- less oversampling DC offset cancellation for direct conversion re⁃ceivers[J].IEEE Transactions on Circuits and Systems II:Ex?press Briefs,2019,66(10):1683-1687.

[9]LIU X M,JIN J,SHI J J,et al.Comparator offset immune I/Q cali⁃bration technique for direct conversion receiver[J].IEEE Micro⁃wave and Wireless Components Letters,2020,30(1):109-111.

[10]VITALI S,FRANCHI E,GNUDI A.RF I/Q downconverter with gain/phase calibration[J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2007,54(4):367-371.

[11] HSIEH Y H,HU W Y,LIN S M,et al.An auto-I/Q calibrated CMOS transceiver for 802.11g[J].IEEE Journal of Solid-State C i r c u i t s ,2 0 0 5 ,4 0( 1 1 ):2 1 8 7 - 2 1 9 2 .

[12] GREEN R A,ANDERSON-SPRECHER R,PIERRE J W. Quadrature receiver mismatch calibration[J]. IEEE Transactions on Signal Processing,1999,47(11):3130-3133.

[13] MARCHE D,SAVARIA Y,GAGNON Y. An improved switch compensation technique for inverted R-2R ladder DACs[J]. IEEE Transactions on Circuits and Systems I:Regular Papers, 2 0 0 9 ,5 6( 6 ):1 1 1 5 - 1 1 2 4 .

[14] GUO W J,ABRAHAM T,CHIANG S,et al.An area- and power- efficient Iref compensation technique for voltage-mode R-2R DACs [J]. IEEE Transactions on Circuits and Systems II:Express B r i e f s ,2 0 1 5 ,6 2( 7 ):6 5 6 - 6 6 0 .

[15] KENNEDY M P.On the robustness of R-2R ladder DACs[J]. IEEE Transactions on Circuits and Systems I:Fundamental Theory and Applications,2000,47(2):109-116.

[16] ELMALA M A I,EMBABI S H K.Calibration of phase and gain mismatches in Weaver image-reject receiver[J].IEEE Journal of Solid-State Circuits,2004,39(2):283-289.

[17] MONTEMAYORR,RAZAVIB.Aself-calibrating900-MHz CMOS image-reject receiver[C]//Proceedings of the 26th Euro⁃pean Solid-State Circuits Conference.Stockholm,Sweden:IEEE, 2 0 0 0 :3 2 0 - 3 2 3 .

[18] DER L,RAZAVI B.A 2-GHz CMOS image-reject receiver with LMS calibration[J].IEEE Journal of Solid-State Circuits,2003, 3 8( 2 ):1 6 7 - 1 7 5 .