时序逻辑电路设计的经典案例教学探究

2022-03-23余安喜罗笑冰李德鑫杜湘瑜

余安喜, 罗笑冰, 李德鑫, 杜湘瑜

(国防科技大学 电子科学学院, 长沙 410073)

时序逻辑电路设计是“数字电路与逻辑设计”课程教学的重点和难点之一。考虑到同步时序逻辑电路的工作频率范围较宽,不易产生竞争-冒险现象,尽管电路较为复杂,在设计稳定性和工作频率要求较高的中大规模时序系统时一般采用同步时序电路来设计。

同步时序逻辑电路的一般设计方法如图1所示,主要包括逻辑抽象、状态化简、状态分配、逻辑化简、触发器选型、画逻辑图、自启动验证等设计过程。

图1 同步时序逻辑电路的一般设计方法

为了形象展示时序逻辑电路的设计方法和设计过程,许多教材采用了串行数据检测器的经典设计案例:设计一个串行数据检测器,要求连续输入3个或3个以上的1 时输出为1,其它输入情况下输出为0[1-2]。

教材通过详细介绍检测器的设计过程,较为清晰地表达出了状态化简的基本思想和基本原则。然而,多年来在广大师生之间围绕该经典案例引发的疑问、争论和质疑不断涌现,使得该教学案例成为本门课程的教学难点之一。2002年,龙胜春指出传统设计方法中状态化简后的电路在有些情况下是不能正常工作的[3]。2006年,陈云洽指出状态化简本质上不会改变电路的逻辑功能,并提出在输入数据稳定时进行检测的米利型和摩尔型电路设计方法[4]。

需要注意的是,教材指出,其所用方法要求输入数据与时钟信号同步,即状态转换的同时(时钟信号的有效边沿到来时),输入也改换为下一个输入数据。这一说明很自然给同学们带来疑问,实际情况下输入数据不大可能与时钟信号严格同步,而如果两者不同步,电路又该如何设计呢?应该如何选择电路结构,米利型和摩尔型电路的差异在哪里呢?围绕这些疑问,如果教师不能在教学过程中从基础概念上加以解释,势必造成学生在基本概念和知识体系学习上的不扎实、不完整,严重影响学习效果。

1 串行数据检测器设计及其缺陷分析

1.1 传统检测器设计及缺陷

在输入数据与时钟信号完全同步的理想情况下,教材给出的传统电路设计如图2所示。

图2 传统串行数据检测器设计

实际情况下,由于电路延时,这里同步假设过于理想。不失一般性,假设时钟周期和输入数据变化周期均为T(数据常常依时钟周期采样获得),而时钟下降沿较输入数据延迟时间d。取T=60 ns,d=20 ns,获得检测波形如图3所示。

图3 传统检测器的错误输出波形(d=20 ns)

可见,检测器在连续输入2个1时即错误输出了有效检测结果,且结果出现在数据输入1后(40+d) ns处,尚不足2个时钟周期,显然与设计目标不符。

1.2 改进型检测器设计及缺陷

考虑实际应用系统不应在数据转换瞬间进行检测,文献给出了两种改进方法[4]。

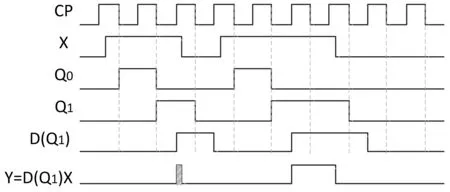

方法一是通过增加1个上升沿的D触发器,将触发器状态延迟到上升沿,然后再生成检测器输出。然而,该电路两种不同边沿触发器的使用让同学们理解问题更加困难,并且当时延d 图4 改进方法一的错误输出波形(d=20 ns) 方法二是设计一种摩尔型电路,在S3状态下输出检测结果,输出与时钟周期保持同步,且与输入不直接相关。尽管该方法可有效解决实际情况下数据与时钟不同步情况下的检测问题,但该解决方案不仅无法向同学们展示米利型电路设计实例,同时也不能引出等价状态的状态化简问题,失去了一个很好的状态化简实例,不符合本部分课程教学目标。 让我们回到电路设计的第一步逻辑抽象,来分析电路设计的本质,从而揭示产生以上现象的原因。实际上前述不同的电路设计是达成了不同的设计目标,进而形成了不同的逻辑抽象结果。由于原题目对设计目标描述不够具体,造成不同设计者对设计目标的具象不同,相应的逻辑抽象也不同。 (1)传统检测器的逻辑抽象是建立在数据同步的理想假设下,此时S2和S3两种状态下的输出和次态都是相同的,因此两状态等价,可以化简。这种情况下,检测输出与输入数据、时钟信号都是同步的。 (2)当数据不同步时,进入S2状态仅表示连续输入了两个1,此时输出应保持为0,而只有进入S3状态,才表明连续输入了3个或3个以上的1,此时输出应为1。可见,S2和S3两种状态的输出不同,即两状态不等价,也就不能做状态化简。此时,可将电路设计为摩尔型(改进方法二),让检测输出与时钟信号保持同步。 可见,数据转换与触发时钟是否同步,决定了电路设计要解决的问题在根本上就是不同的,相应的逻辑抽象也是不同的。不同的逻辑抽象结果下,状态的等价性发生了根本变化,状态化简过程也将随之改变,米利型和摩尔型的电路结构选择也就清晰了。更多情况、更详细的讨论可参见文献[5]。 考虑到实际应用中,检测时钟信号与输入数据有一定时延的,合理的解决思路是:首先将输入数据进行预处理,即通过一个时钟控制的寄存器,实现与检测时钟的同步,然后再输入一个传统的串行数据检测器。实用的串行数据检测器电路如图5所示。 图5 实用的串行数据检测器设计 图6给出了数据不同步时(d=20 ns)下的检测波形,可见检测结果的波形与设计目标相一致。 图6 实用电路的输出波形(d=20 ns) 需要说明的是,原教材在原例题解析中也给出了类似的补充说明,但未就数据不同步带来的影响展开深入讨论,也没有给出完整的电路设计,理解起来难度较大。 通过上面的分析,我们从检测时钟信号与输入数据不严格同步的实际情况出发,理清了数据同步预处理环节与经典电路设计方法的关系。我们可以通过将传统设计方法和实用的电路设计相结合,在课堂上以教学案例的形式,把时序逻辑电路设计方法与流程中涉及的逻辑抽象、状态等价、状态化简等理论问题完整的实例化展开,同时鼓励同学们在实验室实现该电路或者完成Verilog仿真,尝试分析其中的数据与时钟同步问题,通过观察记录不同延时情形下的波形,更加深入地去思考电路运行的内在机理,体会实际电路与经典理论之间的联系与区别,从而激发同学们夯实理论知识体系和解决实际问题的创新性思维能力。 本文围绕串行数据检测器这一时序逻辑电路设计的教学案例进行探讨,根据检测触发时钟与输入数据同步和非同步两种情形,分析了传统电路和两种改进型电路的输出波形、设计缺陷及其逻辑抽象本质,提出了实用化的电路设计,最后从如何激发同学们夯实理论知识体系和解决实际问题的创新性思维能力的角度,给出了本案例教学的具体实施方法。 总之,传统电路设计有利于理解时序逻辑电路设计中的状态化简问题,实用化的电路设计只需对电路前端引入预处理过程,实现简单。同时教学过程中,还可通过绘制各种情形下的波形图,形象展示米利型和摩尔型两种电路结构对输出波形的影响,还可鼓励同学们课后完成电路设计的全流程仿真。这样,教学过程的理论体系更完整、逻辑性更强,理论与实际应用相结合,对于活跃同学们应用理论知识解决实际问题的创新性思维很有益处。

2 从逻辑抽象解释电路设计本质

3 实用的串行数据监测器电路设计

4 具体案例教学实施方法

5 结语