新一代自主可控保护装置软硬件平台技术

2022-03-22陶保震严洪峰王宏宇

仲 伟,王 仲,陶保震,严洪峰,王宏宇

新一代自主可控保护装置软硬件平台技术

仲 伟,王 仲,陶保震,严洪峰,王宏宇

(江苏金智科技股份有限公司,江苏 南京 211100)

为满足智能变电站不断提升的海量高速数据处理要求,采用多核SoC+FPGA硬件方案,基于SylixOS嵌入式实时操作系统,研究分布式、多板卡结构的保护装置平台技术。提出FPGA高速前置数据处理设计,讨论多板卡互联的LVDS高速总线和CAN实时通信技术,并给出多板卡精确时钟同步和采样同步方案。基于异构多处理软件模型,研究了多核多任务并行处理架构,提出利用多板卡数据相互校核进一步提高装置可靠性的技术方案。最后基于软硬件平台技术,采用全国产化器件,完成了一系列继电保护装置的研制和测试。通过现场试运行检验,验证了该自主可控技术方案的可靠性和先进性。

自主可控;继电保护;实时操作系统;多核SoC;FPGA;背板总线

0 引言

近年来,为了妥善应对复杂多变的国际形势对国家用电安全的冲击,积极响应国家电网及南方电网公司关于大力推进二次设备国产化应用的号召,急需开发出一套适用于智能和常规变电站二次设备的统一的软硬件平台。该平台应满足新一代控制保护装置平台化、模块化、网络化、智能化方向发展的需要,采用全国产化的芯片方案,使用国产嵌入式实时操作系统,适用于国网、南网的智能及常规变电站二次设备产品应用。

1 硬件平台设计

微机保护经过二三十年的发展,其硬件架构不断进步,目前中高压保护装置在硬件设计上大多采用多板卡多CPU核的分布式设计方式,充分利用多核CPU的处理能力,将功能按照需求合理分布在多CPU或多个CPU核心上执行,提高了平台的整体性能以及可靠性[1-3]。同时由于当前智能变电站大容量高速数据处理的要求,特别是在三网(SV、GOOSE、MMS)合一情况下,如果仅仅使用CPU对这些数据进行处理,在极端环境下(如网络风暴)可能会影响高实时性的计算,例如SV插值、保护计算等。因此需要利用现场可编程门阵列FPGA (Field-programmable Gate Array)的高集成度、高性能、并行处理的特点,对这些数据进行预处理,过滤筛选后,才将有效数据交给CPU进一步处理,有效降低了CPU的处理工作量,提高了系统实时性。

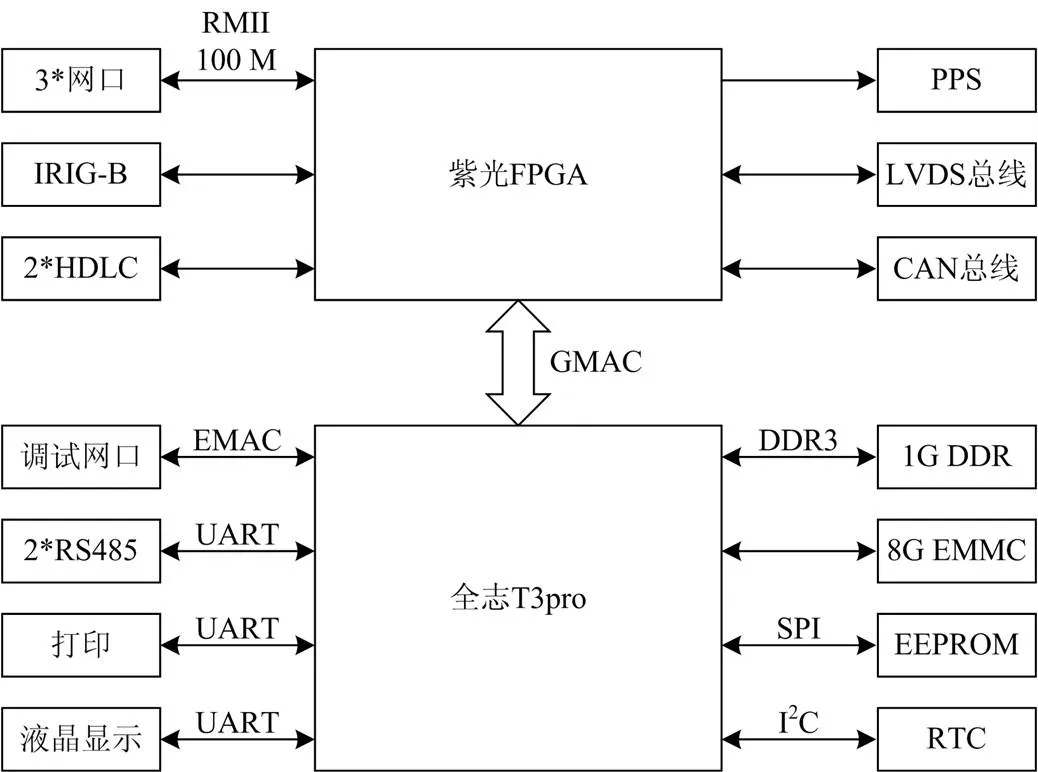

参照当前相对成熟的基于进口芯片的保护装置平台方案[4-11]以及行业相关技术规范的要求,平台总体硬件架构设计如图1所示。

图1 平台硬件架构

根据平台化、模块化的原则,将主要硬件按照功能划分为CPU板、SV/GOOSE处理板、模拟量采集板和开入开出板四大模块,各模件均采用智能板卡设计,板卡之间采用背板总线进行通信。除CPU板卡模件必选一块外,其他板卡均根据产品需求可选配,例如低压保护和测控装置可只选择一块CPU板模件,而高压保护可选多块CPU板模件,以实现多个CPU数据的相互校核,提高保护的可靠性[12-14];对于智能装置,则输入输出模件选择一块或多块SV/GOOSE处理板模件,而常规装置则选择模一块或多块模拟量采集板和开入开出板模件。

1.1 主CPU模件硬件设计

平台的CPU板模件均采用全志T3pro和紫光同创FPGA来实现,全志T3pro是一颗包含4核ARM Cortex-A7架构处理器的芯片,主频1.2 GHz,功耗低、性能强、接口丰富、性价比高,其四个核心可以AMP (Asymmetric Multi-Processing)模式分别运行不同的软件系统。

T3pro与FPGA之间采用千兆GMAC通信,具有传输速度快,通道带宽大的特点,有效保证了T3pro与FPGA之间数据交互的实时性。主CPU板硬件总体架构如图2所示。

图2 CPU板硬件架构

全志T3pro自带的EMAC接口,用于实现调试网口;自带的多个UART接口实现2路RS485、232打印和串口液晶功能;通过内置DDR3控制器提供1G的片外DDR RAM空间;8G EMMC用于实现操作系统的文件系统,主要用于存储引导代码、固件、设定值文件、报告、录波等数据;T3pro的SPI连接EEPROM芯片,用于存储掉电保存设定值;外部RTC芯片经I2C接入T3pro,为整装置提供实时时间。

FPGA实现3组站控层网口,并通过FPGA逻辑给这三个站控层网口提供报文过滤、风暴抑制等功能,提高站控层网络的稳定性[15];外部对时信号IRIG-B也接入FPGA,由FPGA负责对IRIG-B信号进行时间解码;此外,FPGA还提供2路HDLC接口,用以实现纵联差动与对侧装置的通信功能需求;主CPU板FPGA输出2路PPS差分信号,用于多板卡之间的采样同步和精确时钟同步;LVDS总线实现板间全双工的数据通信,主要用于CPU板与CPU板之间、CPU板与SV/GOOSE处理板之间以及CPU板与模拟量采集板之间高速数据交互,传输波特率160 Mbps[16-17];CAN总线主要用于CPU板与开入开出板模件之间的高实时数据传输,传输波特率1 Mbps。

相比目前行业内已广泛使用的Xilinx Zynq- 7015(双核Cortex-A9,主频800 MHz)进口SoC芯片方案,T3pro的CPU核心数更多、主频也更高,相应的计算速度也更快,结合AMP模式的应用并合理分配CPU各核的处理任务,使用更少的CPU芯片即可实现同样的功能;T3pro的外设资源同样不弱于Zynq-7015,只是Zynq-7015作为SoC芯片,片内还集成了47K的FPGA逻辑资源,这是目前国产同类芯片所不具备的。

1.2 SV/GOOSE采集板

SV/GOOSE采集板模件主要应用于智能装置,用以获取过程层SV数据和收发过程层GOOSE数据,采用兆易创新的GD32+紫光FPGA的硬件架构。GD32是一颗Cortex-M4架构的MCU处理器,集成了128K片上RAM,以及3072K的片上FLASH,通过芯片内置的SPI总线挂载FPGA,用以实现FPGA程序的引导加载和调试功能。SV/GOOSE采集板的绝大部分功能均由FPGA实现,包括:提供8路光纤以太网口,每个光口均可实现SV数据采集以及GOOSE收发功能;输入的差分PPS信号,用以同步主CPU的精确时钟,并且实现多SV/GOOSE板卡间的采样插值同步;LVDS总线用于SV/ GOOSE采集板与CPU板间的数据交互,SV经过二次同步插值后的采样数据以及GOOSE滤包后的数据均通过LVDS总线发送给CPU板进一步处理。

1.3 模拟量采集板

模拟量采集板模件主要用以实现常规装置的模拟量采集功能,同样采用GD32+紫光FPGA的硬件架构。MCU处理器GD32在这块板卡上只是起到FPGA程序的引导加载和调试作用,模拟量采集的功能均由FPGA实现。每块板卡提供最多4片AD芯片,每片AD提供8个模拟量通道,通过SPI总线分别接入FPGA,由FPGA负责定时触发AD采样转换以及读取AD采样转换后的模拟量数值,FPGA将所有模拟量通道的采样值组织打包成一帧报文后通过背板LVDS总线发送到CPU板以进行下一步计算处理。板卡输入的PPS差分信号主要用于多块模拟量采集板之间的采样同步,以保证同一台装置所有模拟量通道都在同一时间进行采样转换。

1.4 开入和开出板

开入板和开出板主要实现常规装置的开关量输入和输出功能,采用GD32作为主处理器,开入和开出功能均直接使用GD32芯片的GPIO实现。开入和开出板与主CPU板之间采用GD32内置支持的CAN总线进行通信,CAN总线没有主从之分,采用多主竞争式总线结构,任意一个节点可以向任何其他(一个或多个)节点发起数据通信,靠各个节点信息优先级先后顺序来决定通信次序,特别适用于传输开关量信息这样的小数据量,高实时性要求的场合。板卡输入的PPS差分信号,用于同步主CPU板的时间信息,以获取精确的开入变位时间。

2 软件平台设计

为适应现代电力系统的智能化、自动化发展趋势以及智慧能源的发展需求,对于继电保护等二次设备处理复杂问题能力的要求不断提升,使得装置软件趋于复杂[18],相应地,对于实时性、可靠性及稳定性要求更加严苛。为此,如何合理地布局和分配CPU资源,充分利用多CPU及多核架构优势是十分必要的。

2.1 CPU板软件架构设计

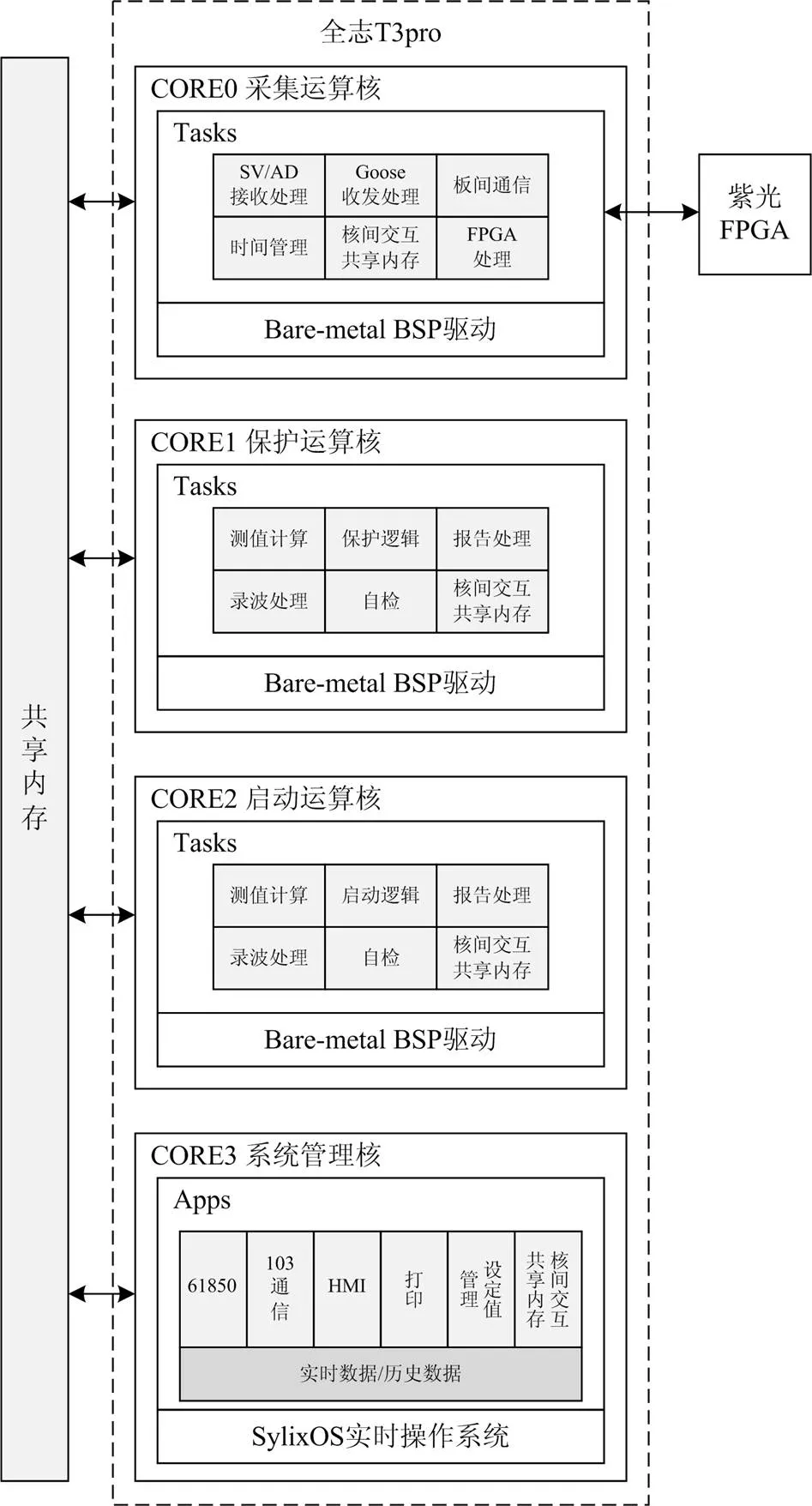

软件平台的设计以前文的硬件平台为基础,采用多CPU多核的分布式设计原则,T3pro拥有4个ARM Cortex-A7核心,分别标记为CORE0-CORE3,CPU以AMP模式运行,其主CPU的总体软件架构如图3所示。

图3 CPU板软件架构

1) CORE0是采集运算核,以Bare-metal裸跑模式运行,主要实现FPGA交互处理及其他外设的接口,以及输入数据的预处理、输出数据的执行;实现SV和AD数据的接收预处理、GOOSE收发处理、统一时间管理、板间背板总线通信(CAN和LVDS总线)、开入开出处理等任务。上电时CORE1-CORE3也是由CORE0负责引导加载,并且正常运行时CORE0也会定期监视CPU其他核是否运行正常,如果发现有异常则会触发看门狗复位整个CPU。

2) CORE1是保护运算核,以Bare-metal裸跑模式运行,实现保护逻辑计算功能,完成测量计算、保护逻辑计算、报告处理、录波处理、自检等任务。

3) CORE2是启动运算核,以Bare-metal裸跑模式运行,实现保护逻辑计算功能,完成测量计算、启动逻辑计算、报告处理、录波处理、自检等任务,与CORE1保护运算核配合,实现完整的保护功能。

4) CORE3是系统管理核,运行SylixOS操作系统,SylixOS是一款完全开源的国产自主硬实时嵌入式操作系统,采用多任务抢占式内核,具有优秀的实时性能,兼容POSIX编程标准。CORE3的具体功能以APP应用软件的形式运行在操作系统之上,主要包括:IEC61850通信(MMS和CMS)、HMI液晶显示、103通信、打印等功能软件。

以上T3pro 4个核的软件运行相互独立,核间采用IPC(Inter-Processor Communication)与共享内存配合进行数据通信[19],同时利用T3pro的MMU(Memory Management Unit)对各核使用的内存进行划分,这样各核的私有内存空间将对其他核不可访问,保证了内存数据的相对独立性,提高了软件系统的稳定性。

2.2 板间通信设计

在本平台中,板间通信主要是LVDS总线和CAN总线通信两种方式。

LVDS总线适用于大数据量高实时要求的通信方式[20-22],主要实现多CPU板之间的数据交互、CPU板与SV/GOOSE板之间SV数据和GOOSE数据的传输以及CPU板与模拟量采样板之间AD采样数据的传输。各板卡上的LVDS总线通信逻辑均由FPGA实现,最多支持16个节点,节点地址为0到15。通信采用总线竞争机制,FPGA会实时判别总线是否空闲。如果总线空闲,则占用LVDS总线并发送数据;如果总线已被占用,则等待总线空闲后再占用并发送数据;如果同时多个节点请求总线,则节点地址低的优先占用。

CAN总线适用于小数据量高实时要求的通信传输方式,主要实现CPU板与开入、开出板之间开关量状态的传送。开关量信息在状态发生变化后立刻通过CAN发送,后续参考GOOSE发送机制按照2 ms-2 ms-4 ms-8 ms-5 s 间隔重复发送,保证了CAN总线信息传输实时性和可靠性,同时减轻了通信负担。

2.3 板间同步设计

板间同步主要利用PPS信号实现,分为采样同步PPS和时间同步PPS,这两种PPS信号均由主CPU板上FPGA产生,其他板卡均为被同步端。采样同步PPS用于同步多块SV/GOOSE板卡和模拟量采样板的采样时刻,时间同步PPS用于精确同步板卡的时钟信息。

当前SV网络的组网方式分为星形组网和点对点[23],星形组网方式利用全站同步时钟源进行同步采样,采样值缓冲区报文中的采样计数SmpCnt相同的即为同一时刻的数据。但是由于一般装置计算所需要的采样频率与合并单元的采样频率(一般为4 kHz)并不一致,因此都需要进行二次采样插值,以获取装置所需采样频率的数据;而点对点方式下,装置与一个或多个合并单元点对点连接,各合并单元之间并未进行采样同步,需要根据SV报文的接收时刻和额定延时进行二次同步采样。为了保证模拟量数据处理的一致性,模拟量采样板也是采用合并单元的采样频率,即4 kHz进行采样,然后经过二次同步采样插值后再将最终的采样数据提供给CPU板[24]。二次采样均在各自板卡的FPGA中,根据采样同步PPS信号进行精确同步插值。

为了保证装置多板卡绝对时钟的一致性,平台设计了时钟同步PPS信号,该信号在绝对时钟0 ms时刻产生上升沿脉冲,结合LVDS和CAN总线的时间同步报文,可以实现多板卡之间的时钟完全同步。

3 平台的应用

基于本文的软硬件平台开发了应用于智能和常规变电站的线路、变压器、母差保护装置,及测控、合并单元、智能终端等二次设备。以110 kV变压器智能保护装置为例具体说明本平台的应用。

根据元件保护相关技术规范的要求,设计110 kV变压器智能保护装置硬件方案:除电源板、液晶板和总线板之外,选择使用2块CPU板和2块SV/GOOSE处理板,这样就按需组成了一台完整的变压器保护装置,对外提供16路过程层光口用于收发SV和GOOSE报文、3个站控层网口提供MMS服务、1个调试网口、1个时间同步信号输入(PPS或IRIG-B),以及1个RS232打印口。CPU板和SV/GOOSE采集板如图4所示。

图4 CPU板和SV/GOOSE采集板

110 kV变压器智能保护装置软件方案:采用双CPU板方案。一块为主CPU板,除实现保护功能外,还对外提供MMS通信服务,以及实现人机交互、打印、时间同步等功能;另一块为辅CPU板,只实现保护功能,并不对外提供其他服务。得益于T3pro的4核AMP方案,软件采用双CPU“保护+保护”架构,每块CPU板均实现完整的“保护+启动”逻辑功能。两个CPU板之间采用LVDS总线互联并交互数据,同时各CPU板卡上的T3pro也会对另一CPU板T3pro的重要数据进行实时校核,只有两块CPU数据及保护动作行为一致时,才表示保护装置工作正常。

包括110 kV变压器智能保护装置在内的基于本软硬件平台开发的二次设备均一次性通过了第三方检测,主要测试内容包括:保护功能和性能、动模、电磁兼容、网络压力、通信规约、网络安全等,各项检测均合格。其关键指标如下:保护动作电流精度和动作时间均满足或超过检测标准要求;在多主站通信中支持≥16个MMS客户端访问链接和≥12个报告实例;在网络压力和网络安全测试中装置无死机、重启、面板死机现象,无异常报文。测试结果表明其各项性能及关键指标均不输于基于进口芯片的同类装置。并且双CPU“保护+保护”架构相比当前多采用的“保护+启动”架构要更可靠、更稳定,可以极大地降低由于单CPU软件异常、单芯片故障、单粒子翻转错误等情况造成保护误动、拒动等装置异常的可能性。

4 结语

新一代自主可控保护装置软硬件平台很好地满足了当前智能变电站和常规变电站对二次设备的应用要求,在该平台的基础上实现了线路、变压器、母线保护以及测控、智能终端等一系列装置,且已通过了第三方检测,具备了入网资格,并且部分设备已参加试点站投运以及挂网试运行近一年。测试及实际运行情况均表明该自主可控平台稳定可靠,性能优异,随着自主可控国产化软硬件的逐步应用将极大增强变电站抵御外部风险的能力,为国家信息安全和产业经济安全提供可靠保障。

[1] 汪冬辉, 王志华, 陈明, 等. 多核 DSP 在就地化保护测试中的关键技术研究[J]. 电力系统保护与控制, 2020, 48(18): 138-145.

WANG Donghui, WANG Zhihua, CHEN Ming, et al. Research on key technologies of multi-core DSP in outdoor installation protection testing[J]. Power System Protection and Control, 2020, 48(18): 138-145.

[2] 陈彬. 通用非对称多核方案设计[J]. 计算机系统应用, 2021, 30(7): 277-282.

CHEN Bin. Design of general asymmetric multiprocessing program[J]. Computer Systems & Applications, 2021, 30(7): 277-282.

[3] 黄国睿, 张平, 魏广博. 多核处理器的关键技术及其发展趋势[J]. 计算机工程与设计, 2009, 30(10): 2414-2418.

HUANG Guorui, ZHANG Ping, WEI Guangbo. Key techniques of multi-core processor and its development trends[J]. Computer Engineering and Design, 2009, 30(10): 2414-2418.

[4] 李响, 刘国伟, 冯亚东, 等. 新一代控制保护系统通用硬件平台设计与应用[J]. 电力系统自动化, 2012, 36(14): 52-55.

LI Xiang, LIU Guowei, FENG Yadong, et al. Design and application of general hardware platform for new generation control and protection system[J]. Automation of Electric Power Systems, 2012, 36(14): 52-55.

[5] 黄雄, 刘晓铭, 郝永奇, 等. 智能变电站新型通用保护测控平台研制[J]. 电力系统自动化, 2014, 38(7): 66-69, 94.

HUANG Xiong, LIU Xiaoming, HAO Yongqi, et al. Development of a new and universal protection and measurement-control platform for smart substation[J]. Automation of Electric Power Systems, 2014, 38(7): 66-69, 94.

[6] 仲伟, 李亚锋. 面向中低压系统保护的嵌入式软硬件平台设计[J]. 江苏电机工程, 2010, 29(4): 4-7, 11.

ZHONG Wei, LI Yafeng. The design of the software and hardware platform for medium-low voltage relay protection[J]. Jiangsu Electrical Engineering, 2010, 29(4): 4-7, 11.

[7] 习伟, 姚浩, 蔡田田. 芯片化保护测控装置方案研究[J]. 电网与清洁能源, 2016, 32(11): 91-97.

XI Wei, YAO Hao, CAI Tiantian. Research on chip- based protection and measuring and control devices[J]. Power System and Clean Energy, 2016, 32(11): 91-97.

[8] 丁毅, 陈新之, 潘可, 等. 基于电力专用多核异构芯片架构的低压保护测控装置设计[J]. 南方电网技术, 2020, 14(1): 58-64.

DING Yi, CHEN Xinzhi, PAN Ke, et al. Design of low voltage protection device integrated with measurement and control function based on power dedicated multi-core heterogeneous chip architecture[J]. Southern Power System Technology, 2020, 14(1): 58-64.

[9] 阮青亮. 一种就地化保护装置硬件架构设计[J]. 电工技术, 2021(11): 116-117, 120.

RUAN Qingliang. Hardware architecture design of a local protection device[J]. Electric Engineering, 2021(11): 116-117, 120.

[10] CHAO Wujie, TANG Zhijun, LIN Guodong, et al. Construction of plug-and-play local protection system for smart substation[J]. Journal of Physics: Conference Series, 2021, 1754(1).

[11] BO Z Q, LIN X N, WANG Q P, et al. Developments of power system protection and control[J]. Protection and Control of Modern Power Systems, 2016, 1(1): 1-8.

[12] 周浩, 石磊, 彭涛, 等. 一起继电保护装置单粒子翻转软错误分析及应对措施[J]. 电力系统保护与控制, 2021, 49(7): 144-149.

ZHOU Hao, SHI Lei, PENG Tao, et al. Analysis and countermeasures of single event upset soft errors in a relay protection device[J]. Power System Protection and Control, 2021, 49(7): 144-149.

[13] ZHOU Hualiang, ZOU Zhiyang, XIA Yu, et al. Functional safety analysis and promotion for relay protection device platform[C] // 2019 8th International Conference on Informatics Environment Energy and Applications (IEEA 2019), March 16-17, 2019, Osaka, Japan: 186-192.

[14] 曾东华. 一种嵌入式系统软错误率评估方法[J]. 信息技术与信息化, 2020, 38(2): 118-120.

ZENG Donghua. An evaluation method of soft error rate in embedded system[J]. Information Technology & Informatization, 2020, 38(2): 118-120.

[15] 谢黎, 周华良, 于同伟, 等. 一种智能变电站新型双网冗余设备及实现[J]. 电力系统保护与控制, 2019, 47(11): 151-156.

XIE Li, ZHOU Hualiang, YU Tongwei, et al. A new network redundancy device for smart substation and its implementation[J]. Power System Protection and Control, 2019, 47(11): 151-156.

[16] 于同伟, 丁岳, 李良, 等. 用于就地化保护关键技术的 SoC设计[J]. 电力系统保护与控制, 2019, 47(21): 150-155.

YU Tongwei, DING Yue, LI Liang, et al. SoC design for key technologies of outdoor installation protection[J]. Power System Protection and Control, 2019, 47(21): 150-155.

[17] 丁毅, 陈福锋, 张云, 等. 基于背板总线的站域保护控制装置设计[J]. 电力系统自动化, 2014, 38(24): 102-107.

DING Yi, CHEN Fufeng, ZHANG Yun, et al. Design of substation-area protection and control equipment based on backboard bus[J]. Automation of Electric Power Systems, 2014, 38(24): 102-107.

[18] 陈波, 陈浩敏, 郭晓斌, 等. 一种通用继电保护软件平台的设计[J]. 自动化技术与应用, 2018, 37(5): 77-80, 97.

CHEN Bo, CHEN Haomin, GUO Xiaobin, et al. Design of a general software platform for relay protection[J]. Techniques of Automation and Applications, 2018, 37(5): 77-80, 97.

[19] 潘可. 多核异构模式下有管理的共享内存设计方法[J]. 单片机与嵌入式系统应用, 2021, 21(1): 27-33.

PAN Ke. Managed shared memory design on multi-core heterogeneous system[J]. Microcontrollers & Embedded Systems, 2021, 21(1): 27-33.

[20] 徐方明, 彭文才, 骆健, 等. 多点互联的高速通信背板总线研究[J]. 自动化仪表, 2020, 41(5): 54-57.

XU Fangming, PENG Wencai, LUO Jian, et al. Research on multi-point interconnection high speed communication backplane bus[J]. Process Automation Instrumentation, 2020, 41(5): 54-57.

[21] 张波, 李杰, 张海鹏, 等. 基于FPGA的LVDS传输链路的可靠性设计[J]. 电子器件, 2018, 41(5): 1237-1241.

ZHANG Bo, LI Jie, ZHANG Haipeng, et al. An LVDS transmission link reliability design based on the FPGA[J]. Chinese Journal of Electron Devices, 2018, 41(5): 1237-1241.

[22] 王政, 张宾. 一种基于FPGA的LVDS数据接收方法[J]. 数字技术与应用, 2019, 37(7): 115-116.

WANG Zheng, ZHANG Bin. LVDS data receiving method based on FPGA[J]. Digital Technology & Application, 2019, 37(7): 115-116.

[23] 电力自动化通信网络和系统第9-2部分: 特定通信服务映射(SCSM)-基于ISO/IEC 8802-3的采样值 DL/T 860.92—2016[S]. 北京: 国家能源局, 2016.

Communication networks and systems for power utility automation part9-2: specific communication service mapping (SCSM)-sampled values over ISO/IEC 8802-3 DL/T 860.92—2016[S]. Beijing: National Energy Administration, 2016.

[24] 王智勇, 裘愉涛, 董新涛, 等. 基于冗余通信的就地化分布式母线保护研究[J]. 电力系统保护与控制, 2020, 48(6): 158-164.

WANG Zhiyong, QIU Yutao, DONG Xintao, et al. Research on outdoor installation distributed busbar protection based on redundant communication[J]. Power System Protection and Control, 2020, 48(6): 158-164.

Software and hardware platform technology of an independent controllable relay protection device

ZHONG Wei, WANG Zhong, TAO Baozhen, YAN Hongfeng, WANG Hongyu

(Wiscom System Co., Ltd., Nanjing 211100, China)

There is an increasingly high level of requirement for high-speed smart substation data processing. Based on multi-core SoC and FPGA hardware and SylixOS embedded real-time operating system software scheme, this paper studies distributed, multi board relay protection device platform technologies. High-speed front-end data processing design of an FPGA is proposed and the LVDS high-speed bus and real-time CAN bus communication technology for multi board interconnection are discussed. A scheme of accurate clock synchronization of multi boards and sampling synchronization is proposed. Based on an asynchronous multi processing (AMP) software model, the architecture of multi-core and multi task parallel processing is studied and a technical scheme to improve reliability of the device is proposed. This employs data mutual checking between multi boards. Finally, based on the software and hardware technologies proposed, a series of relay protection devices that apply fully domestic components are developed and tested. The reliability and advantages of our independent and controllable technical solution are verified by field trial operations.

This work is supported by the National Key Research and Development Program of China (No. 2018YFB2100100).

independent and controllable; relay protection; RTOS; multi-core SoC; FPGA; backplane bus

10.19783/j.cnki.pspc.210802

国家重点研发计划项目资助(2018YFB2100100)

2021-07-01;

2021-08-16

仲 伟(1978—),男,通信作者,硕士,高级工程师,研究方向为电力系统继电保护;E-mail: flyzhongwei@ foxmail.com

王 仲(1983—),男,本科,工程师,研究方向为电力系统自动化;

陶保震(1984—),男,硕士,工程师,研究方向为电力系统控制保护硬件平台。

(编辑 葛艳娜)