一种使用相位合成结构的多相位输出全数字DLL电路*

2022-03-19孙昊鑫洪钦智管武梁利平

孙昊鑫,洪钦智,管武,梁利平

(1 中国科学院微电子研究所,北京 100029;2 中国科学院大学,北京 100049)(2020年1月14日收稿;2020年4月8日收修改稿)

在光通信等高速通信领域,电路的工作频率已经能够达到十几甚至几十GHz。多相位时钟生成电路被广泛应用在时钟数据恢复和时间数据转换等高速通信电路中。多相位时钟生成电路的核心结构一般由锁相环(phase locked loop,PLL)或延迟锁相环(delay locked loop,DLL)组成,PLL和DLL能够对时钟信号和数据信号实现相位锁定[1-2]。与PLL相比,DLL结构更简单,稳定性更好。DLL可以分为3种类型:模拟型DLL[3]、数字型DLL[4]和数模混合型DLL[5]。模拟型DLL和数模混合型DLL内部含有电阻和电容等模拟器件,与数字器件相比,模拟器件占据更大的面积且电源噪声和衬底噪声会对模拟器件的性能产生很大的影响,此外,这2种类型的DLL设计周期长、可移植性差。而数字DLL因为其使用数字电路设计,能够更方便地移植到其他工艺,设计时间短等优点逐渐成为研究的热点。

传统的多相位DLL一般为2种结构,一种为串联多条相同的延时线,每条延时线输出一个相位的输出时钟[6];另一种为使用两级DLL结构,第2级DLL产生中间相位[7-8]。使用串联延时线结构的多相位DLL产生N个时钟相位需要串联N个相同的延时线,本征延时为单一延时线本征延时的N倍,分辨率也下降为单一延时线分辨率的N分之一。使用两级DLL结构的多相位DLL相当于在第1级DLL的输入输出端并联上额外的DLL,面积和功耗显著增加。因此传统的多相位输出DLL大多使用模拟电路或定制电路来实现以提高精度,减小本征延时。

为解决模拟多相位DLL和半定制多相位DLL设计周期长,不易于移植到其他工艺,数字DLL精度不够,本征延时大等问题,提出一种工作频率在860 MHz~1.04 GHz,能够产生21个输出相位,使用标准单元设计的多相位ADDLL电路。针对数控延时线精度不高、本征延时大的问题做出改进,延时线通过调整两输入NAND门不同的输入信号改变延时,通过并联BUF减小本征延时,精度可以达到2~3 ps。相位合成模块接收2个时钟信号产生中间相位,级联多级相位合成模块可以产生多个中间相位。使用相位合成模块可以减少串联的延时线的级数,不需要第2级DLL产生中间相位,简化电路结构,减小本征延时,提高ADDLL的工作频率。使用基于SR锁存器的鉴相器,解决了传统鉴相器的“死区”问题。使用标准单元设计,可以有效地减少设计周期,便于结构调整和工艺移植。

1 多相位输出ADDLL结构

串联延时线结构的多相位DLL的最后一个输出out15与输入时钟进行鉴相,当out15延时达到一个时钟周期时,完成相位锁定,每条延时线输出一个时钟相位,由于延时线串联,本征延时、最小调节步长相互叠加,使工作频率下降。两级DLL结构的多相位DLL包含主DLL(MDLL)和子DLL(SDLL),MDLL产生相位差大的输出时钟,SDLL接收MDLL的输出,通过调节内部延时线的延时达到clk1和clk2的相位锁定,从而得到中间相位。因为MDLL和SDLL都需要使用延时线、鉴相器、控制模块等,电路结构复杂,导致芯片面积和功耗会相应增加。SDLL需要将2个相位差很小的时钟信号进行相位锁定,必须同时具有高精度、低本征延时等特点,设计难度大。针对传统多相位DLL电路存在的问题。本文提出的多相位DLL结构包括数控延时线DCDL、相位合成模块Blender、鉴相器PD、数字控制模块FSM和二分频模块。输入时钟信号CLK_IN每经过一条DCDL均产生一个中间信号,产生的中间信号两两输入到Blender模块中产生最终的输出相位。Out[21]作为反馈时钟输入到PD中与CLK_IN鉴相,FSM根据PD的鉴相结果为UP或DOWN调整DCDL的控制码,当PD的输出出现2次跳变或者控制码达到最大、最小值时locked信号拉高,表示相位已经锁定。为防止错误锁定,延时线初始延时被设置为最小,当延时线延时大于1/2时钟周期时,miss信号被拉高,表示DLL开始正常工作。多相位DLL结构如图1所示,其中图1(a)和1(b)为传统多相位DLL结构,1(c)为本文提出的多相位DLL结构。

与传统的多相位DLL相比,本文提出的多相位ADDLL使用的串联延时线级数减少,本征延时小,工作频率更高;不需要第2级DLL,使用由反相器组成的Blender模块代替,电路结构简单,面积功耗大大减小。

1.1 数控延时线DCDL

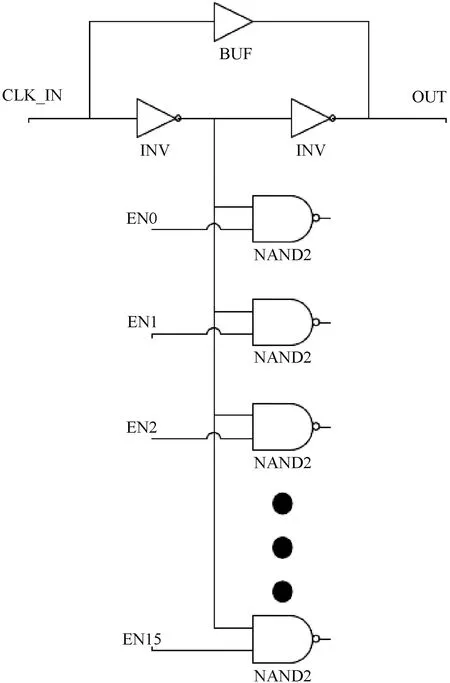

数控延时线用来调节时钟信号的延时大小。因为多相位DLL要求延时线精度高,本征延时小,所以延时线一般都采用全定制电路设计。通过对延时线的结构和其中MOS管的大小进行精确设计控制延时线的本征延时和精度,分为电压控制延时线[6]和电流控制延时线[9-10]。使用标准单元组成的延时线可以通过调整负载电容(插入dummy)的方式调整延时[11],但是这种结构的延时线本征延时大,不适于应用在多相位DLL中。本文使用的由标准单元组成的高精度延时线如图2所示。

图2 延时线结构

延时线由反相器INV、与非门NAND2和缓冲器BUF组成。NAND2的控制码EN0-EN15调整延时线的负载电容,从而调整延时线的延时。并联更多的NAND2门能够提供更大的延时调节范围,同时也会消耗更大的面积、增加本征延时。在输入输出端并联BUF可以减少延时线的本征延时。根据不同的工作频率,在设计过程中可以对并联的NAND2门的个数和并联的BUF门个数进行调整。本文使用并联16个NAND2门和1个BUF门的延时线。若并联1个BUF的2个INV延时为2tinv,控制码为0时NAND2门提供的延时为t1,控制码为1时NAND2门提供的延时为t2。当EN0-EN15为16′h0000时,延时线的延时最小为2tinv+16t1;当EN0-EN15为16′hffff时,延时线的延时最大为2tinv+16t2。

1.2 相位合成模块Blender

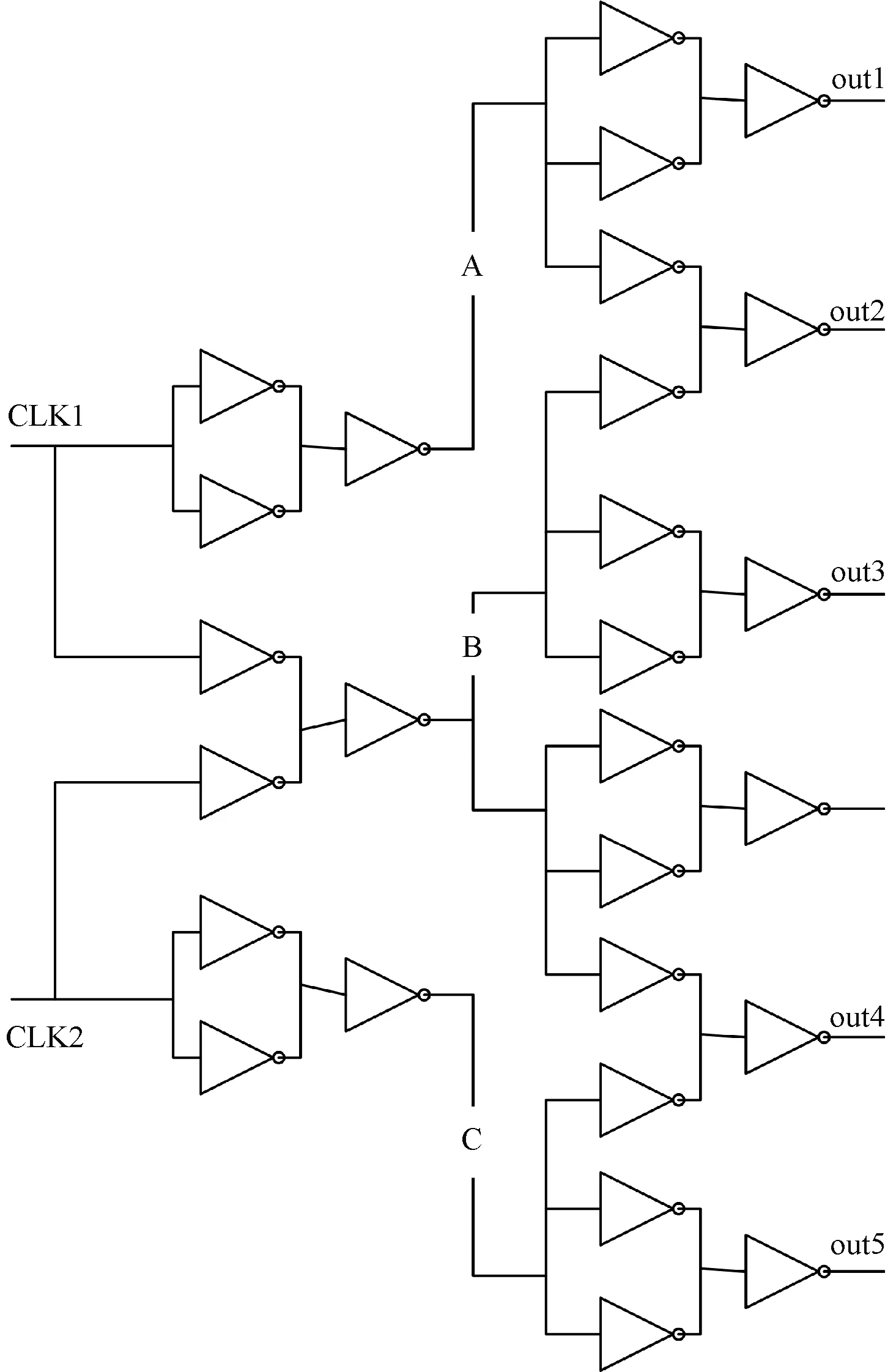

串联多条延时线的多相位DLL本征延时大,工作频率低。使用两级DLL结构,功耗和面积显著增加,并且第2级DLL需要特殊设计,以满足其对2个相邻的、相位差很小的时钟信号的锁定。考虑到以上情况,本文提出的多相位DLL使用相位合成模块产生多相位时钟,拥有本征延时低、面积小、功耗低等优点。相位合成模块[12]如图3所示。

图3 相位合成模块

CLK2为CLK1经过一级DCDL之后的输出信号。将CLK1和CLK2接入相位合成模块。CLK1和CLK2经过相同的延时分别得到信号A和信号C。信号B由CLK1和CLK2共同驱动,则信号B的相位位于信号A和信号C之间。将信号A和信号B、信号B和信号C作为输入连接相同的结构,可以得到不同相位的输出out1~out5。可以级联相位合成模块以生成更多的输出相位。

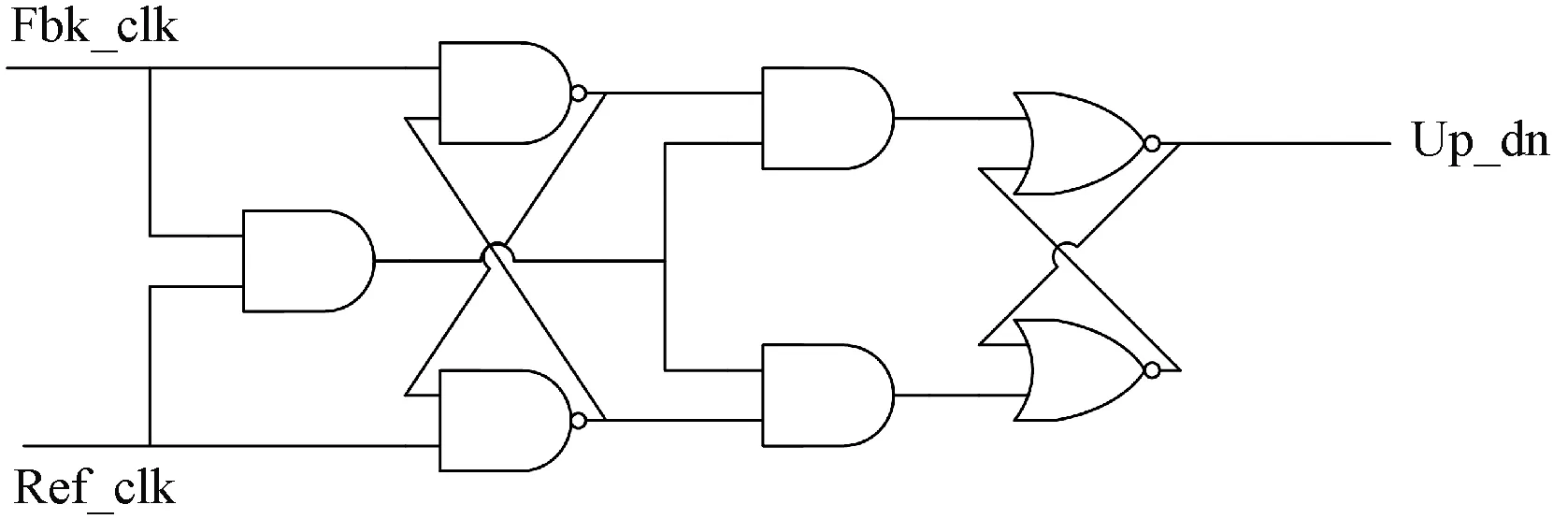

1.3 鉴相器PD

鉴相器是DLL的最核心部分之一,鉴相器和延时线结构共同决定了DLL的分辨率。简单的标准单元组成的鉴相器基于D触发器结构,分别将反馈时钟和输入时钟接入D触发器的数据端和时钟端,若反馈时钟超前输入时钟,鉴相器输出1;若反馈时钟滞后输入时钟,鉴相器输出0。当输入时钟和反馈时钟相位差很小时,D触发器进入亚稳态,鉴相器不能正常工作。本文使用的鉴相器由2个SR锁存器和一些标准单元组成,如图4所示。

图4 鉴相器结构

2个SR锁存器基于反馈时钟和输入时钟的相位差输出PD的鉴相结果,中间的标准单元组成复位信号。

1.4 数字控制模块FSM

数字控制模块根据PD输出的结果调整延时线的状态码,同时输出锁定信号lock以及失锁信号miss。

初始状态FSM输出控制码Sel=16′h0000,延时线的延时最小,Sel采用温度计编码。此时无论PD输出信号Updn为0或1,下一个时钟上升沿到来时,Sel+1(增加一位1的个数)。当Updn=1时,Miss信号拉高,说明不会出现错误锁定。Miss=1,FSM根据Updn信号调整Sel中1的个数。Updn=1,如果Updn_reg=0,则CNT+1,如果CNT=2,则锁定;如果CNT不为2或者Updn_reg=1,那么Sel+1,Updn_reg=1,延时增大;Updn=0,如果Updn_reg=1,CNT+1,如果CNT=2,则锁定;如果CNT不为2或者Updn_reg=0,那么Sel-1(减少一位1的个数),Updn_reg=0,延时减小。锁定之后Sel信号不再改变。Sel=16′hffff,输出失锁信号,表示工作频率过低;Sel=16′h0000,输出失锁信号,表示工作频率过高。

2 后仿真测试结果与比较

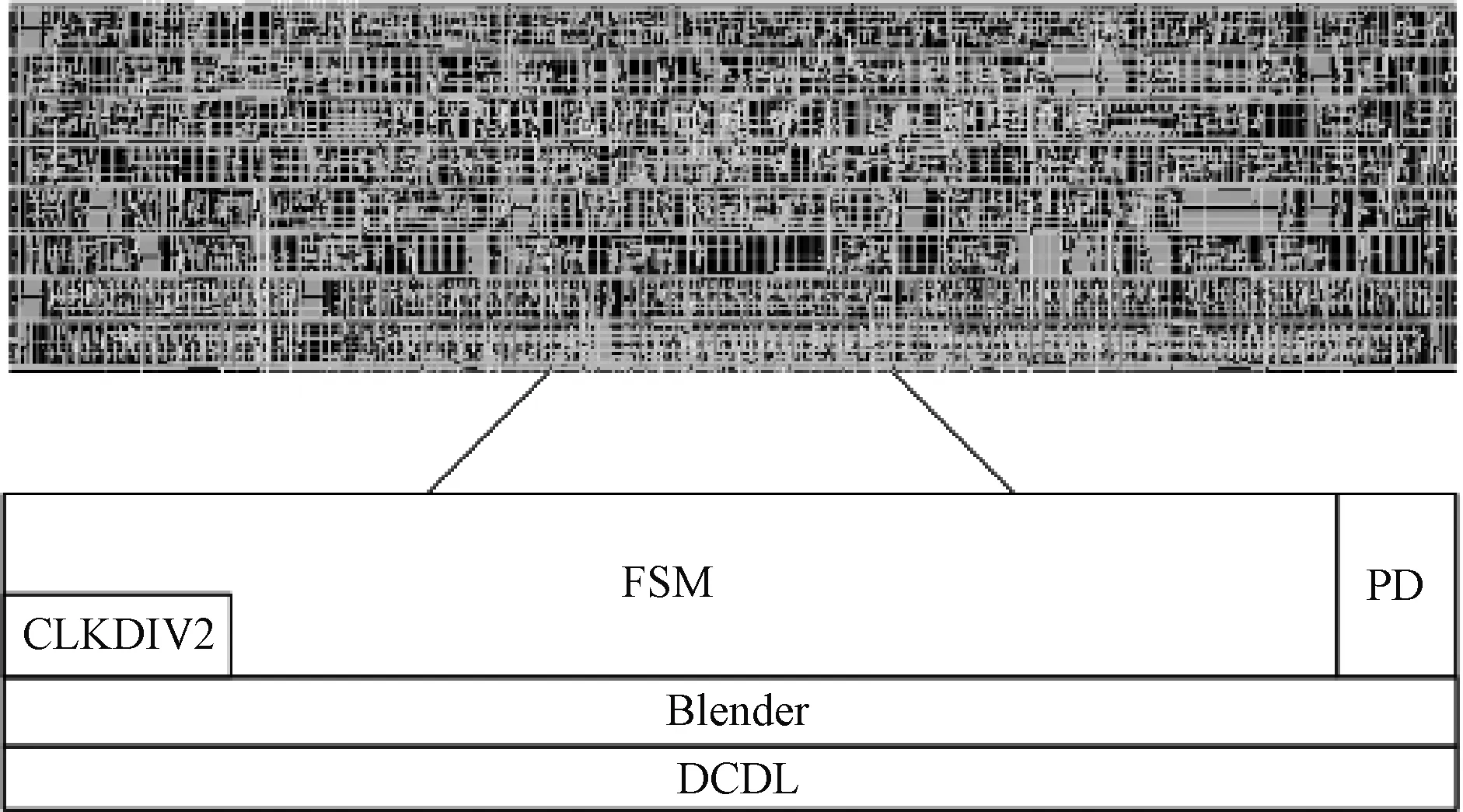

本文提出的多相位ADDLL采用SMIC 55 nm CMOS标准工艺,版图如图5所示。

图5 DLL版图

延时线DCDL和Blender使用手工摆放,保证每条DCDL和Blender受布局布线影响小,其他模块使用ICC自动摆放。在SS工艺角下,供电电压1.2 V,版图面积为90 μm2×19.2 μm2,分辨率为13 ps,1 GHz时,功耗约为2.66 mW。使用icfb提取版图的寄生参数信息在HSPICE中进行后仿真。

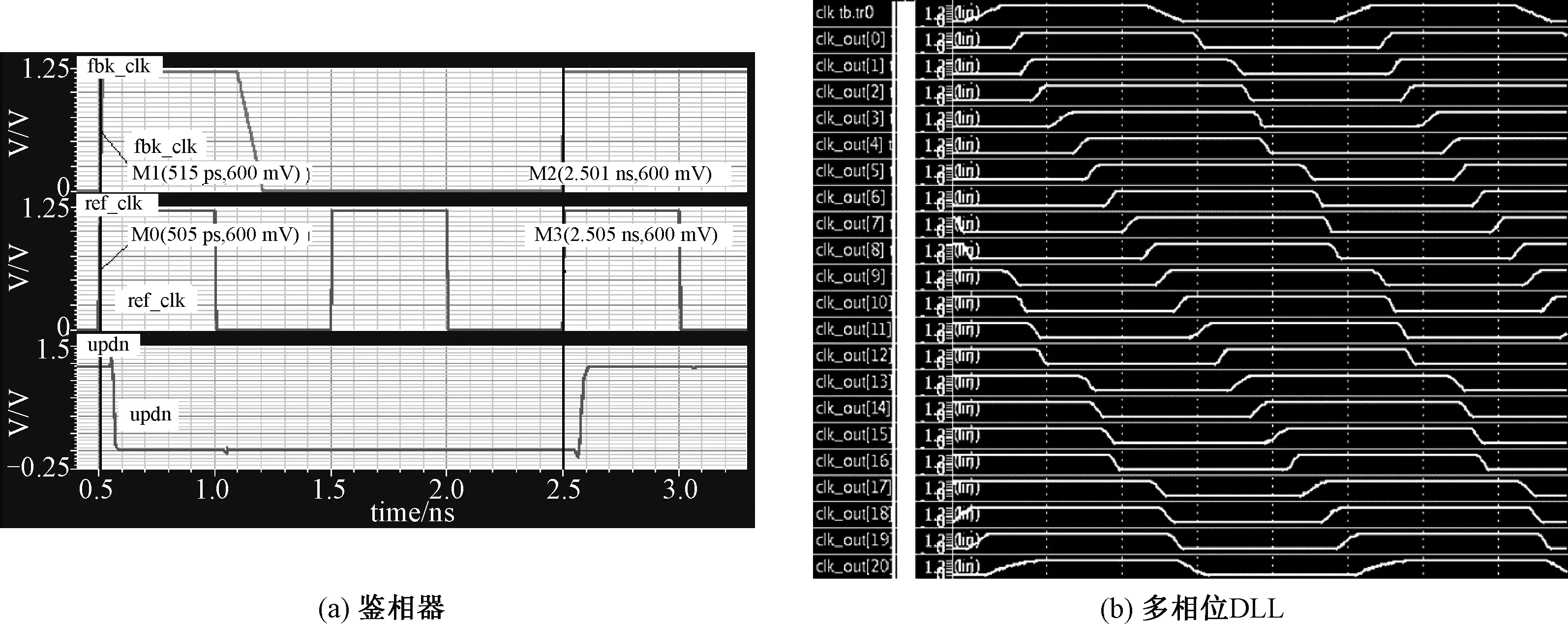

图6(a)是鉴相器的后仿真结果,6(b)是多相位DLL仿真结果。

图6(a)中ref_clk表示输入时钟,fbk_clk表示反馈时钟。由仿真结果可以看出,ref_clk和fbk_clk相位差在4 ps时,鉴相器仍然可以正常工作,即本文使用的鉴相器精度相比传统鉴相器有明显提高,可以有效的避免传统鉴相器存在的“死区”问题。

图6 后仿真结果

图6(b)是本文提出的ADDLL在1 GHz下的HSPICE后仿真结果。仿真结果表明,在SS、TT、FF工艺角下,该电路均可以工作在860 MHz~1.04 Ghz的频率范围内,并且能够产生分布比较均匀的多相位时钟输出。

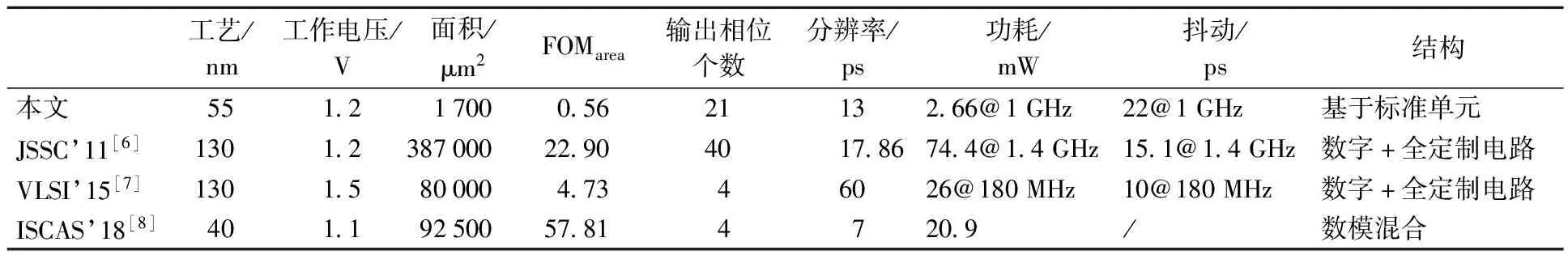

表1是本文提出的多相位ADDLL电路与几种现有的多相位DLL电路的比较。

表1 本文设计的多相位DLL与其他设计的对比

3 结论

本文针对目前多相位DLL设计过程中存在的大面积、高功耗、设计周期长等问题,提出一种基于标准单元设计的多相位输出ADDLL。使用相位合成模块产生多相位输出,减小串联延时线的级数,不需要额外的控制逻辑,有效地减小面积和功耗。本征延时减小使ADDLL可以工作在更高的工作频率下。使用标准单元设计,可以直接接入到数字电路中。对工艺变化不敏感,让设计可以更好地移植到其他工艺,也大大缩短了设计周期。本文提出的ADDLL可以工作在860 MHz~1.04 GHz,产生21个输出时钟相位,也可以级联多级相位合成模块产生更多相位输出。

猜你喜欢

杂志排行

中国科学院大学学报的其它文章

- DFT mechanistic insight into the modular strategy involved in the palladium-catalyzed synthesis of cyclopentenones from α,β-unsaturated acid chlorides and alkynes*

- 脱水诱导基因RD特性及功能*

- 对线性幺正光学加密系统的选择明文攻击*

- Ab initio simulations of NO adsorption on hematite(0001)surface: PBE versus PBE+U*

- 基于B/S架构的激光雷达电力巡线可视化管理与分析系统*

- 基于低秩和一维稀疏矩阵分解的多通道SAR-GMTI方法*