模拟电路优化设计理论与关键技术研究

2022-03-17董晶

董晶

(山西职业技术学院,山西太原,030006)

0 引言

模拟电路主要指对模拟信号进行传输、变换、处理、放大等操作的电路。随着电子技术、网络技术的飞速普及,模拟电路的故障处理、优化策略等逐渐成为影响电子系统正常运行的关键。模拟电路主要分为标准模拟电路以及专用模拟电路等类型,电路中主要包括放大电路、信号运算和处理电路以及振荡电路等,具有函数取值无限多、模拟信号具有连续性等特征,在实际的故障诊断和电路优化环节具有较大的难度[1]。如何选择恰当的模拟电路优化方法和技术,是能否顺利开展模拟电路优化设计的关键。因此,本文概括了模拟集成电路优化设计流程,针对模拟电路优化设计中的关键方法、技术等进行总结,旨在为模拟电路优化相关研究提供借鉴。

1 模拟集成电路优化综合流程

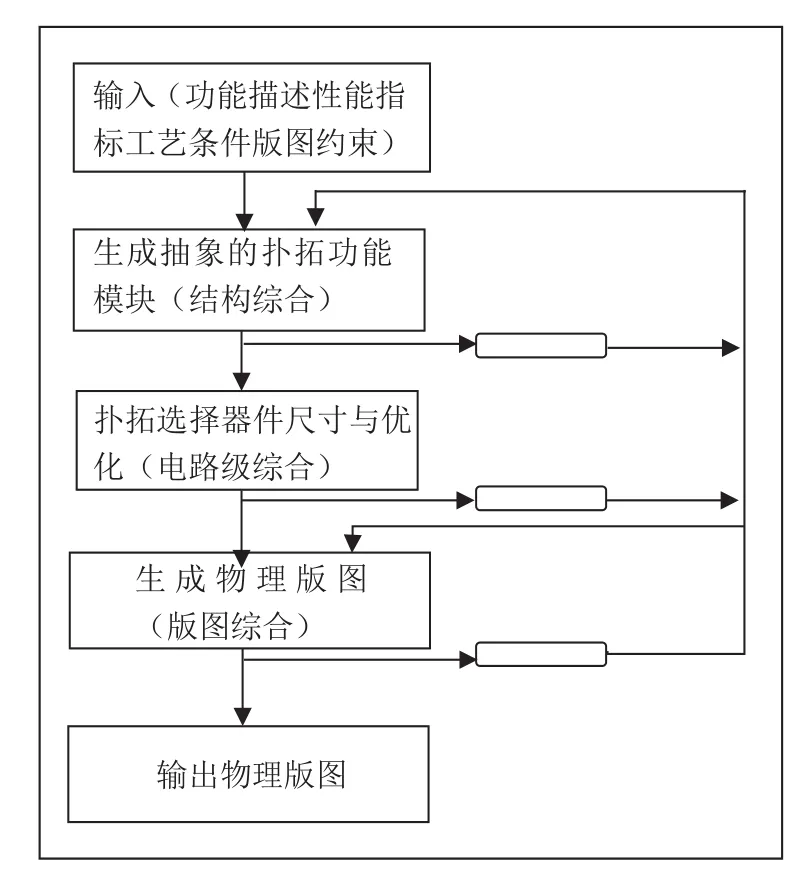

模拟电路优化设计理论可以从多方面进行优化设计,如理论、行为设计、结构、功能等,该模拟电路优化设计理论的思想具有很好的发展前景。模拟集成电路优化综合可以分为两部分:物理综合,即模拟集成电路的高层综合,其又可以分为两部分结构综合和电路级综合;结构级综合,该综合是将电路的扑拓结构利用数学或算法进行行为描述,然后在确定扑拓结构和使用器件的尺寸[2]。如图1所示为模拟集成电路优化设计流程。

图1 模拟集成电路优化设计流程

1.1 模拟集成电路高层综合方法

传统的模拟集成电路多采用自上而下的设计方式,而在模拟电路优化设计专业电路设计软件平台展开的结构级、功能级、电路级等方向的优化设计,同时这些都属于高层综合方式[3]。其中,要了解用户的对电力功能、性能指标等方面的需求,然后在根据数学或算法在进行程序语言描述。

1.2 物理版图综合方法

物理版图综合方法是在高层综合法之后进行的,它的工作主要取决于器件尺寸和工艺条件,在此基础上才能设计出规则正确的物理版图。它的功能包招模块和相关器件的布局、布线等有一定的关系,并且还会涉及到一些电源和连接地点。在以往的传统模拟单元版图当中,主要依据过程模块,需要先将电路版图整体进行软件编码,录入相关信息数据,然后才能生产版图。在模拟电路优化理论中,为了得到最佳性能,电路器件尺寸的变化需要对相应的版图结构作比较大的调整。

模拟电路优化设计的最终结果与版图有恨到关系,所以想要得到理想的设计效果,需要认真遵循相关原则,主要为以下两个原则,即令产生的电路尽可能满足全部性能标准;使版图能够最大程度实现紧凑。这样的措施需要定制版图,能够运用宏模式版图设计策略进行操作。在进行操作处理时,应当将单个或者特定的结构租组件展开优化升级。与此同时,关注模拟期间和专门器件组。由于它们之间参数存在一定差别,所以即便是运用同组参数也会出现不同的几何变化。例如两个匹配的晶体管能够用集合型、堆积型进行布置。针对系统结构出现的宏观变化,需要针对定制板块的某项参数单元进行实际版图设计。为了避免生产过程中出现负面情况,需要对关键器件进行细心的维护。在定制模拟电路优化设计电路优化设计版图的综合工具中,不论处理怎样的宏单元,都需要保证布线和放置的合理性和最优化,并且合理选择几何变化,运用布线进行连接。

2 模拟集成电路优化设计关键技术

当前的电路设计实用的软件有很多,主要有Proteus、Altium Designer以及 Multisim等软件。首先是Proteus软件,这项软件能够进行电路图设计、PCB布线和电路仿真。Proteus软件分为两个模块,分别为ARES和ISIS模块,ARES用来制作PCB,ISIS用来绘制电路图和进行电路仿真。其次为Altium Designer软件,这个软件通过把原理图设计、电路仿真、PCB绘制编辑、拓扑逻辑自动布线、信号完整性分析和设计输出等技术的完美融合。最后为Multisim软件,这个软件可以进行电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。模拟集成电路优化设计可以通过以上软件进行操作,可以进一步减少人为干涉,实现自动控制。当前,对软件工具主要进行以下三方面的优化[4]。

2.1 基础优化

在进行模拟电路优化设计时要从基础出发,清楚的了解用户的需求,再根据系统优化算法来制定出模拟电路优化设计的具体参数。其中,数字优化技术是最常见的一种方式,但是其存在许多问题。

(1)在设计电路时先制定好起始点,起始点是电路良好工作的基础,如出现故障会引起人力、财力等方面的问题。

(2)输入约束,在优化设计时要确定好该线路目标的性能。

(3)系统优化是比较繁琐的,它包含多个部分的优化,因此时间较慢。

(4)在进行优化设计时,需要清除的了解系统和优化算法,这样可以提高模拟电路的精确度和安全性。

(5)在进行优化设计时,需要借鉴之前模拟电路的设计经验。

2.2 版图优化

模拟电路的版图优化需要从数字领域出发,通过标准单元、门阵列、参数化单元方法等来进行操作,但其受版图因素的影响较大[5]。模拟阵列需要先设计好器械的尺寸、配置等,然后再从单个元件阵列变化到电路阵列,同时可以适当地规划一个或更多级的互相连接设计电路。但是也容易出现一下问题:缺乏高性能模拟电路所需的设计灵活性,实现的部分较小;该设计方式中未使用到元件,同时还会浪费电路的硅片面积。

标准单元解决了硅片面积浪费的问题,它的工作是在DA的基础上提前设计和布置好的,想要实现单元功能需要调集必需的单元然后布局和布线才能进行操作,因此硅片只用在所需单元,不会造成浪费。将其与模拟阵列相比,其周转次数更长。并且两者都不具备良好的灵活性,在设计灵活性受到一定的局限。虽然标准单元已经在当前的数据领域当中广泛使用,并且取得初步成功,但是仍然会在模拟电路设计中受到限制。因为建立和维持丰富的单元库以能提供宽范围的最多的技术规范具有一定的难度。

另外,由于以上两种方法都没有切实均未考虑到制造工作可能带来的一些影响,进而降低了实际效果。模拟参数化单元的使用需要将版图的设计方法作为基础,它的参数化丹玉与千标准化单元具有一定的相似度,只是其参数化单元能够允许依据实际需求功能来定值单元,提供的灵活度主要与各个自模块生成器的复杂程度有一定的关系。将一系列的参数进行输入,进而生成了单元版图代码。通过运用这样的方法,能够提升电路元件值的连续性。这样的结果是上述两种方法不能够达到的。但是这种方法在混合模块拓扑与混合布局配置方面仍然会对模拟电路具有一定的限制,并且这种方法与阵列和标准单元一样,未能充分考虑到制造工艺对其造成的附加影响。

2.3 知识优化

(1)层次式方法。

在模拟电路的优化设计过程中,每个模块会出现一部分的混合信号。在针对数转换器这样较为复杂的模拟宏模块设计过程中,通常情况会会将模拟模块拆分成多个子模块。这类子模块的定义源自于初始模块中的原始定义。完成定义的导出之后,需要将每个子模块进行独立设计,或者将其拆解成更多更小的子模块。将这样的向下层次化分解继续操作,直至分解后的子模块大小能够满足物理实现。然后将其自上而下进行综合,随着再由下向上的版图实现,并且进行设计验证。但是这个过程需要一定的制造成本,所以在进行设计验证的时候需要保持谨慎与详细。并且在设计内容需要保障全部设计功能都能在制造容带差之内。如果设计过程中某一项不能满足规定标准,便需要重新进行设计。

(2)固定拓扑方法。

这种方法主要是备用固定电路拓扑当中的计算器件合理尺寸,此类股东的器件电路拓扑与比艾丁器件尺寸大小所依据的理论都被存储在同个知识库里面。将知识的基础作为出发点,固定拓扑方法会对设计灵活度造成一定的限制和约束,因为这种方法的实施是将器件尺寸当做合法设计变量,。而这种方法的另一个弊端便是当一个新的拓扑加入之后,会付出一定的代价,这是由于在相似的拓扑中出现了重复知识的低效利用。

(3)混合层次式和固定拓扑的方法。

由层次式和固定拓扑结构组合而成的系统附加了设计灵活度一拓扑更改,这样的设定令电路库变小,但是电路特性范围却得到了扩展,但是他们的灵活性步入全层次式系统。