集成电路测试系统高速数字通道校准装置架构设计∗

2022-03-14黄俊杰姚俊杰

胡 勇 黄俊杰 姚俊杰

(中国船舶集团有限公司第七○九研究所 武汉 430205)

1 引言

数字通道测试速率的不断提升以及单块板卡的集成度越来越高是当今大规模集成电路(SOC)测试系统发展的趋势,现如今主流SOC测试系统数字通道的测试速率大多已达到8Gbps。国内已有多家科研院所配备了此类SOC测试系统几十台套,而且今后高速SOC测试系统在国内科研院所的应用会越来越多。然而,由于测试系统高速数字通道校准的特殊性以及缺少对高速数字通道校准方法及技术规范的研究,当前高速数字通道普遍缺乏可靠的量值溯源途径,从而导致SOC测试系统无法得到完整的校准。因此,急需开展集成电路测试系统高速数字通道校准技术的研究。

本文提出了一种集成电路测试系统高速数字通道校准装置架构设计方法,研建由高速通道切换系统、通用测量仪器、校准接口板及校准软件组成的集成电路测试系统高速数字通道校准装置。相较于传统通过眼图定性观测高数数字通道传输信号质量变化的方式,该校准装置可定量测量考核高速数字通道性能的各类参数,且具有通用、多通道测量、便携、自动化等优点[1~10],解决测试速率达8Gbps高速SOC测试系统的量值溯源,促进并完善国防微电子量传体系。

2 集成电路测试系统高速数字通道校准装置架构设计

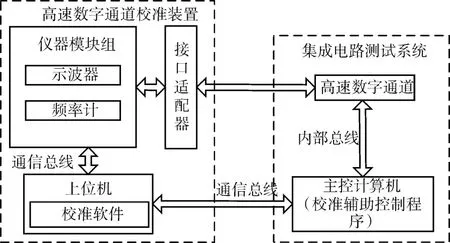

本文的校准对象是集成电路测试系统高速数字通道,针对校准对象的特点以及所使用的校准方法,研建较为通用的高速数字通道校准装置,在分析当前高速数字通道的性能指标的基础上,选择合适的仪器设备构建校准装置,保障校准装置所复现的量值范围、不确定度要求等性能指标,能够保障高速数字通道的量值溯源性。校准装置架构如图1所示。

图1 集成电路测试系统高速数字通道校准装置架构图

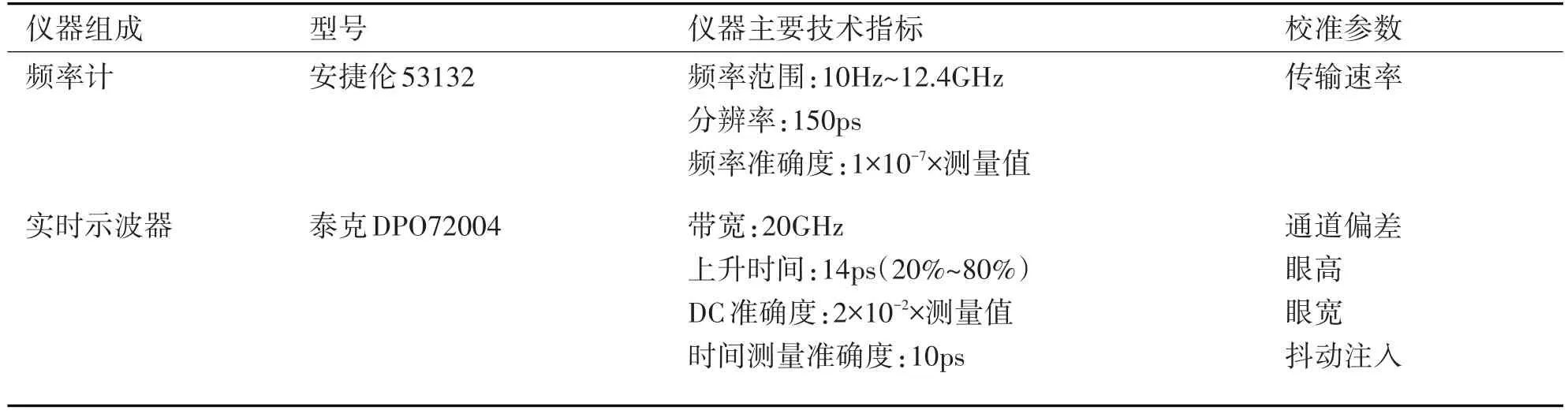

校准装置包括仪器模块组、接口适配器以及校准软件等部分。仪器模块组采取高性能的通用台式仪器,为了实现对输出数据传输速率、通道偏差、眼高、眼宽、抖动注入等参量的有效校准,选用了性能满足要求的频率计、示波器等通用仪器,具体的技术指标见表1。

表1 校准装置仪器组成

由表1看出,采用安捷伦的53132频率范围到12.4GHz,可以满足传输速率的测量要求。选用的泰克示波器DSA72504带宽20GHz,大于被测信号的5倍带宽,幅度准确度及时间测量准确度较高,可以满足通道偏差、眼高、眼宽、抖动注入的测量要求。

校准软件运行于上位机中,上位机通过通信总线分别与仪器模块组及测试系统的主控计算机建立通信连接。校准软件控制仪器模块组测量指定通道上的信号,并向校准辅助控制程序发送指令,控制测试系统数字通道运行于指定状态。

接口适配器由高速通道切换系统和校准接口板组成,用于高速数字通道与通用仪器之间的无缝自动切换,在保证校准装置技术性能的同时,实现所有参数的全自动校准,拓扑结构2×16,带宽大于20GHz,抖动小于20ps。

3 高速通道切换系统设计

在高速信号的切换应用中,信号完整性是研究的重点和难点。校准的需求是要通过接口适配器后,能够使信号尽可能完整地从源端传输到测量端,并且具有复现性。事实是,任何的电路和线路都有带宽限制,而一个完整的高速信号具有无穷的多次谐波,因此高速信号在通过接口适配器的过程中,不可避免地会对高次谐波进行衰减。同时,高速信号在切换的过程中对切换链路的要求较高,如阻抗的一致性,线路的连续性等,而这些都会影响信号的完整性。

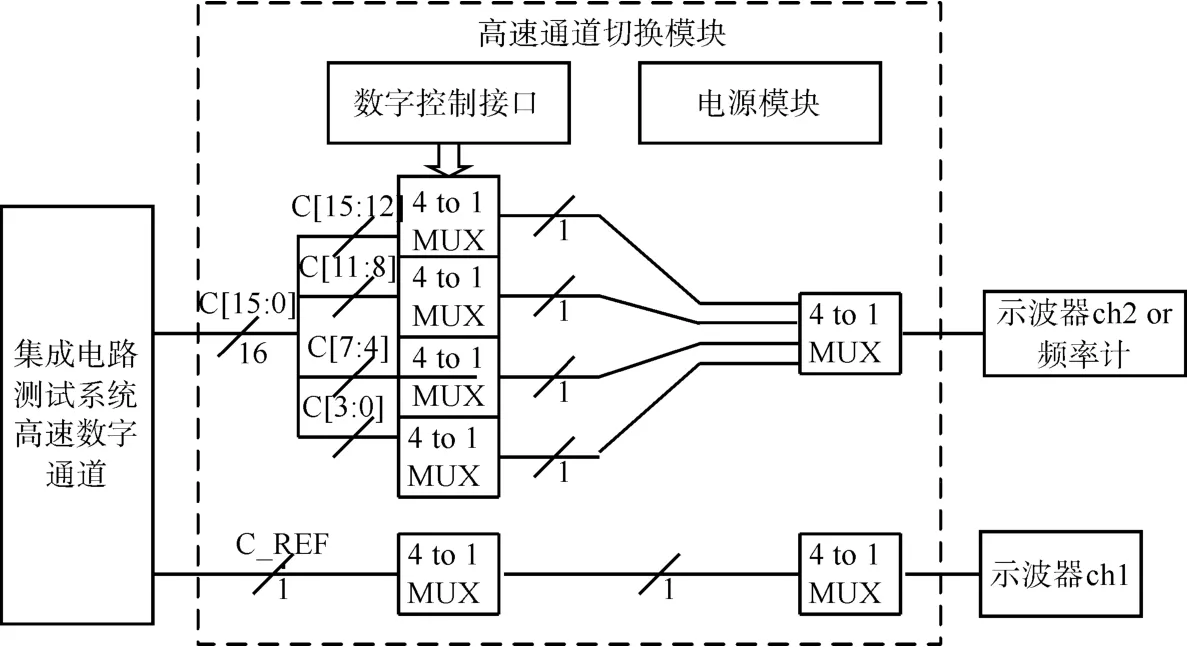

高速通道切换模块总体框图如图2所示,主要分为高速信号通路、数字控制信号通路及电源模块。高速信号通路为其核心部件,通过高性能射频开关、高性能射频线缆及连接器组成,高速信号路径无需经过PCB单板,避免通过PCB的信号路径阻抗不连续引入额外的串扰、插损、回损等信号完整性的问题。考虑满足高速信号测设需求,采用较简洁的拓扑连接关系,避免使用有损信号的功率分配器或者一分多的连接头等器件,但测试时需要采用人工手动切换通道的方式更换不同的测试仪器。数字控制接口主要包括PC控制接口、高速开关选择控制逻辑电路。电源模块主要提供数字控制及高速开关所需的稳定工作电压。数字控制接口及电源模块采用PCB单板的方式实现。

图2 高速通道切换模块总体框图

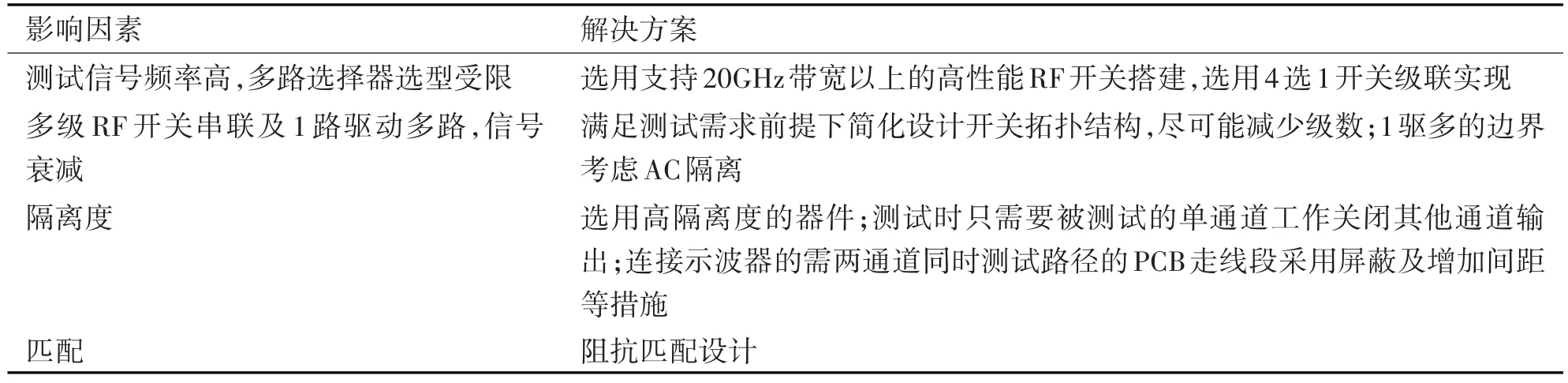

高速通道切换系统对校准装置性能的主要影响因素及解决方案如表2。

表2 影响因素及解决方案

4 校准接口板设计

在高速信号测量中,校准接口板的设计是一个非常重要的环节。这是由于当信号传输速率很高时,阻抗不匹配、介电材料损耗、传导损耗、串扰等因素都将导致信号衰减。在设计时应通过合理的布线保证线路之间没有相互干扰。考虑到高速信号的特殊性,需要在接口板的设计过程中从信号的布线、电磁干扰(EMI)、信号的完整性、信号的衰减、可靠性等多个方面综合考虑[11~13]。

1)通孔设计

连接Pogo Pin的通孔是测试系统和校准接口板连接的第一个阻抗突变点,通孔设计是否合适,将直接影响校准接口板的性能和最终测量结果。因此需要精细设计通孔的参数,尽量减少通孔产生的寄生电容和电感,减小对高速信号的影响。

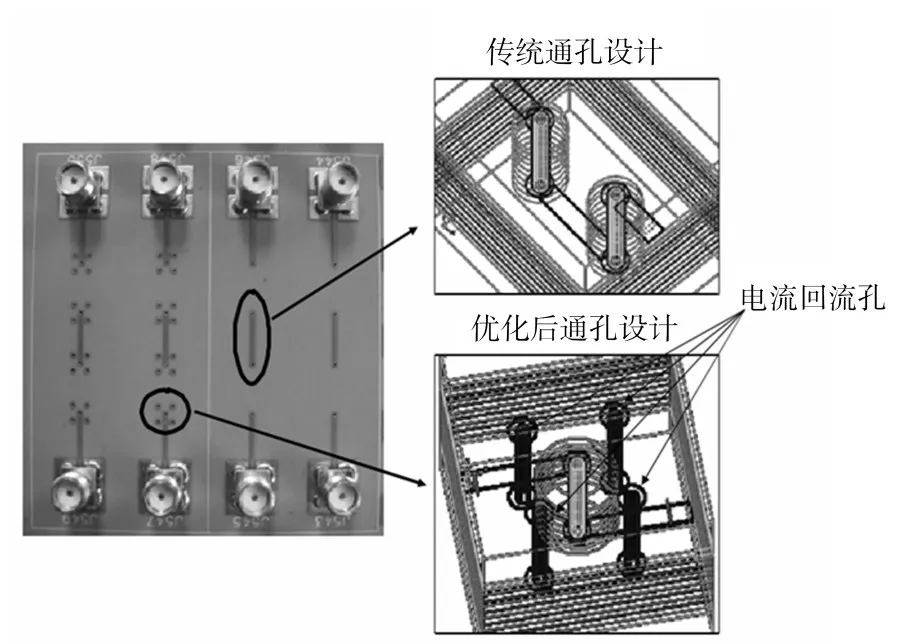

对多层板而言,当信号从通孔经过时,必须找到返回电流的路径。因此比较好的方法是在每个信号通孔附近提供接地的通孔,使返回电流在邻近的通孔流过。由于测试系统通道分布紧密,相应在校准接口板上引出的信号也排列紧密,为了减少相邻信号的串扰,本文采用优化的设计,在每个信号通孔周围分布四个对称的电流回流通孔,既保证了PCB上不同信号之间的安全距离,同时尽可能减小了串扰问题,同时SMA的布局应尽可能靠近通道,使得PCB上的走线尽可能短,如图3所示。

图3 通孔的优化设计

2)布局设计

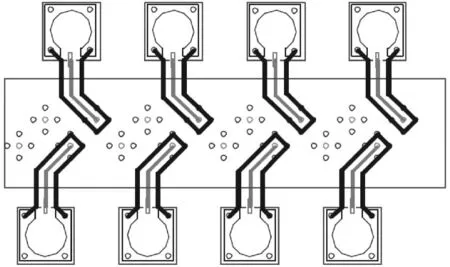

校准接口板设计连线示意图如图4所示。将测试系统同一块高速通道板上的一组数字通道(例如:一组16个数字通道)用50Ω阻抗匹配最短等长导线通过SMA接头引出,并选取其中一个通道作为参考通道。将测试系统其余数字通道每间隔2个通道用50Ω阻抗匹配最短等长导线通过SMA接头引出。所有的回流孔连接到SMA接头的地。

图4 校准接口板设计连线示意图

5 结语

集成电路测试系统高速通道校准装置的不确定度主要来源于通用测量仪器、高速通道切换系统以及校准接口板等引入的误差,本文通过选用带宽达20GHz以上的示波器、高频切换开关、高频接头、高频线缆等组件,同时对校准接口板与测试系统弹簧针Pogo Pin连接的通孔尺寸和钻孔工艺进行了优化设计,确保PCB布线尽可能短,同时设计校准接口板50Ω阻抗匹配,确保高速信号经由校准装置引入的不确定度尽可能小。

本文通过分析集成电路测试系统高速通道校准方法、集成电路测试系统高速通道校准装置架构设计、高速通道切换系统设计、校准接口板设计等几个步骤,成功设计出集成电路测试系统高速数字通道校准装置架构。经过试验证明,基于该架构可以构建出集成电路测试系统高速数字通道校准装置,并完全满足设计目标。集成电路测试系统高速数字通道校准装置具有通用、便携、自动化、高集成度等特点,具有很高的应用价值,填补了国内空白,一定程度上提高了微电子计量的技术水平。