一种半导体芯片的设计方向研究

2022-02-25杨志伟

杨志伟

(吉林工业职业技术学院智能制造学院,吉林 吉林 132013)

1 引言

随着半导体芯片的蓬勃发展,晶闸管芯片因其具备高阻断电压、大电流条件下工作、容量大和体积小等优点而在功率半导体器件中有着不可或缺的地位。

笔者认为,在这些优势的基础上,进一步提升晶闸管芯片触发电流的能力及其动态特性,将成为其未来的发展的方向[1]。由于根本的解决方案主要取决于其芯片结构的设计,因此中心门级和多层的P/N 型半导体是当前最为有利的设计方案[2]。

2 晶闸管芯片的基本结构

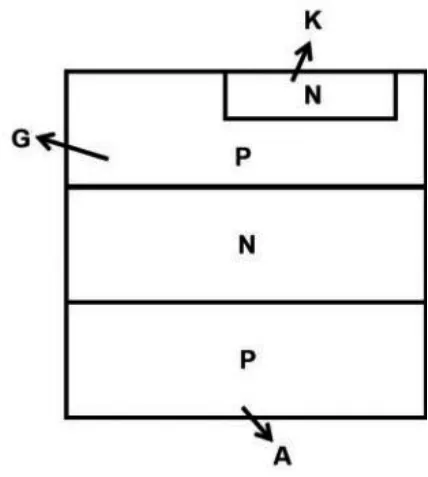

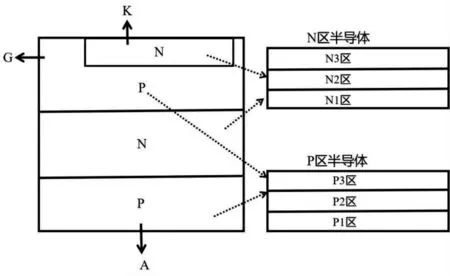

图1为晶闸管芯片的基本结构,其结构设计基础主要为P/N/P/N。由于图1主要为单向晶闸管芯片结构,因此其中A 代表阳极、K 代表阴极、G 代表门极;在双向晶闸管芯片的情况下,G依然继续代表门极,而与门极同一面的电极(包括阴极和阳极)则一般使用MT1 极来代表,另一面(也包括阴极和阳极)常使用MT2 极来代表。

图1 晶闸管的基本结构

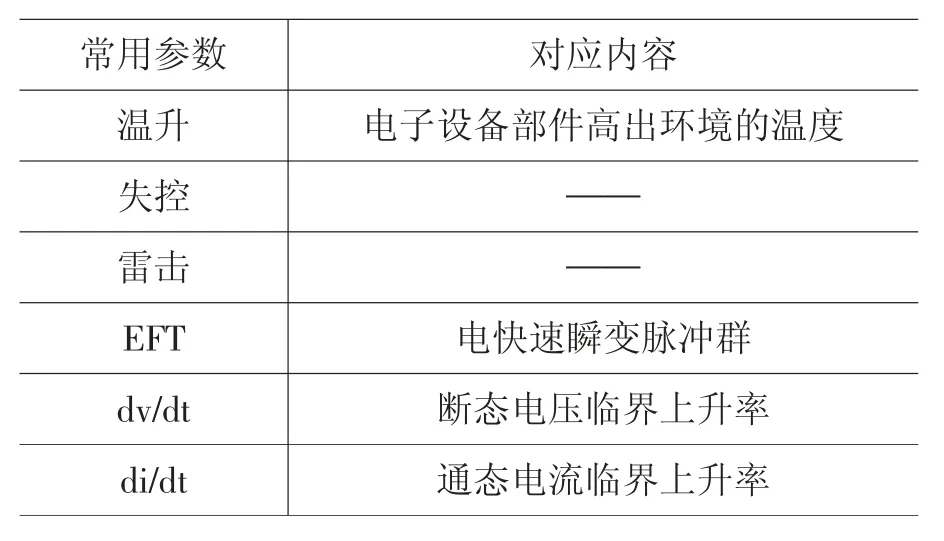

在了解晶闸管芯片相关参数的基础上,能够更加清晰地理解提升新型结构晶闸管芯片性能的机理,尤其是是门极的影响。晶闸管芯片的常用参数如表1所示,晶闸管芯片的其他测试参数如表2所示[3]。

表1 晶闸管芯片的常用参数

表2 晶闸管芯片的其他测试参数

为更清晰地描述该半导体芯片的导通原理,可将图1所示的芯片结构看作是两个互相作用的三级管的组合,由此衍生出如图2所示的半导体导通原理。

假设电路处于稳定的阻断状态,电压UA 实际上是降于集电极的势垒区上。在外电路中,电流IA=IA0,在数量级上与集电极漏电流IC2 或门极电流IG0相当,并由其中较大值的来决定。

当t=0 时,合上开关S,门极电流以增量δIG突然增加。这样晶体管T2 的基极电流就由起始值IB20=I*B20+IG(t﹤0)增加至IB20=I*B20+IG0+δIG(t=0)。此时,发射极J3 更正向偏置,更多的电子由此注入基区,并向集电极扩散,其中只有一部分在途中被复合掉,因此集电极电流增加。

受到电子渡越时间的限制,经过延迟时间tv2 后,阳极电流才开始增加。为了简化作出如下假设,经过延迟时间后,集电极电流能够准确地增加至新值,如此可得方程式(1):

式中,β2—晶体管2 在共发射极回路的小信号电流放大系数。

同时,集电极电流IC2 即晶体管T1 的基极电流IB1 供给n 基区电子。当t=tv2 时,晶体管T1 的基极电流的增量为ΔIB1(tv2)=ΔIC2(tv2)=β2δIG。

类似于晶体管2,经过延迟时间tv1 后,集电极电流增量如方程式(2)所示:

式中,t1=tv1+tv2;β1—晶体管1 的小信号电流放大系数。

另外,当集电极电流IC1 流回晶体管2 的基区时,IC1=I*B2,t1=tv1+tv2,该电流在晶体管T2中又使基极电流有了新的增加,具体如方程式(3)所示:

方程式(3)表明:原始信号δIG 在两个晶体管中依次被放大β2 和β1 倍后,又反馈回原基极。因此,沿着反馈回路总的放大系数(该反馈回路已在图2中用虚线表示)为β12=β1β2。

开通(门极触发)意味着阳极电流IA=IE1 趋于无限增加,这是以基极电流无限增加为前提的,一旦反馈信号稍大于或等于原始输入信号ΔIG,基极电流就会无限增加。按照方程式(3),开通条件应如方程式(4)所示:

方程式(4)中,两个晶体管的共发射极回路的小信号电流放大系数的乘积至少等于1。

将β=α/(1-α)带入方程式(4),可得等价的开通条件如方程式(5)所示:

根据方程式(5),两个晶体管在共基极回路中的小信号电流放大系数之和至少等于1[3]。

3 门极结构的设计方向

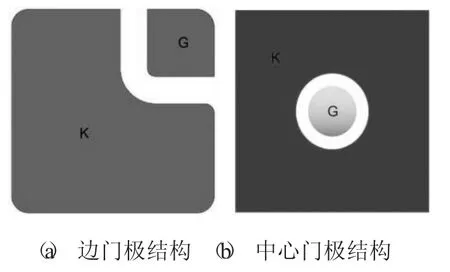

传统晶闸管芯片主要使用条形门极和工字门极等[4],而且门极数量单一并位于芯片的边缘位置,该门极的设置弥补了由于阴极不均匀而导致触发速度慢等相关问题。通过调整门极的位置、形状、大小、数量以及不同组合等方式,使门极的分布更加多样化并更具可控性。门极的调整在一定程度上可优化开关速度、通态压降、扩展速度、di/dt 和开关损耗等相关参数,用以匹配不同产品的需求[3]。为进一步验证中心门极的优势,制备了如图3的光刻版图。

图3 两种不同结构的门极

从图3(a)和图3(b)的对比可以看出,中心门极更利于其触发。一方面中心门极与发射极之间的触发点更多,触发更敏感;另一方面,在实际工艺中,由于光刻的轻微偏差都会导致触发电流的波动,而从图3(b)中可以看出中心门极的触发极位于中心位置,因此对于光刻误差的影响会大幅度降低。

尽管中心门极在理论上具有优势,但在实际生产中能否得到与理论对等的结果还需要进一步试验验证的。为此,2021年吉林华微电子股份有限公司的研发团队就该设想进行了验证,并发表相关专利进行理论论证和技术保护[5]。根据相关专利可以获取中心门级在使用上的明显性能优势。

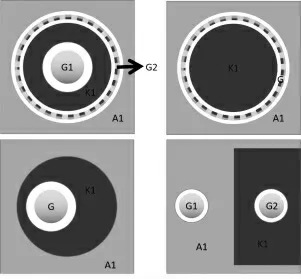

传统的晶闸管芯片技术往往局限于单一门极和固定位置。为进一步提升晶闸管性能,如图4所示设计了不同的芯片结构。

图4 不同设计的芯片结构

图4中固定在边缘位置的门极普遍触发较为不均匀,固定在中心位置则会增加引线过程中的成本需求,而引入偏心和多重门极就可以同时解决边缘门极的不均匀和中心门极的引线成本。引入环形门极利于提升双向晶闸管芯片的开关速度,并与其他门极配合起到共同放大门极的效果。不同配合方式的门极不仅能够起到提升性能和产品质量的作用,还能够匹配实际生产中的相关需求并弥补局限性。因此,未来门极的结构将向着更广泛的设计层面发展,并根据实际情况在不同应用领域通过调整不同的触发极状态来实现其触发效率的最大程度提升。

4 多层半导体结构分析

根据晶闸管芯片基础原理可知,随着PNN+结构中电压的不断升高,空间电荷区的展宽在到达N+层后,由于N+层杂质浓度较高,空间电荷区的展宽变得很小。当结区最大电场强度持续增强后,待到达雪崩电场强度时,反向电流将会急剧增加。据此可得,增加了N+层可在一定程度上提高晶闸管的耐压能力[6]。同理,在晶闸管芯片的各掺杂硅区域形成一定的浓度差也会使芯片的耐压和稳定性得到一定程度地提升,而工艺上不同元素掺杂硅的扩散推结速率也是这样。基于实际的工艺情况,不同结深同时配合不同元素也更加利于控制生产与整体工艺的稳定性[7]。为更明确展示多层半导体结构的设计方案,设计了如图5所示的晶闸管芯片多层半导体结构示意图。

图5 晶闸管芯片多层半导体结构示意图

从图5中可以看出,多层半导体主要定义为某P/N 型半导体内部结构。该P/N 型半导体内部形成不同的半导体层,每个半导体层具备独特的半导体掺杂浓度或者不同的掺杂元素。基于此,可在一定程度上提高晶闸管芯片的动态参数[8]。具体工艺形式:首先,进行低浓度深结扩散,即注入低浓度P 或N 型掺杂物质;其次,进行高温长时间推结;然后,进行高一级浓度的注入后继续推结;最后,依次进行相关工艺,以获取多层次的半导体结构。

为此,笔者所在研究团队先同时制备了常规的单层半导体结构与优化的多层半导体设计结构,再在调试出相同静态参数的情况下,通过同一封装公司、同样的封装外形,取回后进行相应的动态参数测试。经过测试发现:单层结构与多层结构除温升较为接近外,多层结构的其他参数有着明显的优势。特别是晶闸管中的重要动态参数,如多层结构在断态电压临界上升率(dv/dt)方面有着特别明显的优势,几乎是接近单层结构的二倍,这对于未来漏保产品的研究有着重要的参考价值[9-10]。

当前的常规单层晶闸管芯片一般会增加一层高浓度P 型掺杂层,主要原因是当半导体与金属接触时,通常会形成势垒层,但是当半导体掺杂浓度很高时,电子则可凭借隧道效应穿过势垒,从而形成低阻值的欧姆接触[8,10]。欧姆接触对于半导体器件非常重要,形成良好的欧姆接触有利于电流的输入和输出。P 型掺杂硅的浓度如果较高会导致电压低的问题,且P 型掺杂硅的导电性本身较差,因此需要在P 型掺杂区表面与引线孔接触一侧形成高浓度掺杂。在实际工艺中,高浓度P 型掺杂硅影响N 型掺杂硅浓度,同时高浓度P 型掺杂硅由于导电性较好,容易造成表面短路现象,就会影响晶闸管芯片的门极触发,从而造成触发电流增加的现象,因而不利于小触发晶闸管芯片的研发[11]。为此,需要有针对性地重新规划表面高浓度P 型掺杂硅,在相同工艺情况下,针对P 型掺杂硅进行有规律的光刻可以避免高浓度的P 型掺杂硅掺杂到阴极区、门极与发射极隔离区的区域,这也在最大程度上提升了晶闸管芯片的触发性能[11]。

4 结语

目前,晶闸管芯片的设计方向更加多元化,具体表现在门极多样化、多层半导体和P 型掺杂硅的图形化,而且随着人们对功率半导体的重视和投资加大,不仅相关科研水平稳步提升,相关领域人才需求也在逐步增加,因此为了使晶闸管芯片研发步入世界前列,对于晶闸管芯片的相关设计与优化仍然持续进行。