基于FPGA的直流电机控制系统的设计

2022-02-22刘仲晔

刘仲晔

(海装驻湘潭地区代表室,湖南湘潭 411100)

1 基于FPGA的直流电机控制系统整体架构

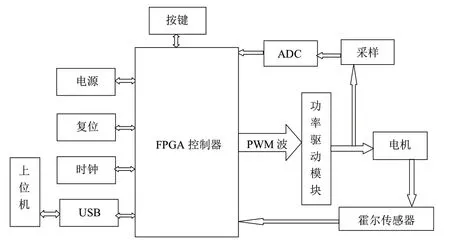

作为控制系统的核心部分,FPGA 要尽可能地减少系统体积,保障系统运行灵活性,以实现不同场景的修改与人性化设计。FPGA 自身有着较小的能耗,因此在移动电源场合弥足珍贵。本研究采用FPGA 芯片进行电机控制系统设计。通常FPGA 控制器启动后,能够对电机转子位置相关信号进行采集,对应的会形成6位换相信号,其与PWM 波信号结合,能够对逆变器6个功率开关管进行控制,实现导通或截止,使得电机处于正常运转状态[1]。

电源、时钟、复位等相关的配置电路是保障FPGA 芯片工作的必要前提。除此之外,还需要借助按键对电机的转速进行控制。首先需要进行按键设置,即在开发板选择SW1、SW2作为脉冲信号输出路径,FPGA 产生PWM 信号后,按键能够对占空比进行控制。另外,一般情况下,FPGA 在脉宽调制波输出期间电压会低于正常电压,各个端口输出的电压均在5V 以下,难以直接将电机驱动。因此需要引入功率驱动模块,将其安装于FPGA 控制器与电机之间,提供高电压保障电源供电。或者FPGA 输出PWM 波时,经过控制作用,使得电机具有合适驱动电压的支持。驱动电压稳定性受多种因素影响,电机的运转速度往往难以掌握,基于此需要引入反馈形成闭环。采用采样电阻实时对功率驱动电路电流予以采样处理,采集信号向控制器反馈,可修正控制信号[2]。基于上述需求,电机控制整体系统架构设计如图1所示。

图1 电机控制整体系统架构

2 基于FPGA的直流电机控制电路设计

2.1 芯片选型与供电

FPGA 的合理化选择是保障系统优化设计的重要环节,研究应用Smartfusion 进行系统模拟,并在此基础上融合Cortex-M3ARM 内核,其与FPGA 芯片能够对数据进行并行处理,促进了控制器性能的提升。与FPGA 相比,ARM 灵活性强,二者结合有利于问题的解决。Smartfusion 的内部集成了100 MHz RC 振荡器,精度均为1%,外部能够与1.5~20 MHz 的时钟以及低功耗时钟连接,配备了两个锁相环,通过功率的输入与输出能够动态配置,使得不同类型时钟信号顺利在芯片输入。Smartfusion 具有可编程模拟模块,有利于反馈环节的设计,能够实现电压、电流及温度监控。ADC 能够达到3路12位,当处于8位模式,速度能够达到600 ksps,内部参考电压为2.56 V。不仅如此,Smartfusion 对多项资源进行集成,可进行利用。常见为Cortex-M3系统,配备Cortex-M3处理器,运行速度可达到100MHz,存储器件优越,可编写,即便掉电,也不会使数据丢失。Smartfusion 利用128位AES 加密技术,高效、可靠;FPGA 部分I/O 灵活性强,同时支持LVDS、PCI、LVCOMS 等多种电平。

芯片正常工作需要稳定的供电。Smartfusion 开发板对应部分电源电压不尽相同,如图2所示。电平值为1.5 V,直流MSSI/O 缓冲区需要3.3 V 电压。引脚电压不同,为实现标准5 V 电压的转变,可以采用线性稳定芯片LT1963、LT3080将其转换为5 V、1.5 V电压。在电平输入与输出端分别配置0.01 μF、10 μF电容,能够将噪声消除,且具有滤波功能,提升运行稳定性。

图2 控制器供电情况示意图

2.2 时钟电路

芯片在保障额定电源供电的同时,应提供稳定的时钟信号,保障内部模块顺利开展工作。本研究在系统设计中配置了两个振荡器,低功率振荡器32.764 kHz,高频振荡器为20 MHz。时钟电路设计如图3 所示。谐振器功率为20 MHz,在Smartfusion芯片MAINXIN 与MAINXOUT 管脚之间,受负载电容的影响,谐振器实际功率在20 MHz 以下,为解决这一问题可以引入两个18 pF 电容进行串联,使得谐振器功率稳定为20 MHz,能够满足以太网时钟高精度需求。32.764 kHz 谐振器放置位置为LPXIN 与LPXOUT 管脚之间,采用30 μF 电容进行连接,能够减少误差,促进实时计数的实现。

2.3 复位电路

电机控制系统运行可靠性很大程度上取决于复位电路,复位电路功能相当于计算机的重启按键,当发生故障时,按下复位键,能够使程序重新启动。不仅如此,复位电路不会一上电便进入工作状态,能够避免CPU 发出错误指令,出现不当操作,电磁兼容性得到了保障。本研究在设置复位系统时引入施密特触发器,复位电路系统结构如图3所示。NL-DS1818复位端口初始保持高电平,未启动复位功能,按下SW3键后,会形成一个完整的通路,高电平经电阻到低电平通路,此时复位端会变为低电平,将复位功能触发。在施密特触发器作用下,复位按钮噪声能够明显降低,该复位信号与开发板微控制器复位保持同步。

图3 复位电路系统结构示意图

2.4 按键电路

按键电路负责对FPGA 芯片进行信号的输送,设计简单。未按下按钮前,SWITCH1 为高电平状态,电压为3.3 V,按下按钮SW1后,高电平端经过电阻、按键会达到低电平端,此时SWITCH1位置会出现一个瞬时的低电平,发出“0”值脉冲信号。

2.5 去耦电路

驱动源与被驱动负载共同构成了一个完整的电路,当处于较大的负载电容,驱动电路要想实现信号的跳变,首先需要充电、放电,若上升沿陡峭,会导致电流增大,部分电流会被分出去,影响系统的正常运行,这一现象即耦合现象。去耦电路在分立元件、集成电路中均有着广泛的应用,是电路设计应用最多的模块。该系统设计的去耦电路电容值包括0.1 μF、1 μF 以及10 μF 多个不同规格。采用1 μF、10 μF 电容能够对高频噪声有效去除,其平行共振频率>20 MHz,高频滤波电容主要置入芯片引脚位置。

3 基于FPGA的直流电机的驱动电路设计

在信号输入端配备上拉电阻,为330 Ω,主要功能是驱动上桥,完成电平转换。PWM 波达到10 kHz会产生噪声,需要进行滤波处理,本研究采用100 pF多层陶瓷电容进行滤波。为提升电压需要采用3个自举电路,电容与二极管组成完整的自举电路,前者用于电荷储存,后者能够对电流倒灌起到预防作用。在频率较高的状态下。电路输入电压与电容电压构成了自举电路电压,起到升压的作用。研究在设计中不仅引入自举电路二极管与电解电容,而且还配置一个10 Ω 的电阻,用于限流自举电路,仍需要去耦处理自举电路,将自举电路与0.22 μF 电容并联,可发挥滤波作用,尽可能使去耦电容与芯片引脚靠近。电源接入端需要采用略大容值的电容进行滤波处理,研究设计时电解电容为22 μF。为确保系统的正常运行还需要针对电路进行故障锁定设计,保护电流。多层陶瓷电容可起到故障锁定与定时的作用,直流母线滤波电容宜选择寿命长、纹波电流高的电容。所用电阻为康铜丝电阻,具有耐高温、温度系数小的特点。需要注意的是在连接该电阻时应将其与引脚尽可能接近。

该驱动电路下,能够保持稳定的供压,结合输入信号对内部功率开关器件进行控制,实现导通,将三相电流输出,使得电机受到驱动,进入运转状态。

3.1 电机选型

电机选择首要考虑的是功率与转速,除此之外还要优先选择体积小、重量轻的电机,保障灵活度。本研究选择的是德国公司生产的QBL4208-41-04-006号电机,当转距处于额定状态下,其转速能够达到4 000 r/min,轴直径5 mm,长度20 mm,外形小巧,总重量仅为300 g,灵活性强。该电机额定工作电流与电压分别为1.8 A、24 V,最大峰值电流与工作电压分别为3倍,5.4 A、48 V。该电机还配备了霍尔传感器,能够将霍尔信号传输到控制器。

3.2 系统测试

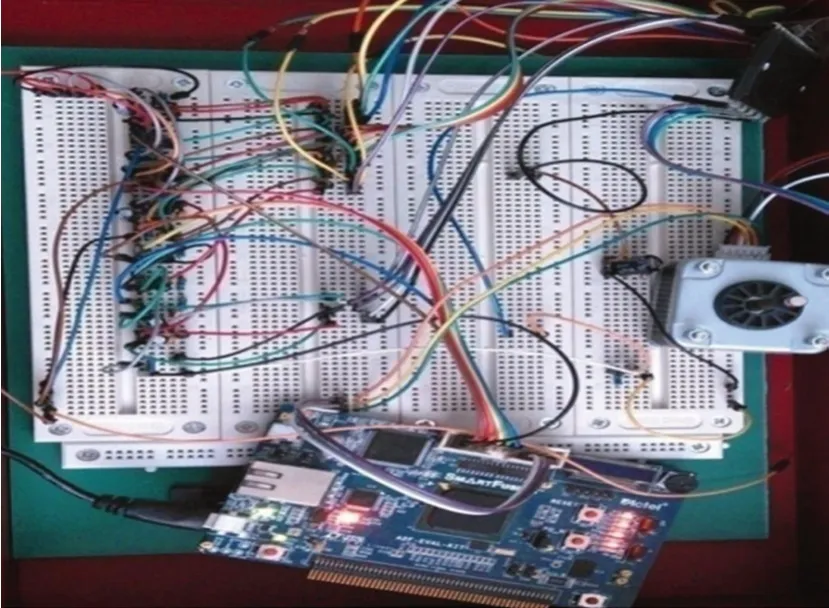

研究构建的基于FPGA 的直流电机控制系统如图4所示,将小型的三相电机作为实验对象,予以驱动实验,按键后将速度实施16挡控制,转速从理论角度能够达到4 000 r/min。为确保驱动模块能够达到最佳的驱动性能,在驱动小车时无需将转速设置过高,因此电源电压采用的是15 V,转速最高为2 500 r/min,挡位差值约为156.32 r/min。为验证电机的静态性能,给定了一个PWM 波,为10 kHz,假设其占空比为50%,理论上转速为1 250 r/min,电流为1.125 A。

图4 系统设计实物展示图

在分析各路信号相位关系时采用在线逻辑分析仪,可以发现,输出信号能够满足电机正常运行,可实现转子换相,经占空比对电机转速作出相应的调整。电机完成霍尔信号输出后,选择其中两相予以采样处理,获得其相位,结果如图5所示。可以发现霍尔信号相位周期相差1/3,对其中1路信号划分6段,发现各个时间段信号均处于正常,能够满足霍尔信号相位关系需求,提示运转正常。

图5 75%占空比PWM电机输出霍尔信号

验证电机中电流反馈环的效果,在启动三相电机后,对主回路电流予以采样,对比控制前后情况,可以发现电流闭环PID 算法应用后,降低了电流振荡幅度,不足开环时的一半,从振荡时间方面看,由初始的500 ms 缩短至200 ms,表明闭环可提升系统稳定性,使得电机运行更为平稳。综合上述实验结果,可以发现该系统能够实现既定的目标,启动时间可达到200 ms,且能够将转速误差控制在0.5%内。

4 结束语

直流电机使用范围广、工作效率高,控制系统具有一定的复杂性。本研究设计的基于FPGA 的直流电机控制系统坚持灵活方便、高精度的原则,采用Smartfusion 控制核心,驱动电路采用PS21564-P 作为主体,通过时钟、按键、电平等配置电路,能够实现数据的控制与传输,电流保护与自举电路具有滤波功能,在减小体积的同时,能够降低控制器误差。经系统验证,该系统具有较好的静态特性与动态特性,能耗低,保障了系统稳定性。