基于定时器和锁相环的伺服系统分频输出方法应用研究

2022-02-13针跃军

摘要:一些运动控制系统,要求伺服驱动器能够输出正交的脉冲,用于反映电机轴的位置信息。现介绍一种基于定时器和锁相环的伺服系统实现可变整数分频输出的方法,即编码器原始信号经运算产生速度信息和位置信息,锁相环以一定的响应速度跟随位置信号;由定时器产生一对中心对称的PWM信号,经过移相产生的分频输出信号再经第二个定时器的正交脉冲接口采样,形成负反馈闭环。经仿真验证,该方法可实现产品要求的35~32 767任意整数分频。研究成果可为相关应用与研究提供参考。

关键词:定时器;锁相环;分频输出;伺服系统

中图分类号:TM921.54 文献标志码:A 文章编号:1671-0797(2022)03-0013-04

DOI:10.19514/j.cnki.cn32-1628/tm.2022.03.004

0 引言

运动控制系统为了监视或控制机构的运行状态,常需驱动执行机构的伺服驱动器将电机编码器位置信息分频后,以正交脉冲的形式实时反馈给上位控制系统。对于脉冲型伺服驱动器,这是常用的方法;对于总线型伺服驱动器,虽然可以通过总线接口向上位控制系统反馈位置信息,但应用中也存在不足之处:一方面,要求上位控制系统总线接口必须与伺服驱动器总线接口相同或者兼容,另一方面,总线通信周期相对伺服控制周期来说较长,且存在较大通信抖动,对于全闭环控制难以获得理想的性能,所以仍然需要将编码器数值分频后通过正交脉冲接口实时反馈到上位控制器[1]。

分频输出采用的硬件平台,一般基于CPLD或FPGA来实现[2],这就需要在伺服系统中增加额外的逻辑单元,会增加成本和系统复杂度。

本文方法,硬件上采用MCU芯片自带的两个定时器外设单元:一个定时器利用PWM功能,生成一对频率可变、占空比为50%的正交脉冲信号;然后将分频输出的正交脉冲信号连接到第二个定时器的编码器接口,对输出信号进行测量,形成反馈;将分频输出脉冲指令信号与反馈信号比较后,利用锁相环跟随指令信号,形成对分频输出的自动控制。

本设计充分利用微处理器丰富的定时器外设,控制上采用锁相环跟随编码器输入信号,在不使用可编程器件的情况下,实现低成本的35~32 767范围内任意整数分频输出,经仿真和实验验证可达到设计要求。

1 分頻输出正交脉冲的方案设计及实现

1.1 设计原理

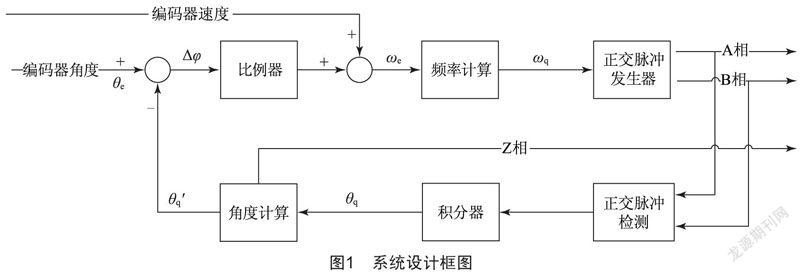

伺服电机位置反馈采用多摩川17位RS485总线式绝对式编码器[3],单圈分辨率为131 072。分频输出正交脉冲分辨率为35~32 767。系统设计框图如图1所示。

编码器实时角度θe与反馈的正交脉冲角度θq′比较后形成角度差Δφ,经比例放大叠加编码器速度后形成速度信号ωe。ωe经频率计算后得到正交脉冲频率ωq,然后通过正交脉冲发生器产生占空比为50%的脉冲信号。此信号经正交脉冲检测器检测积分后形成正交脉冲的角度值θq,再经角度计算后,形成正交脉冲反馈角度θq′。

当编码器角度θe与正交脉冲角度θq′同相位,那么角度差Δφ为0,正交脉冲输出频率正比于编码器速度;当电机加速时,编码器角度θe超前正交脉冲角度θq′,相位差Δφ增加,导致ωe增加,正交脉冲频率ωq增加,最终使得反馈角度θq′相位增加,这样相位差Δφ将会减小;当电机减速时,编码器角度θe滞后正交脉冲角度θq′,相位差Δφ减小,导致ωe减小,正交脉冲频率ωq减小,最终使得反馈角度θq′相位减小,这样相位差Δφ将会增加。整个调节过程为反馈控制方式[4],无论电机处于何种运行状态,系统总能将相位偏差降低,且积分环节可使稳态偏差消除,使分频输出角度始终跟随编码器角度。

1.2 正交脉冲发生器

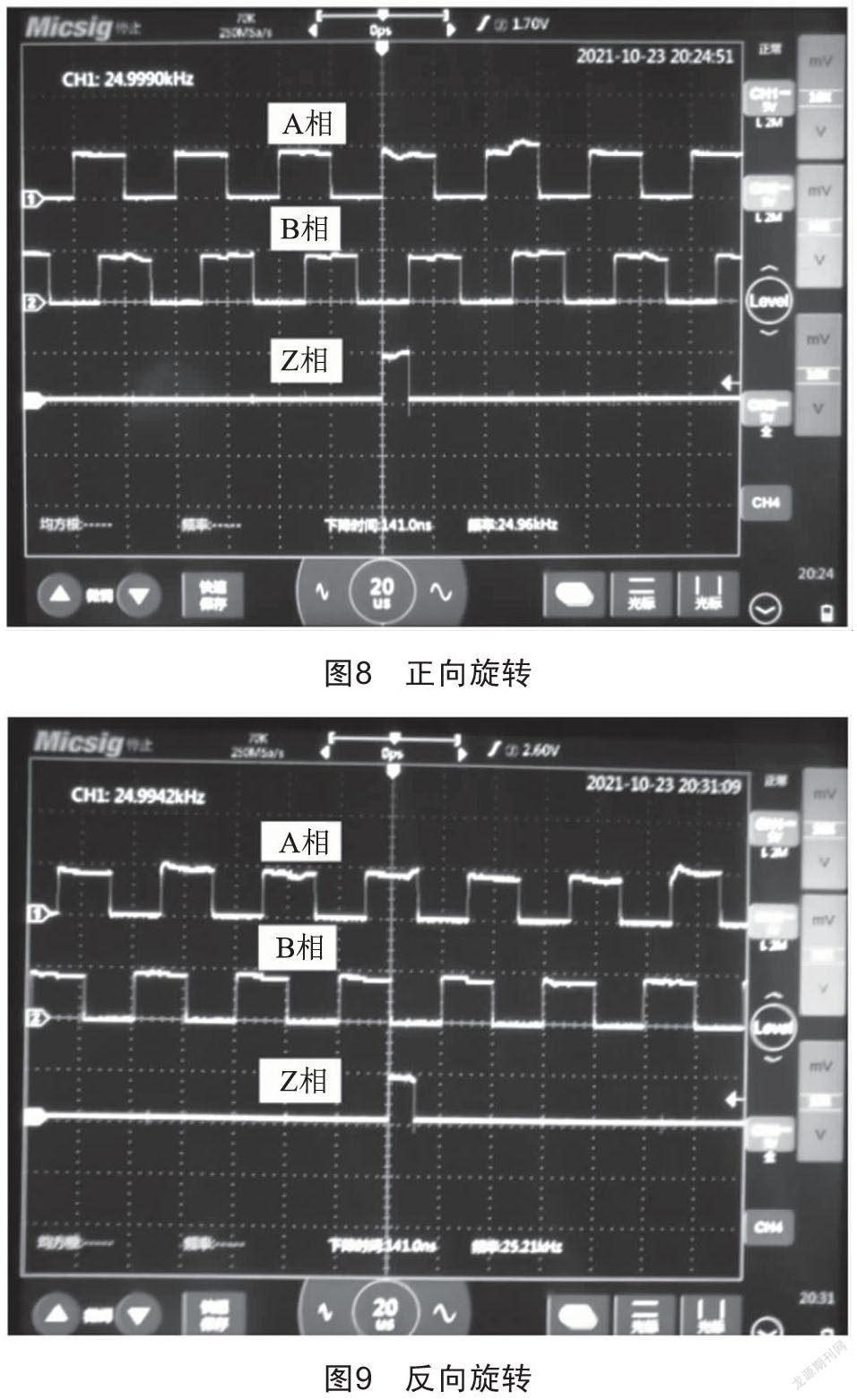

正交脉冲由工作于非对称PWM模式的定时器产生,其由正交的A、B两相脉冲和表示零位的Z相信号组成,且三个信号之间有一定的相位要求和占空比要求[5]。定时器在该模式下生成的两个中心对称PWM信号间允许存在可编程相移。当定时器向上计数时,若定时器值小于比较寄存器值CCR1,则输出高电平;反之,输出低电平。当定时器向下计数时,若定时器值大于比较寄存器值CCR2,则输出低电平;反之,输出高电平。正交脉冲输出过程如图2所示。

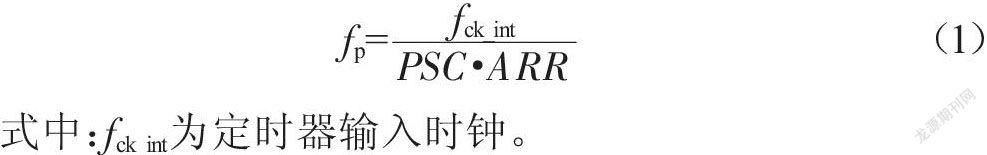

脉冲频率fp由计数器的重载寄存器ARR和定时器的16位预分频器PSC确定,如式(1)所示:

式中:fck_int为定时器输入时钟。

由图2可知,综合调节比较器CCR1~CCR4的值,即可改变两路PWM脉冲的占空比和相位。脉冲A与脉冲B要求占空比为50%、相位差90°,可固定脉冲A与定时器三角波中心对称,只调节脉冲B的相位。各比较寄存器值计算如下:

1.3 正交脉冲检测及Z信号生成

1.3.1 正交脉冲的检测

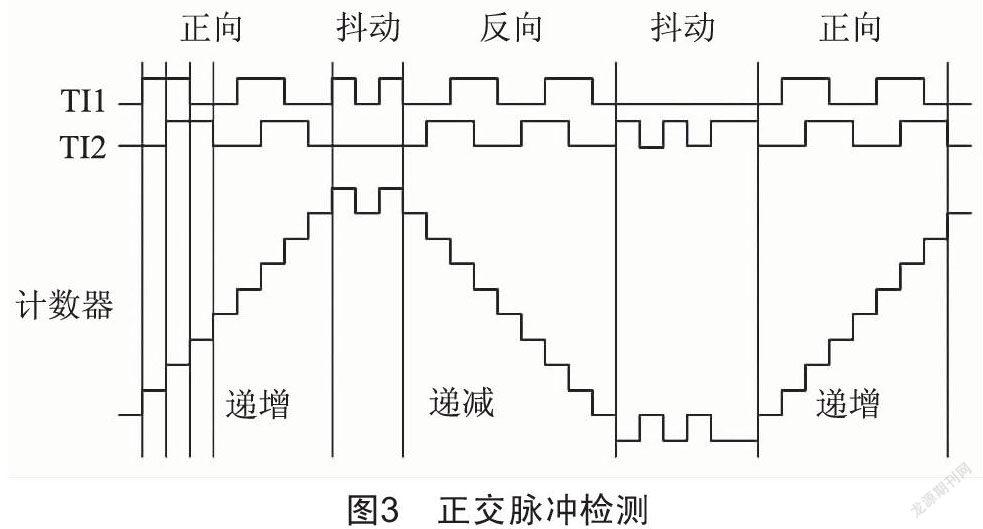

将输出的正交脉冲信号A与B分别连接到第二个定时器TIM2的编码接口TI1、TI2,并配置为编码器接口模式。此时,它相当于带有方向选择的外部时钟,在两路信号的每个边沿进行计数。当A相超前B相时递增计数,B相超前A相时递减计数,因此其计数值始终表示正交脉冲的位置信息,计数方向对应于旋转方向。工作过程如图3所示。

1.3.2 产生零位脉冲Z信号

Z信号与A相、B相脉冲有一定时序和精度要求,且Z信号的正脉宽要求为90°。为达到此要求,采用定时器TIM2的输出比较功能输出脉冲宽度为1个时钟宽度的信号作为Z信号。首先,将TIM2重载寄存器TIM2_ARR设置为分频脉冲的分辨率Ro,如此,当向上计数达到该值时,定时器将从0开始重新计数,并产生更新事件。其次,打开定时器TIM2溢出中断,当中断发生时,强制输出Z信号为低电平。最后,在向上计数时设置比较寄存器值为1,向下计数时设置比较计数器值为Ro-1,当比较匹配时,Z信号设置为自动翻转。

1.4 锁相环

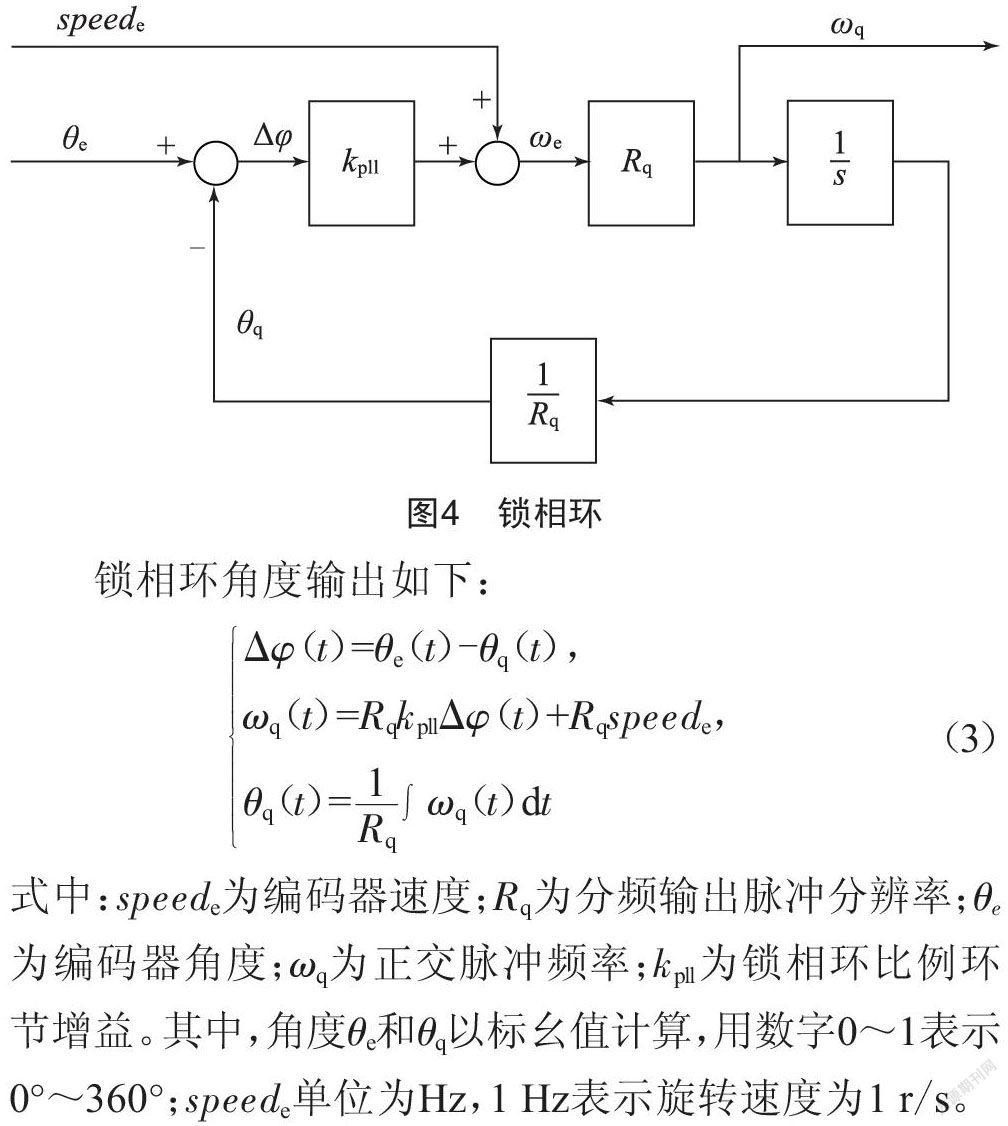

锁相环的作用是稳定分频输出的角度,即正交脉冲的个数,实时跟踪电机编码器角度值。锁相环结构图如圖4所示,由负反馈调整回路实现。

锁相环角度输出如下:

式中:speede为编码器速度;Rq为分频输出脉冲分辨率;θe为编码器角度;ωq为正交脉冲频率;kpll为锁相环比例环节增益。其中,角度θe和θq以标幺值计算,用数字0~1表示0°~360°;speede单位为Hz,1 Hz表示旋转速度为1 r/s。

比例环节增益kpll应尽量大,以提高系统的动态响应,有利于快速跟随输入信号;但同时也要足够小,以减少输出频率抖动引发的干扰。其值可通过仿真和调试进行合理选取。

2 分频输出脉冲自动控制仿真与实验验证

2.1 控制系统的Simulink仿真

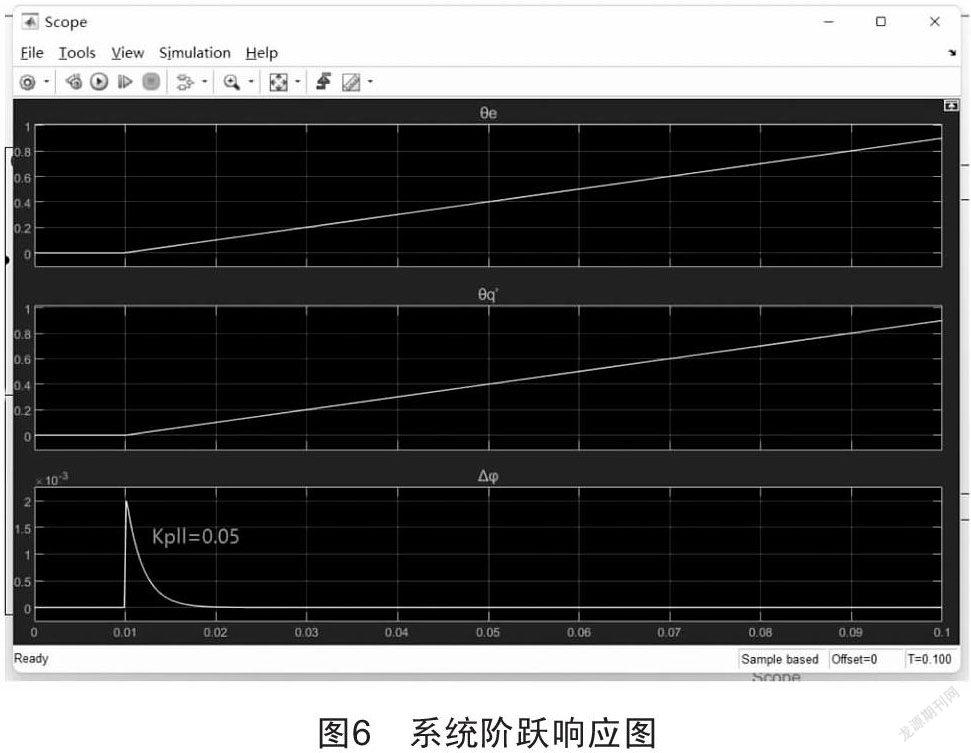

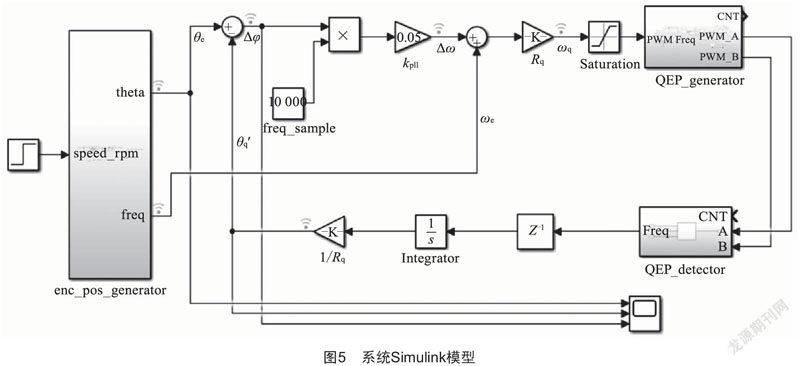

系统Simulink模型如图5所示。正交脉冲发生器模块QEP_generator是利用Simulink基本模块单元搭建的,用于模拟MCU定时器外设产生正交PWM;正交脉冲检测模块QEP_detector用于模拟MCU定时器编码器接口进行正交脉冲计数;其他比例、积分模块采用标准的Simulink模块实现[6]。

通过调节kpll值观察模型的阶跃响应,以初步找出kpll的合适范围,为实验验证提供较为准确的值,阶跃响应如图6所示。系统采样频率10 kHz,仿真时长0.1 s,在0.01 s编码器速度由0 r/min变化至600 r/min,角度误差经过0.02 s收敛至稳定值。经仿真比较,随着增益kpll增大,收敛逐渐加快;当kpll大于0.4时,会出现超调且能够收敛;当kpll等于1.0时,系统出现震荡且无法收敛。为减少系统震荡,将系统调节为过阻尼状态。根据调参仿真,kpll以不大于0.4为好。

2.2 实验验证

2.2.1 实验平台与实验方法

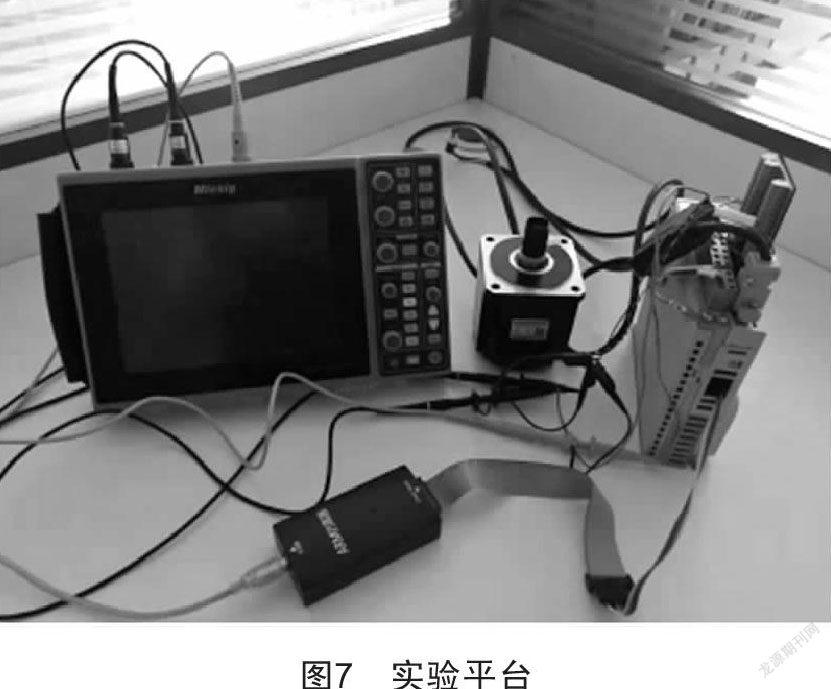

采用四横电机SH660系列220 V/400 W交流伺服驱动器作为实验平台(图7)来验证本文所提分频输出方法。伺服电机安装17位多圈绝对式编码器,额定转速3 000 r/min,设置分频输出4倍频后分辨率为10 000。分频正交脉冲由Micsig STO1104C示波器采样,脉冲计数由J-Scope采样并显示。实验操作使用四横电机公司的伺服系统调试软件ShMotion,利用调试软件位置点动功能,设定点动脉冲数位20 000,单圈脉冲数10 000,最高速度设定为600 r/min。调试软件启动位置点动功能后,伺服电机以设定速度先反向运转720°再正向运转720°,用示波器和J-Scope同时采集分频输出脉冲,对设计方法进行验证。

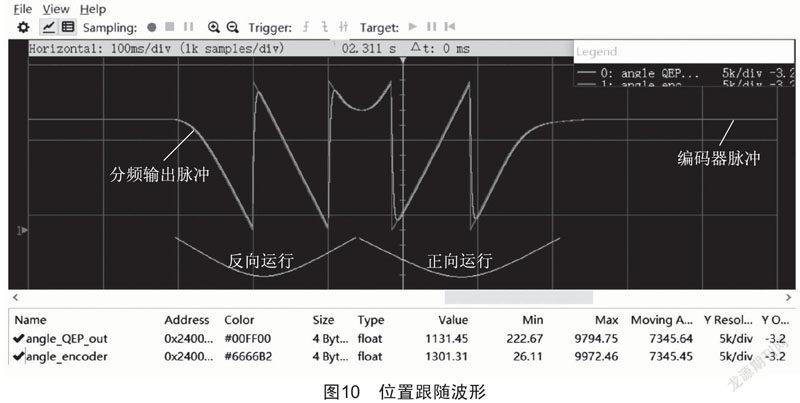

2.2.2 正交脉冲相位验证

正向旋转波形如图8所示,可以看出,正交脉冲A相超前B相90°,频率为25 kHz。修改点动脉冲数位-20 000,反向旋转波形如图9所示,可以看出反向运转时B相超前A相90°,频率为25 kHz。根据实验结果,分频输出信号特征符合产品要求。

2.2.3 分频输出脉冲位置跟随性验证

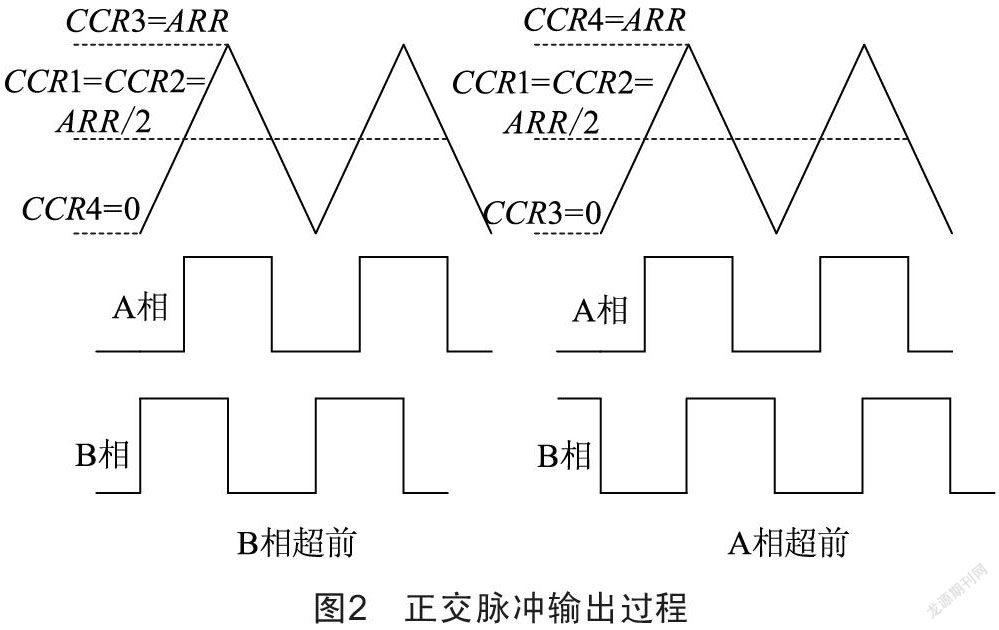

J-Scope采集位置跟随波形如图10所示,在反向旋转时,分频输出脉冲信号跟随编码器脉冲以下降锯齿波的形式在0~10 000之间变化。

在完成反向运动20 000个脉冲后,电机减速停止到初始位置,开始正向运动。正向运动时,分频输出脉冲跟随编码器脉冲以上升锯齿波的形式在0~10 000之间变化,完成正向运动20 000个脉冲。可以看出,分频输出角度能够较好地跟随编码器角度。

3 结语

综上所述,本文介绍了一种基于定时器和锁相环实现伺服系统可变整数分频输出的方法,使用微控制器两个定时器外设,控制方法上采用比例积分环节构成锁相环,无须CPLD或FPGA器件,在伺服系统原有的MCU上就可实现,具有明显的成本优势。通过仿真和实验,在伺服系统5 000 r/min速度范围内,该方法可实现产品要求的35~32 767任意整数分频。该方法在低速范围内还可提供倍频输出,但囿于定时器PWM的输出频率,高速倍频会受到限制。

[参考文献]

[1] 丁信忠,严彩忠.伺服系统等占空比任意小数分频研究[J].微电机,2018,51(7):40-43.

[2] 汪虹,李宏.基于FPGA的等占空比任意整数分频器的设计[J].现代电子技术,2005(16):8-9.

[3] 姜燕平.多摩川绝对式编码器特点和应用[J].电梯工业,2006(1):14-15.

[4] 胡寿松.自动控制原理[M].6版.北京:科学出版社,2015.

[5] 杨金波,殷春辉,赵晶.正交脉冲分频系统设计[J].测控技术,2015,34(7):144-146.

[6] 孙忠潇.Simulink仿真及代码生成技术入门到精通[M].北京:北京航空航天大学出版社,2015.

收稿日期:2021-11-19

作者简介:针跃军(1983—),男,山西人,工程师,研究方向:伺服控制系统。