一种以太网通信芯片的优先级编码方法

2022-02-10王昉闫振林张兵杨怡平靳新波

王昉 闫振林 张兵 杨怡平 靳新波

摘要:随着网络应用的不断丰富,包括路由、QoS保障等在内的复杂业务对以太网通信设备的数据检索匹配能力提出了更高的要求,因此基于内容可寻址存储器(Content Addressalle Memory,CAM)的以太网通信芯片及其数据查找机制成为研究的热点。然而此类通信芯片存储器所使用的優先级编码及检索方法大多针对固定位宽数据,难以支持新业务对多种位宽数据进行灵活检索的需求。针对这一问题,提出了一种以太网通信芯片的优先级编码方法,使得CAM支持适应多种查找模式。通过比较,该方法能使以太网通信芯片具有更多位宽数据的搜索能力,同时减少对线道的要求。

关键词:以太网通信芯片;内容可寻址存储器;多种搜索位宽;优先级编码

中图分类号:TP333文献标志码:A文章编号:1008-1739(2022)24-60-4

0引言

在以太网通信设备中,用来存放程序和数据[1]的存储器有着不可或缺的作用。传统的计算机存储器(RAM或ROM)使用地址来指示存储单元的位置,并且输出该位置存储单元中的数据。而内容可寻址存储器(Content Addressalle Memory,CAM)则接收外部检索数据,比较该数据与CAM中存储的数据是否匹配,并且输出该匹配数据在CAM中的地址。由于存储器中与检索数据相一致的数据通常不限于一个,因此,当以太网通信芯片CAM中有多个与检索数据相一致的数据时,一般需要使用优先级编码器对从存储单元输出的一致信号(表示与检索数据相一致的信号)进行编码,并返回优先级最高的地址信号。因此,以太网通信使用的存储器通常为CAM。

由于CAM的应用越来越广泛,而不同领域的应用所需的搜索数据位宽往往是不一样的。因此需要在不损失容量的情况下,提供多种搜索位宽的选择。传统做法是由多个最小宽度的模块来进行拼接,将每个小模块的匹配结果都输出到优先级编码器中,并进行不同的组合,计算出不同配置下最高优先级的地址。很显然,这种方式每增加一种位宽,布线通道就需增加一倍,不能满足集成电路的需求。同时,随着复杂路由、QoS保障等业务对以太网通信芯片的CAM提出了越来越灵活又复杂的数据搜索需求,其突出表现为搜索数据对象位宽往往非固定,使得针对固定位宽的优先级编码方法难以适应。针对这个问题,本文从优先级编码方法的改进入手,提出了一种以太网通信芯片的优先级编码方法。

1相关理论

1.1 CAM

CAM是以内容进行寻址的存储器,是一种特殊的存储阵列RAM。CAM在其每个存储单元都包含了一个内嵌的比较逻辑,写入CAM的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址[2]。RAM是一个根据地址读、写数据的存储单元,而CAM和RAM恰恰相反,返回的是与端口数据内容相匹配的地址。

一次典型的CAM查找操作过程为:首先,CAM接收外部的查找命令并把查找数据存储到比较寄存器中,比较寄存器和掩码寄存器的内容共同组成系统的一个查找字(search word),这些查找字广播到每一组相关联字中,每一组相关联字都有一个匹配链(matchline),匹配链指示查找字与存储字是否一致(匹配或不匹配),匹配链把结果反馈到优先译码器中,优先译码器产生一个二进制的匹配位置定位和一个匹配命中信号[3]。由于在CAM中可能存在多个字同时匹配,因而使用了一个优先译码器而不是简单的译码器。当有多个字同时匹配时,优先译码器选择最高优先权的匹配地址映射到匹配结果,在CAM中低地址字具有高优先权[4]。

1.2优先级编码

编码器是一种将信息由一种特定格式(或编码)转换为其他特定格式(或编码)的传感器、软件或算法,转换的目的可能是为了标准化、速度、保密性、保安或是为了压缩数据。而优先编码器允许同时在几个输入端有输入信号,编码器按输入信号排定的优先顺序,只对同时输入的几个信号中优先权最高的一个进行编码[5]。优先编码器常用于在处理最高优先级请求时控制中断请求。如果同时有2个或以上的输入作用于优先编码器,优先级最高的输入将会被优先输出[6]。

2设计思路

随着网络应用的发展,包括复杂路由、QoS保障在内的业务对以太网通信芯片提出了更为灵活和复杂的数据搜索需求,传统芯片固定位宽的优先级编码方式很难满足其需求[7]。因此,在不损失CAM容量的前提下,本文拟对现有存储器的编码方法进行改进,使其支持多种搜索位宽,具体改进思路如下:为了实现多种搜索位宽,首先提出最小宽度模块的概念,通过多个最小宽度模块来进行拼接,将每个小模块的匹配结果都输出到优先级编码器(PE)中,在优先级编码器中进行不同的组合,并计算出不同配置下最高优先级的地址[8]。支持4种不同搜索位宽的CAM芯片传统实现方法结构如图1所示,将PE放在中间,CAM阵列放在两边。该示例共放置了8个CAM阵列,能实现4种不同比较位宽的配置(即1,2,4,8倍位宽),CAM阵列在版图上需要提供3走线通道。如果放置16个阵列,则可以多一种16倍位宽的配置,走线通道则上升到7根[9]。

通过这个方式,每增加一种位宽,布线通道就需增加一倍,这在集成电路领域是不可取的。特别是随着特征尺寸的减小,CAM基本单元面积越来越小,形状也会越来越扁,版图上所能提供的走线资源更加稀缺,一般只有几根而已[9]。而这个方法在支持多种位宽搜索时,由于对芯片内部布线通道需求巨大,其所能提供的不同位宽模式种类也受到极大限制,无法提供更多模式来满足不同应用领域的需求。因此,这种优先级编码的方式很难提供4种或4种以上不同位宽配置的以太网通信芯片CAM。为此,提出了一种以太网通信芯片的优先级编码方法来克服这个问题,使一颗芯片具有支持更多搜索位宽的能力。

3优先级编码方法

3.1传统优先级编码方式

在CAM單元整列中存储数据,搜索的数据从搜索数据寄存器发送至CAM单元整列,如图2所示。然后,将该搜索数据与存储在CAM单元整列中的数据进行比较,如果存储的数据与搜索的数据相匹配,则将匹配线的逻辑电平设为高,反之则为低。最后,匹配线检测单元检测匹配线的逻辑电平。优先级编码器接收来自该检测单元的输出,并且输出匹配的CAM单元的字线地址[10]。

3.2支持多种查找模式的优先级编码方法

因此,本文提出了一种以太网通信芯片的优先级编码方法,对以太网通信芯片CAM进行如下操作:

①将CAM阵列分组,每组有一个底层优先级编码器,该优先级编码器放置于该分组物理实现的中间位置;

②底层优先级编码器对CAM阵列分组中每个字的比较结果进行处理,按照不同的配置计算出是否匹配,并将该新的匹配结果输出给上一层的优先级编码器A,底层优先级编码器同时生成组内CAM模块的块地址;

③优先级编码器A对底层优先级编码器的匹配结果进行处理,按照不同的配置进行计算,计算出是否匹配,并将该匹配结果输出给更上层的优先级编码器B,优先级编码器A同时需要对底层编码器产生的低位块地址进行选择,与该编码器生成的高位块地址合在一起,生成新的块地址;

④优先级编码器B对优先级编码器A的匹配结果进行处理,按照不同的配置进行计算,计算出是否匹配,并将该匹配结果输出给优先级编码器B的上一层优先级编码器C,优先级编码器B同时需要对优先级编码器A产生的低位块地址进行选择,与该编码器生成的高位块地址合在一起,生成新的块地址;

⑤以此类推,直至顶层;

⑥顶层优先级编码器对下一层优先级编码器的匹配结果进行处理,按照不同的配置计算出是否匹配,并对该匹配结果进行优先级编码,产生行地址;顶级优先级编码器同时需对下一层编码器产生的低位块地址进行选择,与该编码器生成的高位块地址合在一起,生成最终的块地址。

其中,底层编码器的电路由1个最高优先级电路和1024个匹配计算单元组成[11]。CAM阵列的结果会输出给相应行的匹配计算单元,得出不同配置下的匹配结果MOUT;在80 bit模式下,mf0,mf1,mf2和mf3中只要有一个匹配,则输出是匹配的,并用块地址[1;0]来表示是哪一个模块匹配,1 024个计算单元会得出1 024个匹配结果MOUT[12];底层优先级电路则会判断出命中的匹配单元中优先级最高的那个,并将该单元所在模块的块地址作为底层PE的块地址输出[13]。

在上述步骤⑥中,底层PE输出的匹配结果MOUT会作为顶层匹配计算单元的输入,在80/160/320 bit模式中,只要MOUTO或MOUT1中有1个匹配,则输出MO是匹配的,并用块地址来表示相应的CAM阵列[14];顶层最高优先级电路会判断出命中的匹配单元中优先级最高的那个,输出该单元的行地址,同时将该单元的块地址作为该顶层PE的块地址输出。

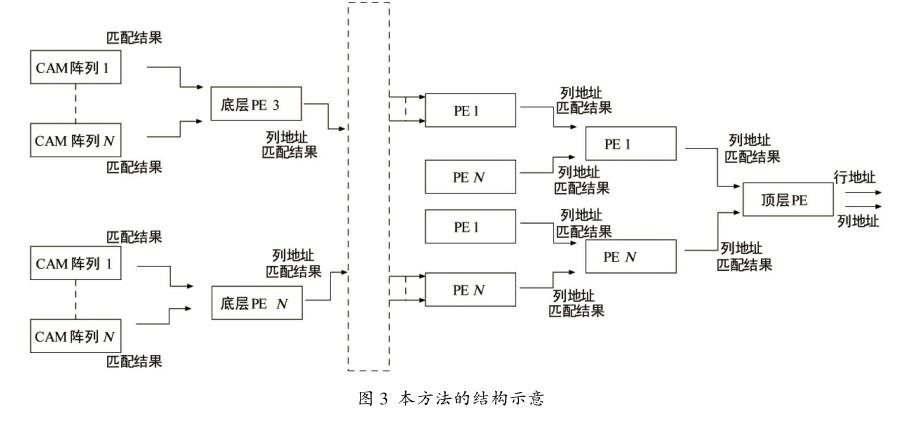

在该优先级编码方法中,8个CAM阵列被分成2组,如图3所示,每组CAM阵列的匹配结果都被输出到底层PE中,底层PE会输出不同配置下的匹配结果,并输出匹配的块地址;顶层PE会根据底层优先级编码器PE的匹配结果判断出最终的匹配结果,并计算出行地址和最高位的块地址。根据该高位块地址,可以选出最终的低位块地址;每个字需2条走线,一条线是BLK3将匹配结果输出给底层PE,另一条线则是底层PE将新的匹配结果输出给顶层PE。

3.3线道数目比较

不同于传统CAM芯片将所有匹配输出都送到一个优先级编码器生成所有地址的方式,本方法中有不同层次的PE,其中顶层优PE只生成行地址,块地址则是在局部编码器中生成,所有输入顶层PE的匹配线结果都会在局部PE中进行简化处理。利用该方式,4种不同位宽的配置的芯片只需2条布线通道,5种位宽的配置也只需3条线道,大大减少了版图对布线通道的需求。同时通过这种方式,一款CAM芯片就可以拥有更多种的位宽配置,在同时支持多种位宽模式时,降低了版图对布线通道的需求,可以使芯片拥有更多种的位宽配置,被更灵活地应用于多重领域。

传统方式所需线道数目是2-1-1,而本方法所需线道数目是-2,如图4所示,传统方法所需线道数目明显比本方法所需的线道数目多。由此可见,本方法能大大减少支持多种搜索位宽的以太网通信芯片对线道的需求,可以使一颗以太网通信芯片具有支持更多搜索位宽的能力。

4结束语

本文针对现有以太网通信芯片的CAM对多种位宽数据的检索模式支持不足,无法满足当前日益复杂的业务需求的问题,从检索时的优先级编码机制入手,提出了一种以太网通信芯片的优先级编码方法。通过对比较单元阵列进行分组,利用不同层次的PE来生成最高优先级的命中地址,其中下层编码器的作用是生成底层模块列地址,并按照不同的位宽配置计算相应字的匹配结果,顶级PE则生成行地址和最终的列地址。该方法能使以太网通信芯片支持多种位宽数据的搜索,同时减少对线道的需求。

参考文献

[1]刘挺.计算机硬件材料的现状及发展趋势[J].造纸装备及材料, 2021, 50(8):62-63.

[2]许培红.基于模糊聚类分析的单词翻译缓存分区管理系统设计[J].齐齐哈尔大学学报(自然科学版), 2021,37(5): 26-30.

[3]王明玉.工业异构网络地址统一分配管理机制研究与实现[D].北京:北京交通大学, 2021.

[4] RAJAEI R, SHARIFI M M, KAZEMI A, et al. Compact Single-phase-search Multistate Content-addressable Memory Design Using One FeFET/Cell[J]. IEEE Transactions on Electron Devices, 2020, 68(1): 109-117.

[5] WANG P, ZHANG J X, ZHANG X, et al. Convergence of Satellite and Terrestrial Networks: A Comprehensive Survey[J]. IEEE Access, 2019, 8: 5550-5588.

[6]丁宪忠.基于非易失存储器的混合TCAM研究与设计[D].濟南:山东大学, 2018.

[7] T·H·金斯利, G·E·帕克斯, Y·夏尔马,等.具有不同物理尺寸,存储器格式和操作能力的存储器装置,模块和具有存储器装置的系统: CN111630504A[P]. 2020-09-04.

[8]康耀鹏,汪鹏君,张会红,等.基于CNFET的三值内容寻址存储器单元设计[J].华东理工大学学报:自然科学版, 2018, 44(5):724-729.

[9]廖澴桓,张跃军,丁代鲁,等.一种密码芯片上的固定位宽密钥产生方法: CN201710200373.7[P]. 2017-09-01.

[10] TAN A J , CHATTERJEE K , ZHOU J R, et al. Experimental Demonstration of a Ferroelectric HfO2-based Content Addressable Memory Cell[J]. IEEE Electron Device Letters, 2020, 41(2): 240-243.

[11]苏童,唐永鹤,蒋烈辉.基于CAM的数据库查询硬件加速方法[J].信息工程大学学报, 2019, 20(2): 217-221.

[12]谢升旭,邢长友,张国敏,等. OpenFlow交换机流表溢出缓解技术研究综述[J].计算机研究与发展, 2021, 58(7): 1544-1562.

[13] OMER M, ZAHID U, HASSAN M, et al. Fast Pattern Recognition through an LBP Driven CAM on FPGA[J]. IEEE Access, 2018,6: 39525-39531.

[14]崔兴龙,方沛昱.一种路由查找方法,装置和存储介质: CN107896194A[P]. 2018-04-10.