一种多源多通道信号采集系统设计

2022-01-25朱紫萌

朱紫萌,于 洵,王 刚,韩 峰

(1.西安工业大学兵器科学与技术学院,陕西西安 710000;2.中国航天空气动力技术研究院,北京 100071)

随着弹载设备的不断发展,对弹载数据采集记录仪的要求也越来越严格。当对巡飞弹载光电吊舱无人机[1]的飞行控制作数据分析时,传统采集卡的体积过大和可靠性不够高,虽然能达到高采样精度和采样率,但是面临导弹内部的高冲击和高过载环境[2],普通采集卡难以满足需求。文中提出一种高集成度的数据记录仪设计方法,该记录仪具有高精度高采样率,同时具备高可靠性和低功耗以及微小体积和质量,可适配于弹载无人机。传统采集卡通常不考虑体积大小,通过大规模模拟电路设计达到更高更稳定的采样;文中通过简单的电路设计和FPGA 核心采集时序设计优化使采集效率更高,硬件更简单易调试,软件更便于移植。传统弹载数据记录仪在使用USB 或串口通信时通常会面临无法实时监测数据或数据传输缓慢的问题[3],遥测数据会导致信号传输不稳定,故通常采用“先记录再读取”的方式;该设计通过FPGA 高速采集算法,同步采集信号和传输信号,实现了设备测试期间的实时监测,非测试期间的大容量存储。

1 系统总体架构及方案

1.1 系统指标要求

由于弹载系统装置于无人机的光电系统上,故有如下特殊要求:

1)高采样率:冲击信号需达到100 kHz 的采样频率,其余信号需达到10 kHz 的采样频率,且要求所有通道并行采集和处理。

2)低功耗:该系统用于无人机载光电系统,故需选用低功耗的器件和芯片。

3)高精度:此系统采集数据用于无人机飞行控制和安全性保证,采集精度要求为0.5%FS。

4)多源:要求分析弹内收到的冲击、振动、过载、温度信号,其中的力学物理量为正交三轴方向,共采集10 路信号。

1.2 系统总体设计

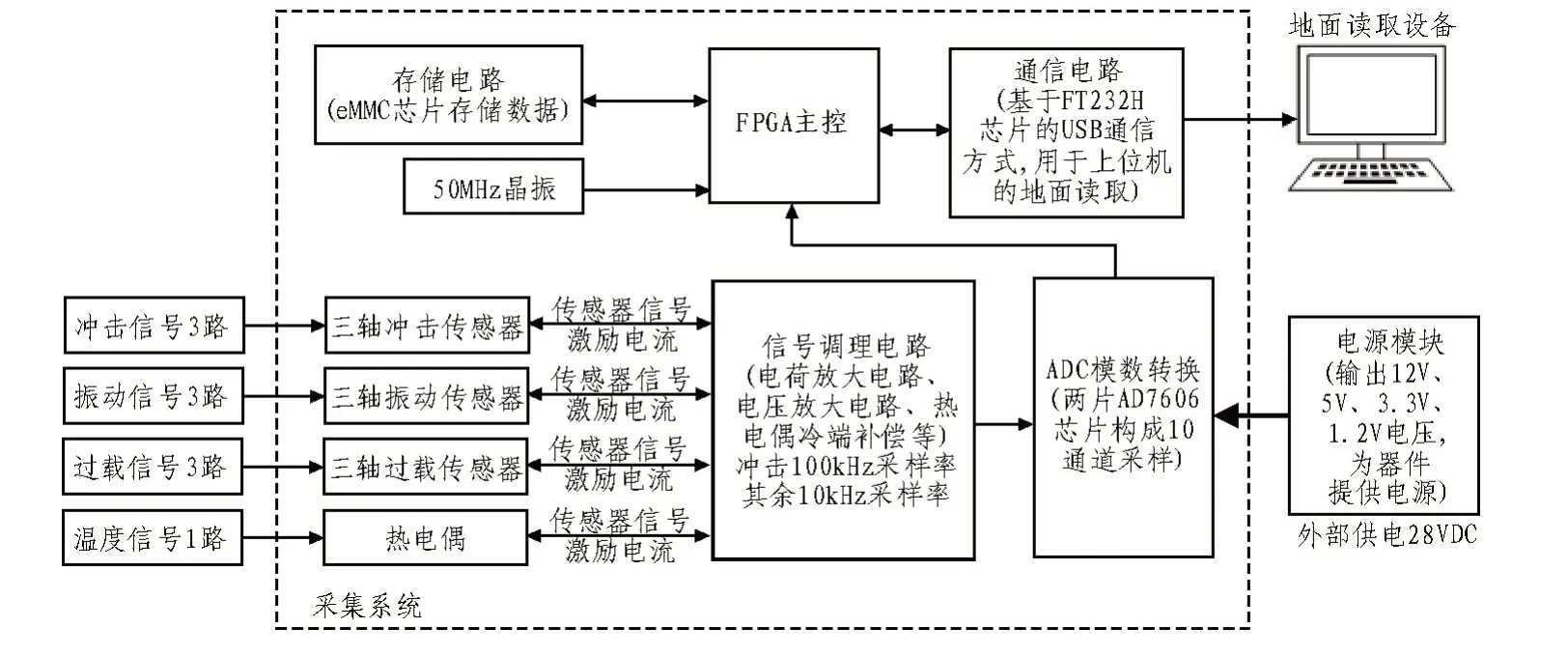

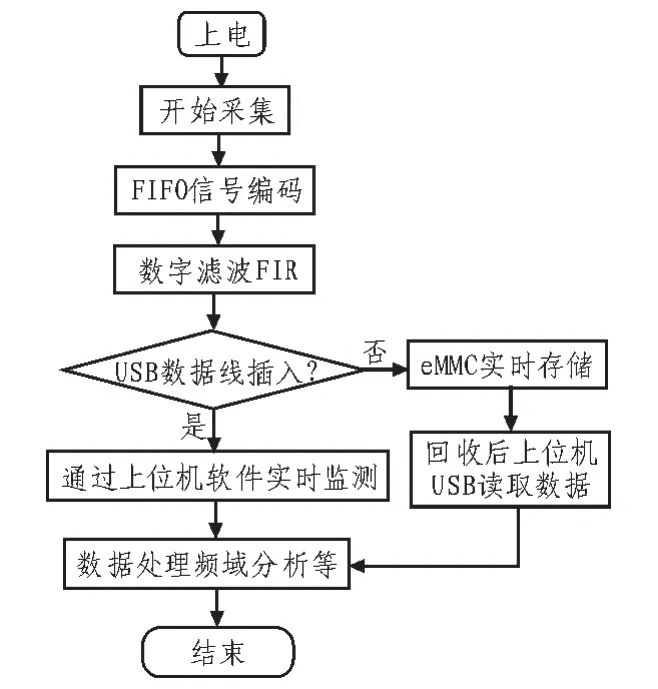

系统总体架构如图1 所示,传感器将接收到的冲击、振动、过载、温度信号先通过信号调理电路,将原始信号经过模拟信号滤波、电荷放大、电荷信号转电压信号等操作将其转化为ADC 模数转换器能够采集的电压范围[4],ADC 将其转化为数字信号,进入到FPGA。FPGA对数字信号进行编帧、解码等操作[5],将数据存入到存储卡中。当弹上系统回收以后[6],上位机可通过FPGA 读取存储卡内的数据,将其有序地显示出来;同时在地面做实验时可以直接通过USB 实 时读取 数据[7]。

图1 系统总体架构

2 硬件系统设计

2.1 硬件器件选型

为满足低功耗低成本和性能的平衡,该设计选用了XILINX 的Spartan6 系列FPGA 作为控制核心[8],该芯片具有43 661 个逻辑单元、2 088 kb 的Block RAM 空间,支持DDR3,具有218 个I/O 口,完全满足设计要求。

在ADC 的选型上,为满足最高单路100 kHz 的要求,设计选用ADI 公司的AD7606 模数转换芯片[9]。AD7606 内置8 个独立ADC 通道,可并行采集8 路数据,具有16 bit 精度,最高采样率可达200 kSPS,属于SAR 型ADC。

对于通信方式,该设计选择USB2.0,采用FTDI公司的控制芯片FT232H。FT232H 芯片是一款单通道高速USB 转UART/FIFO 接口芯片,能够用于各种串行和并行I/O 配置,包含专有动态双向数据总线,可通过外部存储器EEPROM 完成其工作模式的配置。它不仅支持异步串行接口(UART),还通过其内建的多重协议同步串行引擎(MPSSE)支持许多同步I/O 接口,如SPI、I2C、JTAG 及FPGA 接口。

数据存储部分作为整个系统的数据载体,承担着存储由ADC 产生的数据的任务。该设备的存储系统选用镁光公司的MTFC16GAPALNA 芯片存储数据;eMMC 存储芯片将NAND FLASH 与控制器MMC 接口封装在一起,控制器负责Flash 的无效块检测、读写、ECC 校验等[10],可大幅度提高数据的读写速度。

2.2 模拟信号调理电路

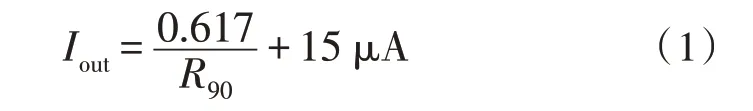

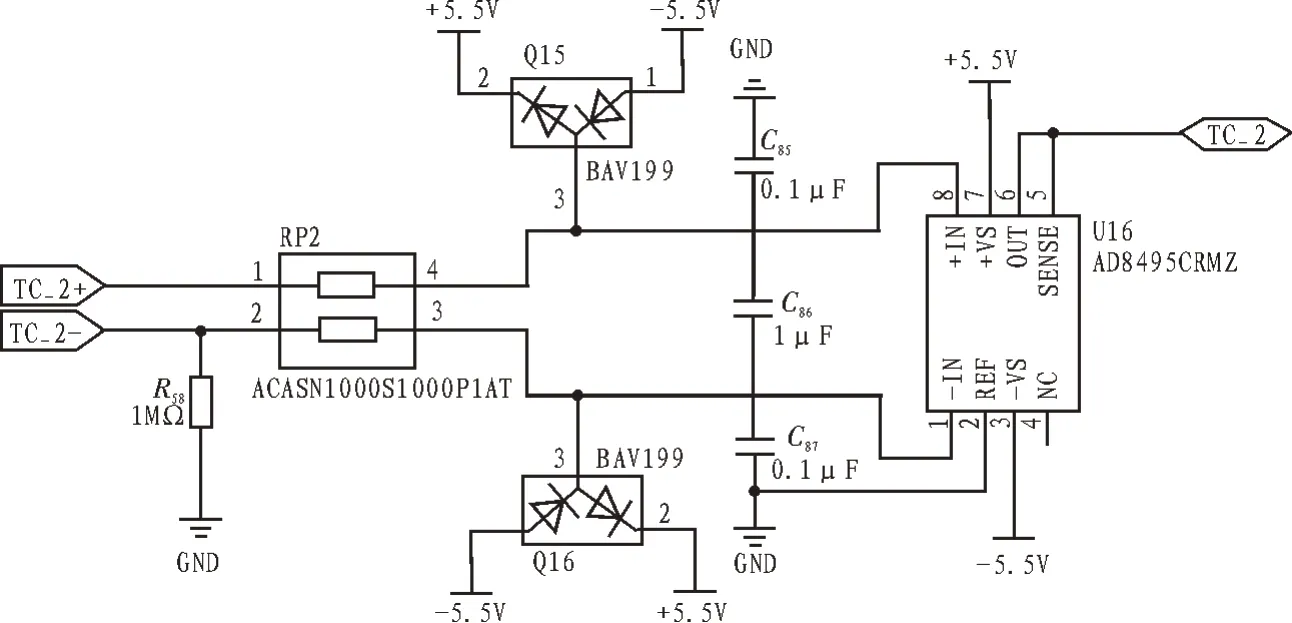

图2(a)所示为调理电路的电流源设计部分,PSSI2021SAY 芯片为一款标准恒流源驱动器,对R90外置电阻改变阻值可输出15 μA~50 mA 的稳定输出电流,为传感器提供激励电流。该芯片集成了内部电阻、PNP 三极管和两个二极管,有助于减少电路板面积。其中,外置电阻和电流输出的关系为:

图2(b)所示为对图2(a)输出的保护电路和运算放大电路。BAV199 是由内部有两个二极管的保护电路,其中公共端3 接输入信号,1 和2 分别接电源正和地,这样信号线上若出现高于正电源的信号则被释放到正电源,出现负电压的信号则被释放到地线上。OPA2171AIDCUR 芯片为一个运算放大器,该芯片规定输入为+2.7~+36 V,具有低失调、飘移和低静态电流的带宽。在该调理电路中,该芯片主要功能是将原始电压信号放大至ADC 能够采集的范围。

图2 模拟信号调理电路

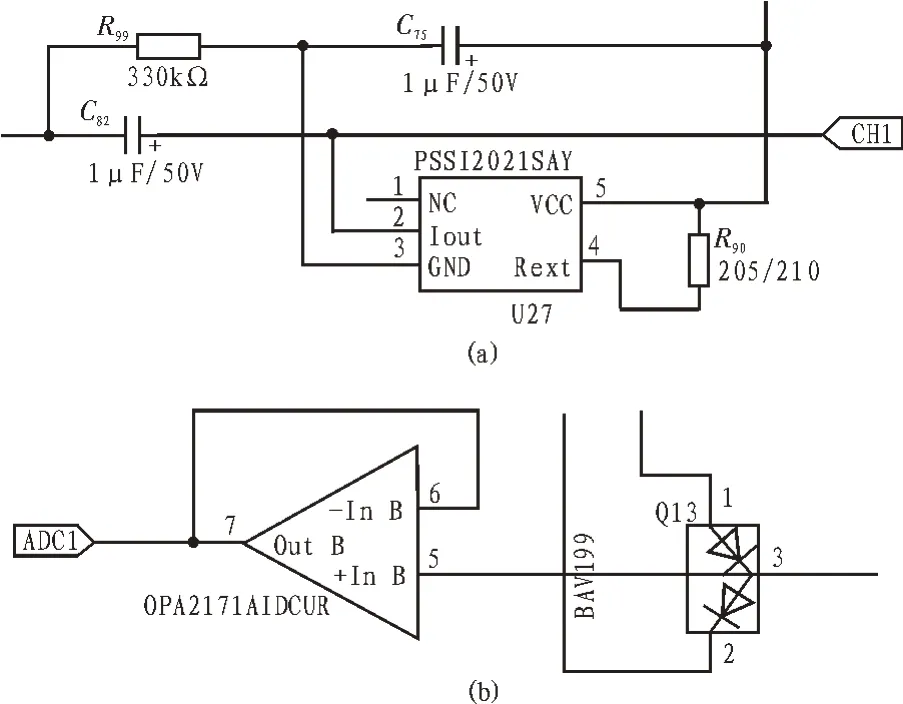

2.3 温度信号调理电路

如图3 所示,选取AD8495 芯片作为设计的热电偶核心调理模块,基于低功耗、高集成度的设计理念,AD8495 满足要求。核心器件AD8495 作为一种热电偶放大器,本身具备的集成温度传感器执行冷结补偿。①AD8495 对25 ℃环境温度进行了优化,额定环境温度范围为0~25 ℃;②固定增益仪表放大器放大热电偶的小电压,已提供5 mV/℃的输出,AD8495 对K 型热电偶的仪表放大增益为122.4;③具有高共模抑制性能,能够抑制热电偶的长引线带来的共模噪声[11]。TC_2 为后端输出电压信号,直接被采集卡采集。

图3 热电偶温度补偿

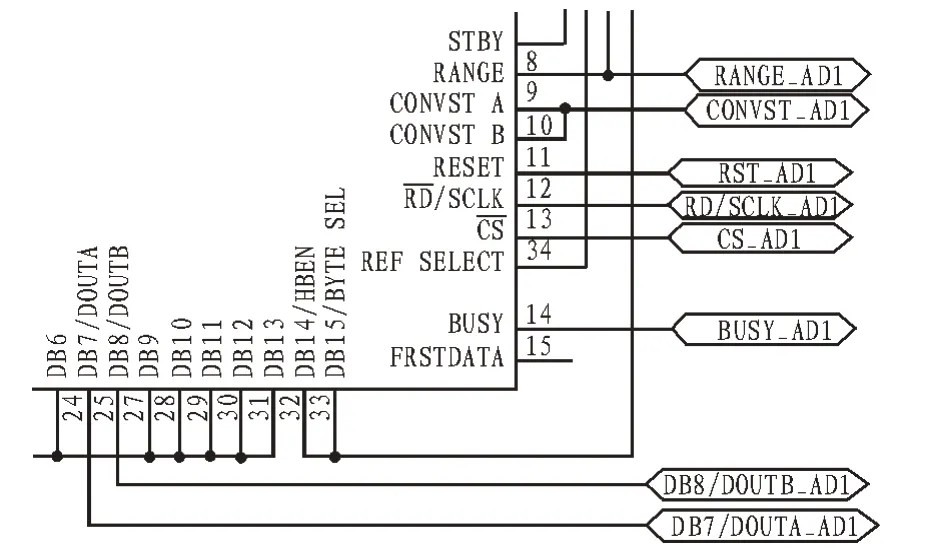

2.4 ADC采集电路设计

两片AD7606 芯片构成采集电路,图4 所示为其中一片和FPGA 交互设计图。由于是同步采样,故两片ADC 的控制引脚通过短接接入FPGA,数据端口独立接入FPGA。

图4 ADC采集电路设计

两片公共控制的信号如下:OS0-3 控制ADC 的过采样倍数;CONVSTAB 将AD 芯片的CONVSTA 和CONVSTB 两个引脚短接在一起,使得ADC 可以同步采样;CS 控制片选;BUSY 表示输出繁忙,CONVSTAB 到达上升沿之后,此引脚变为高电平,直到数据转换完成,此引脚下降沿表示数据已经被存入寄存器,可以读取;RANGE 引脚输入高电平,表示ADC 的输入电压范围是±10 V;RD/SCLK 设置为SPI协议的时钟。

数据端口如下:DB7/8 为ADC 的串行读数模式的输出端口,DB7 输出为通道V1~V4,DB8 输出为通道V5~V8。

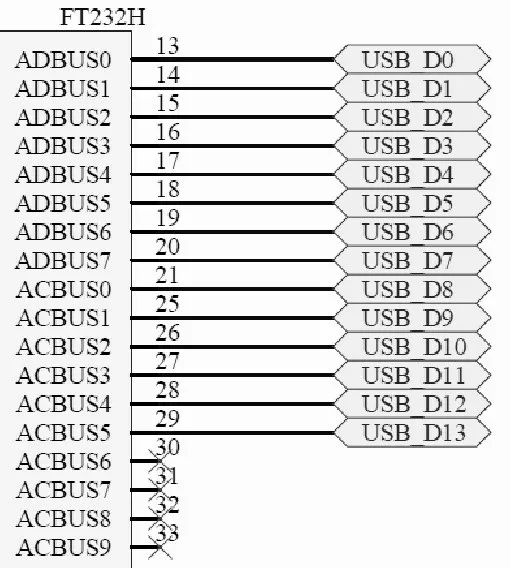

2.5 USB通信电路设计

数据在FPGA 内部经过滤波编码以后直接通过USB 将数据传输到上位机。将FT232H 配置为245同步并行FIFO 模式,传输速率为40 MB/s。USB_D0~USB_D7 接口为一个位宽为8 bit 的双向数据端口,即数据总线。USB_D8~USB_D13 位状态总线,分别是时钟、FIFO 数据可读标志、FIFO 数据可写标志、输出使能、读/写数据输出使能6 个控制端口。四线USB 接口线缆直接接入上位机,采用LabView 编写上位机观测数据。电路设计接口部分如图5 所示。

图5 USB通信电路设计

3 FPGA逻辑设计

3.1 FPGA逻辑设计

系统FPGA 内部逻辑设计和数据流如图6 所示。

图6 FPGA逻辑流程图

设计采用Verilog 语言在ISE14.7 平台上实现了ADC 数据采集、数据缓存、数字信号滤波、数据存储及通信等功能。

3.2 AD7606加速采集逻辑

现存的多数采集卡常根据ADC 器件的时序图直接设计采集逻辑,在设计灵活度上有缺陷,在采集速度上也容易受到FPGA 的门延时以及状态机等的影响。因此为了系统的灵活性,在器件选型上使用了多功能的AD7606 作为数模转换芯片。

通常为了控制简单,便于编写代码,会选择使用AD7606 的并行读取模式,很少使用串行读取模式。但AD7606 的最大读取速度为200 kHz,并行读取涉及到多个线路的控制,期间的延时会影响最终的效率,且并行读取模式和FPGA 使用同一个时钟,容易出现时序难以控制的问题。

为避免并行模式带来的一系列问题,该设计将AD7606 配置为双通道高速串行接口,将10 个通道的传感器模拟电压值经过A/D 转换成16 位二进制数,然后发送给FPGA 作后续处理。

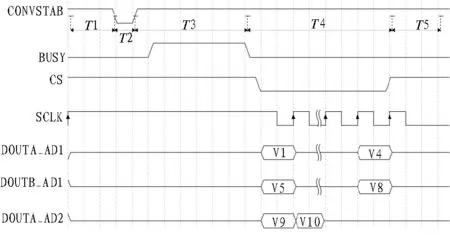

AD7606 转换过程如下:同步采样信号线CONVSTAB 被激励,由低电平变为高电平,表示ADC内部正在进行数模转换,此时外部设备(如FPGA)不能进行读取。当CONVSTAB 变为高电平以后,经过最多40 ns,BUSY 信号变为高电平,BUSY 信号为高表示正在转换数据,不能读取。BUSY 信号的高电平时间为转换时间,介于3.45 μs 与4.15 μs 之间。当BUSY信号变为低电平时,表示数据已经转换完毕[13-16];CONVSTAB 在后续也会再次下降,CONVSTAB 高电平脉冲时间为25 ns。片选CS 必须在BUSY 下降沿之后才能使能,CS 有效时FPGA 才能读取数据。当运行在并行模式时,FIRSTDATA 会在第一个通道读取期间产生一个高脉冲;当运行在串行模式时,FIRSTDATA 会在读完第一通道数据后产生一个高脉冲。

为加速采集速率,在电路设计和逻辑设计上采用了一种加速策略,将多余的引脚悬空,不在逻辑里面体现,从而去掉不必要的判断过程,减小采样间隔,增大采样速率[17-20]。如图4 中的电路设计,系统将FIRSTDATA 引脚和BUSY 引脚悬空,不对其控制。

系统外部使用50 MHz 时钟频率,具体控制时序如图7 所示。根据AD 硬件时序,CONVSTAB 下降沿有效,表示开始启动AD7606;T1 表示设置的等待时间,此处设计为等待20 个时钟(0.4 μs),以保证复位效果良好。T2 为开始启动命令的保持时间,为加速采集,此处判断下降之后,只等待2 个时钟便拉高CONVSTAB,表示数据转换开始。AD7606 的转换时间典型值为4 μs,因此在此处做一个延时等待,即200 个时钟;完成以后立即将CS 和SCLK 置低电平。SCLK 为FPGA 通过PLL 产生的一个时钟,频率为17 MHz;当CS 保持低电平时,在每一个SCLK 的上升沿时FPGA 读取一次信号,每次读1 bit,采用移位寄存器的方式存储。AD7606 的精度为16 bit,故每个通道要使用16个时钟,每个读取周期可以读取4个通道。如图7 所示,DOUTA/B_AD1~2 为两片AD7606拼成的10 通道数据;使用64 个SCLK 可以读完所有数据。T4 为读取数据的时间,T5 为下一次采集的等待时间,可以在FPGA 里面缩短T5。

图7 采集逻辑时序图

3.3 存储逻辑

数据写入过程:在eMMC 进入传输模式之后发送CMD16 命令,设置写数据块长度;再发送CMD24命令,开始单块写操作,将RAM 数据写入eMMC,依次写入起始位、数据位、CRC16 校验码与结束位。数据发送完毕后,eMMC 器件会根据接收到的数据进行CRC16 校验比对,校验成功后才将数据存储到FLASH 里面,即存储完成。

数据读取过程:FPGA 在接收到上位机发出的读取命令后,主动向eMMC 控制器发送读数命令。首先判断eMMC 后端RAM 是否写满,若写满则继续向里面写数据;若未满,则发送CMD17 命令,开始读数据操作。当检测到其为有效时,开始读数据,并且实时CRC 校验,并对读取数据进行计数。当计数到规定数据块长度时,接收端进行数据接收,并将接收到的数据CRC 校验与eMMC 的CRC 校验对比,判断数据接收是否正确,完成一次数据的读取操作。

3.4 通信逻辑

读数据期间,首先FT232H 拉低RXF#信号,表明FT232H 芯片有数据等待读出,此时还不能读数据,总线上的数据并不是真实有效的数据。这个信号相当于一个提示,接收到RXF#信号后,用户(FPGA)需要拉低OE#,使能FT232H 的数据输出,大约9 ns 后,总线上开始出现有效数据,此时用户拉低RD#就可以从FT232H 的FIFO 中读取数据,这里RD#晚于ОE#一个时钟周期动作即可,既可以保证数据准确,也保证了速率。

写数据期间,当FT232H 的数据写FIFO 未被写满时,拉低TXF#,表示FT232H 可以接收FPGA 发送过来的数据。FPGA 拉低WR#,这时数据就能写到FT232H 中。通过状态机对FT232H 进行数据读写。状态机实现简单的读写跳转,上电后程序处于空闲状态,此状态下程序首先检测RXF#是否为0,是则进入READ 读状态;RXF#不为0 时,检测TXE#是否为0,并且判断FPGA 内部FIFO 是否为非空(即empty=0),同时满足时进入WRITE 写状态。在读状态,如果检测到RXF#拉高则回到空闲状态,如果检测到TXE#拉高,或者FPGA 内部FIFO 为空(即empty=1),则回到空闲状态。

4 测试结果及分析

4.1 实时读取功能测试

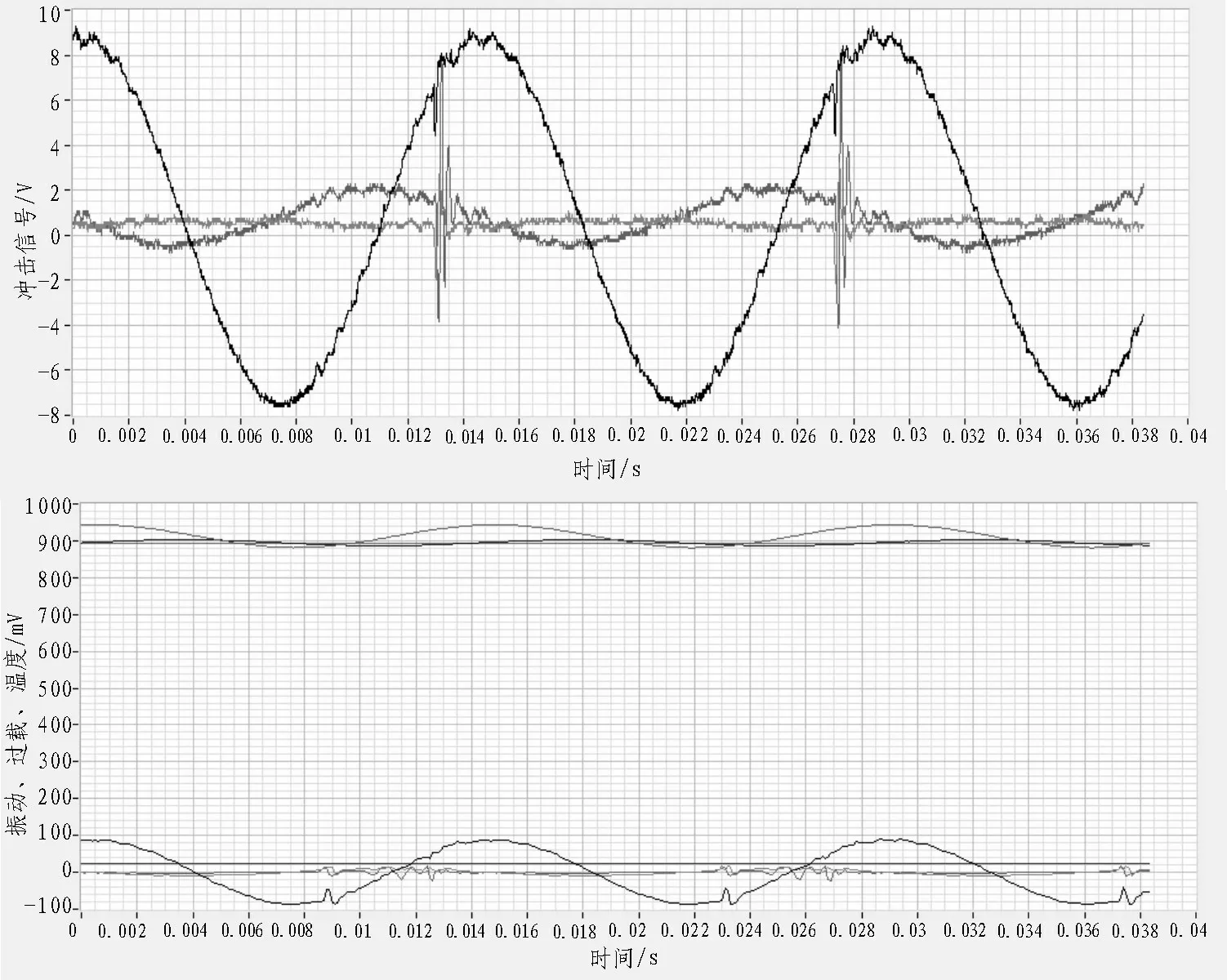

通过USB 读取功能的上位机对系统的实时采集作验证,连接相应的传感器,加一组正弦信号,效果如图8 所示。上侧为冲击信号实时采集界面,下侧为振动、过载和温度信号的实时采集界面。因冲击信号要求100 kHz 的采样率,其余信号为10 kHz 采样率,故使用两个窗口观测,以避免内存溢出造成画面卡顿。

图8 实时采集界面

4.2 数据分析

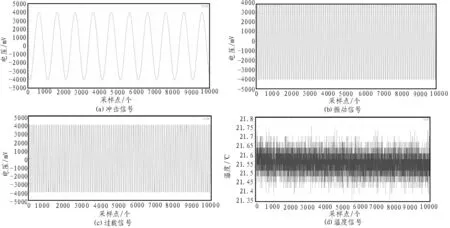

通过模拟信号源分别给采集系统输入幅值为4 000 mV、频率100 Hz 的信号和室温约21 ℃温度输入量的值以测试系统指标。为便于验证数据和分析数据,实验将采用存储模式将数据存储在eMMC 中,通过数据采集系统专用的上位机软件对数据进行读取。采集频率和信号源频率相对较高,图9 中展示了每一个传感器采集10 000个点的采集信号情况。在相同时间采集数量下,冲击信号得到的信号频率低于振动、过载、温度信号频率的10 倍,验证了冲击信号通道采样率100 kHz,其余通道采样率10 kHz。

图9 信号读取

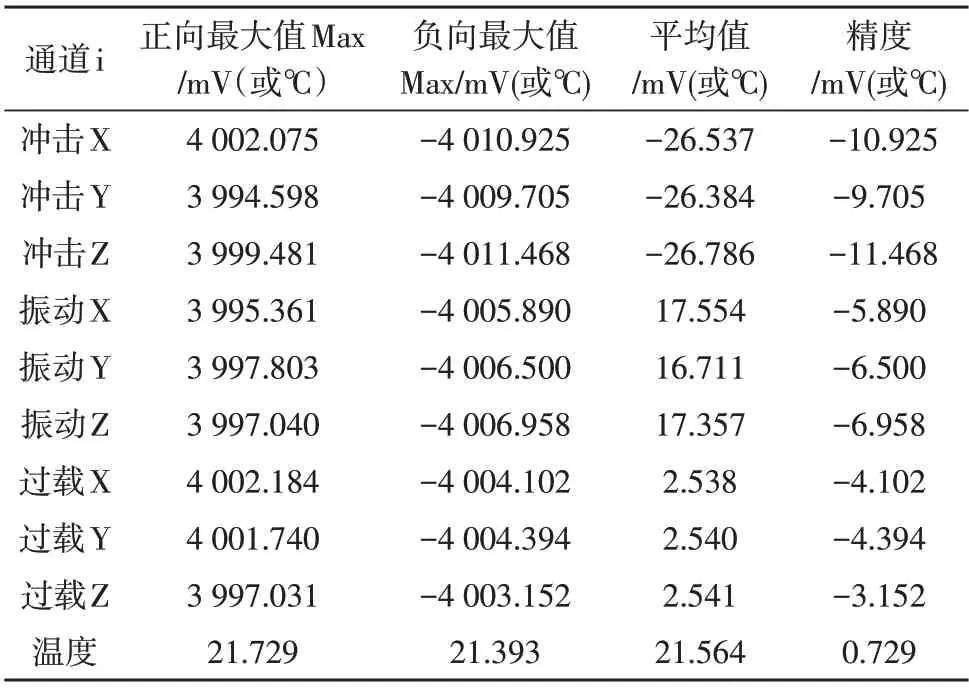

为测试数据采集精度,将采集到的标准源信号数据作计算和处理,对每个通道的峰值、平均值、误差等进行计算。

系统要求对模拟电压的AD 采集精度为0.5%FS,实验的标准输入信号为4 000 mV,所以采集卡容许的精度为0.5%·(±4 000 mV)=±20 mV;温度为0.5%·220 ℃=1.1 ℃。

计算结果如表1 所示。

表1 计算结果

经过实验验证,系统采集卡的采样率和采样精度已满足工程要求,对模拟电压的采集精度比要求的±20 mV 高出大约一倍。

5 结束语

此弹载无人机信号采集系统能够实现多通道、多种类型信号的并行采集。针对ADC 芯片开发使用的FPGA 采集加速优化方法具有实用价值,为其他芯片的FPGA 控制逻辑设计提供了参考方法。实验结果表明,该系统满足采集精度和采样频率的要求,且可以以不同的采样率采集多种信号源。对比传统的弹载数据采集设备,文中所设计的设备具有以下优势:实现对4 个传感器的同时采集;上位机可以直接观察模拟信号曲线。

不足之处在于文中未针对传感器自身的精度提升和校准作出说明,在安装传感器之前应先对传感器进行校正。另外,eMMC 存储设计方面只使用了经典电路设计和时序设计方法,没有对大数据的存储空间作优化,后续可在此方面继续探索研究。