EEPROM 电路关键设计技术*

2022-01-16居水荣

居水荣

(江苏信息职业技术学院微电子学院,江苏 无锡 214153)

在EEPROM 设计中,产品规格包括时序的定义非常重要,另外EEPROM 电路设计中单元电路和高压模块(即电荷泵电路)的设计也是关键,直接影响整个电路的性能。下面分别做介绍。

1 产品规格的定义

EEPROM 产品通常具有以下功能:

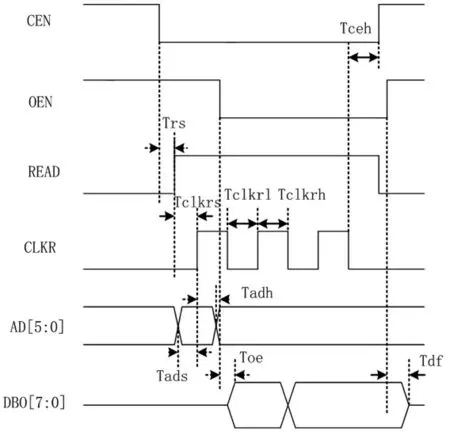

(1)读操作

当RSTN=1,CEN=0,OEN=0,WEN=1,READ=1,CLKR的上升沿锁存地址,地址对应的数据在CLKR 的下降沿,被锁存输出到DBO[7:0],控制器可以在CLKR 的低电平时间从DBO[7:0]总线上获得数据。改变地址,对应每个CLKR 的高电平脉冲,读取数据。

(2)standby 模式

当CEN=1 或者RSTN=0(或者同时满足),则EEIP进入standby 模式,此时EEIP 的功耗非常小。

(3)页写操作

东西部扶贫协作和对口支援,是推动区域协调发展、协同发展、共同发展的大战略,是加强区域合作、优化产业布局、拓展对内对外开放新空间的大布局,是实现先富帮后富、最终实现共同富裕目标的大举措。根据国家东西部扶贫协作部署,福建省福州市连江县对口帮扶甘肃省定西市陇西县,2017年初完善结对、帮扶对象瞄准贫困村和建档立卡贫困人口,精准聚焦于产业合作、劳务协作、人才支援、资金支持等方面开展帮扶工作。

当CEN=0,RSTN=1,OEN=1,READ=0,WEN 的下降沿将触发写操作,在WEN 的下降沿,锁存地址,在WEN的上升沿,锁存数据。在WEN 跳高之后,控制器计时,如果50us 内没有WEN 的下降沿出现,则向EEIP 发出擦写操作的要求。反之,则需要继续等待下次满足50us 的条件出现,才启动擦写操作。另外在满足擦写条件后,还需要等待20us 后,启动高压动作,对EEIP 进行高压擦写过程。

(4)全片擦操作

操作开始与页写操作类似,需要一个或多个WEN的下降沿,但是对应的输入数据对操作无影响。同样等待50us,启动擦操作,此时需要满足全片擦使能信号有效,其余与页写操作的擦过程相同。在完成全片擦操作后,所有array 数据位为全1。

(5)全片写操作

操作开始与页写操作类似,需要一个或多个WEN的下降沿,但是对应的输入数据对操作无影响。同样等待50us,启动写操作,此时需要满足全片写使能信号有效,其余与页写操作的写过程相同。在完成全片写操作后,所有array 数据位为全0。

以读操作为例,其时序定义如图1 所示。

图1 EEPROM 的读时序

2 单元电路的设计

EEPROM 中的单元(cell)结构如图2 所示。

图2 cell 单元的电路图和物理结构

图2 中,EEPROM 的cell 存储单元由两个nmos 晶体管组成,N1 为高压nmos 管,作为cell 单元的选择管,N2为数据的存储管,N2 有两个栅,上层为控制栅,下层为浮栅(floating gate),两层栅之间有gate oxide,浮栅与沟道之间也有oxide,电荷存储在浮栅上。

EEPROM cell 单元的编程激励即进行编程操作的各节点的电压如表1 所示。

3 高压产生电路的设计

EEPROM 中最重要的模块为高压产生电路,原因是该模块产生EEPROM 操作所需要的高压。高压产生电路主要包括一个振荡器电路和一个电荷泵电路。电荷泵电路的整体结构如图3 所示,上述模块分别介绍如下。

(1)振荡器电路

振荡器电路在需要产生高压时刻,在输出端输出3~10MHz 的时钟信号,给电荷泵提供时钟输入。使用pmos偏置管提供电容的充电电流,pmos 管流过电流为4uA,电容大小约为1pf,输出延时后对电容快速放电,充放电的过程形成振荡器的振荡周期。使用RS 触发器,保证可以得到占空比较好的时钟频率输出。

(2)电荷泵主体电路

主体电路共有12 级,可以获得eeprom 工作需要的13v 以上的VPP 电压。每级大电容为0.6pf,小电容为0.08pf,这两个电容需要使用MIM 电容。最后VPP 输出端有8pf 的滤波电容,该电容使用14v 的nmos 管设计。

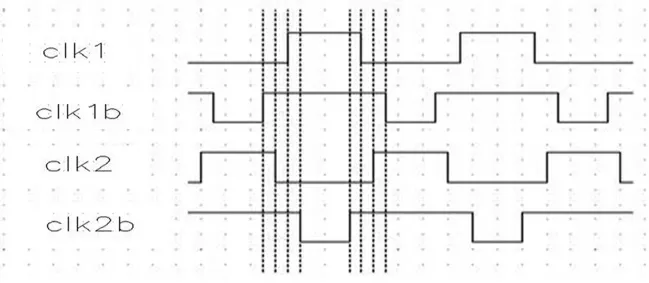

(3)四相时钟电路

电荷泵电路中需要产生四相时钟,四相时钟电路产生的波形如图4 所示。利用简单的延时电路来产生不同相位的时钟信号,利用四相时钟来克服阈值电压对电荷泵的影响,保证每级电荷的有效传递。考虑输出需要15v以上的信号,使用12 级电荷泵电路,其中传输电荷的nmos 管的pump 电容为0.8pf,抵制衬底偏置影响的nmos管的pump 电容为0.1pf。

图4 四相时钟波形

克服阈值电压影响的nmos 管的大小为4/2,对于电荷传输管,每四级为一组相同,依次为8/2、12/2 和16/2。考虑减小阈值电压对电荷泵性能的影响,使用低阈值电压的nmos 管。考虑滤波需要,在电荷泵的输出端到地加8pf 电容。最后,在高压结束时,为电荷泵的可靠工作,提供电荷泵各级节点到电源电压的放电通路。

(4)高压稳压电路

高压稳压电路利用电容分压获得的采样电压与基准电压比较,当采样电压小于基准电压,电荷泵工作,使输出高压上升;当采样电压大于基准电压,电荷泵关闭,输出高压保持,随着高压到地漏电的存在,高压将下降,下降到一定值时,电荷泵将再次工作,以上过程循环往复。电容分压电路的初始电压值,对高压稳压影响较大,所以电路中提供电容电压的复位,保证了每次高压启动时,电容上没有剩余电荷。设计中,电容分压为1∶1∶5,每个电容大小为0.6pf,已知参考电压为1.2v,则输出高压设计值VPPL 为13.2v,VPP 约为15.2v。另外,在高压结束时,提供了高压到电源电压的放电通路。

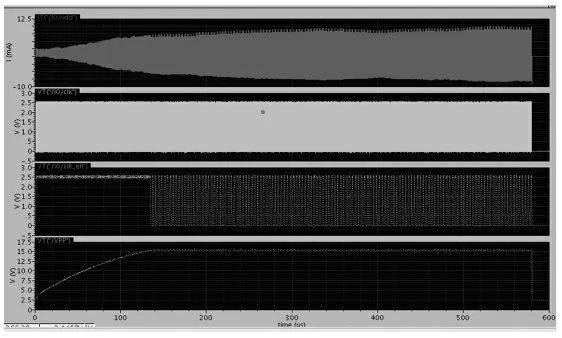

4 高压产生电路的整体仿真

高压产生电路仿真时在VPP 和VPPL 到地之间增加电流负载和电容负载,VPP 到地电流取100nA,VPPL 到地电流取1uA;VPP 到地电容取5pf,VPPL 到地电容取25pf。Vref 输入电压1.2v,iref 输入电流为2uA。图5 为高压产生电路在tt corner,vdd=2.5v,温度为27 度时的仿真波形。

图5 高压电路产生仿真波形

不同仿真条件下的高压产生电路的仿真结果如表2所示。

表2 不同仿真条件下的高压产生电路仿真结果

5 结论

本文详细介绍了EEPROM 电路设计中的关键技术,主要是针对单元电路和高压产生电路的结构、功能及仿真结果等进行了详细描述,为设计EEPROM 提供了参考方案。