基于ARM架构的多通道振动信号采集研究

2022-01-12李毅铭杜冬梅

李毅铭,杜冬梅

(华北电力大学能源动力与机械工程学院,北京 102206)

振动信号是检测机械设备的重要技术参数,许多故障都反映在异常的振动信号中[1]。目前利用嵌入式技术对振动信号进行采集的系统都存在一些问题,高端的系统存在结构复杂、操作困难、价格偏高等问题[2],而低端数据采集装置存在精度不满足要求,通用性差等问题[3]。

针对这些问题,本文选择使用STM32F767内置的模数转换器(A/D),合理配置A/D的性能参数,实现多通道、高精度的数据采集,这不仅有利于降低成本,而且还具有一定实用性[4]。

1 数据采集系统硬件配置

1.1 STM32微控制器

本文选择高性能ARM Cortex-M7 32位 RISC 内核的STM32F767作为主控制器,工作频率高达216 MHz。Cortex-M7内核具有浮点运算单元(Float Point Unit,简称FPU),支持ARM双精度和单精度数据处理指令和数据类型。它还可实现一套完整的数字信号处理 (Digital Signal Processing,简称DSP)指令和一个内存保护单元(Memory Protection Unit,简称MPU),增强了应用程序的安全性[5]。

对于绝大部分振动信号,10 kHz的最大采样率就可以满足实际需求,而更高的采样频率一般用在12位以上的A/D中。对于它内置的12位A/D来说,最大转换速率为2.4 MHz,也就是转换时间最小为0.41 μs(在A/D时钟频率设置为最大的36 MHz,采样周期设置最小的3个A/D时钟周期下得到),完全满足一般情况的数据采集频率需求。同时每个A/D包含19个复用通道,可测量来自16个外部源、两个内部源和UBAT通道的信号,在通道数上也完全符合采样需要。各个通道的A/D转换还有多个工作模式可供选择,分别是:单次转换、连续转换、扫描转换和间断转换[8]。

1.2 A/D数据采集

A/D的作用是将模拟信号转化为数字信号。大多数A/D的自身输入都是来自外部传感的电压信号,输出转换后的数字信号[9]。本文讨论的数据采集方法都基于STM32F767内部自带的模数转换器。A/D的关键技术参数包括采样时间、采样精度、分辨率和转换速率等。

1.2.1 采样时间

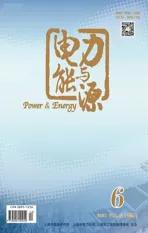

A/D时序图如图1所示。A/D在开始精确转换之前需要一段稳定时间TSTAB,随后等待触发信号,当转换开启后,经过总转换时间,EOC位置1,将转换结果保存至A/D的数据寄存器中,最后用软件对EOC位进行清零,等待下一次转换。

图1 A/D时序图

对于A/D内部要转换的通道来说,首先要确定的就是采样时间。A/D会在多个fA/D CLK周期内对输入电压进行采样,采样时间的周期数可以通过修改寄存器的配置位进行修改。它可以被配置为3,15,28,56,84,112,144,480个周期。每个通道均可以使用不同的采样时间进行采样[10]。

A/D单个通道的转换时间:

Tcon=采样时间+12个周期

(1)

对于配置多通道进行采集的A/D来说,A/D的总转换时间:

应用HITACHI HI VISON Preirus彩色多普勒超声诊断仪,高频探头频率5.0~13.0 MHz。患者取仰卧位,头部后仰或垫高肩部充分暴露颈前区[1]。平静呼吸,甲状腺二维超声扫查发现结节后,首先用二维超声观察其形态、大小、边界、内部回声、有无钙化等,然后切换到弹性模式,行甲状腺超声弹性成像检查。显示结节并尽量固定探头位置,手持探头在结节部位做微小运动,使显示屏压力指示条的数字控制在3~4[2],并使感兴趣区域大于结节的2~3倍[3],用双幅实时显示功能动态观察声像图,对甲状腺结节进行弹性分级。

(2)

式中N——通道数;fA/D CLK——A/D的时钟频率,此时钟来自于经可编程预分频器分频的APB2时钟,fA/D CLK最大配置频率为36 MHz,超过该频率就会使采样数据精度显著下降。

对于每个要转换的通道,都需要尽可能让采样时间长一点,以保证数据有较高的准确度,但是同时也会降低A/D的转换速率。尤其在使用多通道进行数据采集时,合理地配置采样时间成为关键。本文选择将A/D的采样时间配置为3个周期,最大化A/D的转换速率,降低A/D的总转换时间,同时也满足大多数数据采集场景所需的精度。

1.2.2 采样精度

STM32F767的A/D输入范围UREF≤UIN≤UREF+,UREF的输入范围:1.8V~UDDA。UDDA为模拟电源输入,等于UDD:当全速运行时,2.4 V≤UDDA≤UDD(3.6 V);当低速运行时,1.8V≤UDDA≤UDD(3.6 V)。当设置参考电压值为3.3 V的情况下,12位A/D的采集精度如用于采集3.3 V电压,那么理想情况下的识别精度为0.8 mV。

STM32F767有一个内部参考电压Urefint,相当于标准电压测点,在内部和A/D 1的通道17相连。也就是说,可以通过这个通道对其余A/D通道采集的值进行漂移校准,但使用内部参考电压校准就需要多开一路内部A/D 1_IN17。

对于采样精度为12位的A/D来说:

Uchx=UA/Dhx×Urefint/UADrefint

(3)

式中Uchx——计算后的实际电压值,V;UA/Dhx——A/D通道采样值;Urefint=4 095×1.2/3.3=1 489 mV,其中1.2 V是标准电压测点的电压值,不随外部供电电压变化;UADrefint——A/D 1的第17个通道A/D 1_IN17采集的A/D值。

对于提高稳定性来说,一般分为硬件和软件两种方式,硬件上可以在A/D引脚和GND间跨接一个1 μF的电容或者选择滤波器。软件的方式是选择跟自身系统匹配的软件滤波器。

1.2.3 采样频率

本文选择使用PWM定时器触发A/D进行采样,这样就可以通过控制PWM定时器的触发频率来调节所需的AD采样频率。对于STM32F767的定时器来说,除了TIM6和TIM7,其他的定时器都可以用来产生脉冲宽度调制(PWM)输出,其中定时器TIM1和TIM8可以同时产生多达7路的输出。

定时器的溢出时间:

(4)

式中arr——自动装载值;psc——分频系数;fTIMCLK——定时器的输入时钟频率,Hz。

定时器的触发频率即为溢出时间的倒数,用来对A/D进行触发。这样A/D的采样频率就是定时器触发频率,要注意A/D的总转换时间要小于定时器的溢出时间。

2 软件设计

2.1 DMA技术

直接存储器访问直接存储器存取 (Direct Memory Access,简称DMA)传输将数据从一个地址空间复制到另一个地址空间,提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。CPU作为系统运作的核心有着转移数据、计算、控制程序转移等功能。独立的DMA通道提供了一条数据道路,可以直接将数据A拷贝到B,不经过CPU处理。DMA的作用就是防止当出现大量数据转移时过度消耗CPU资源,使CPU可以更专注于更加实用的操作、计算、控制等。

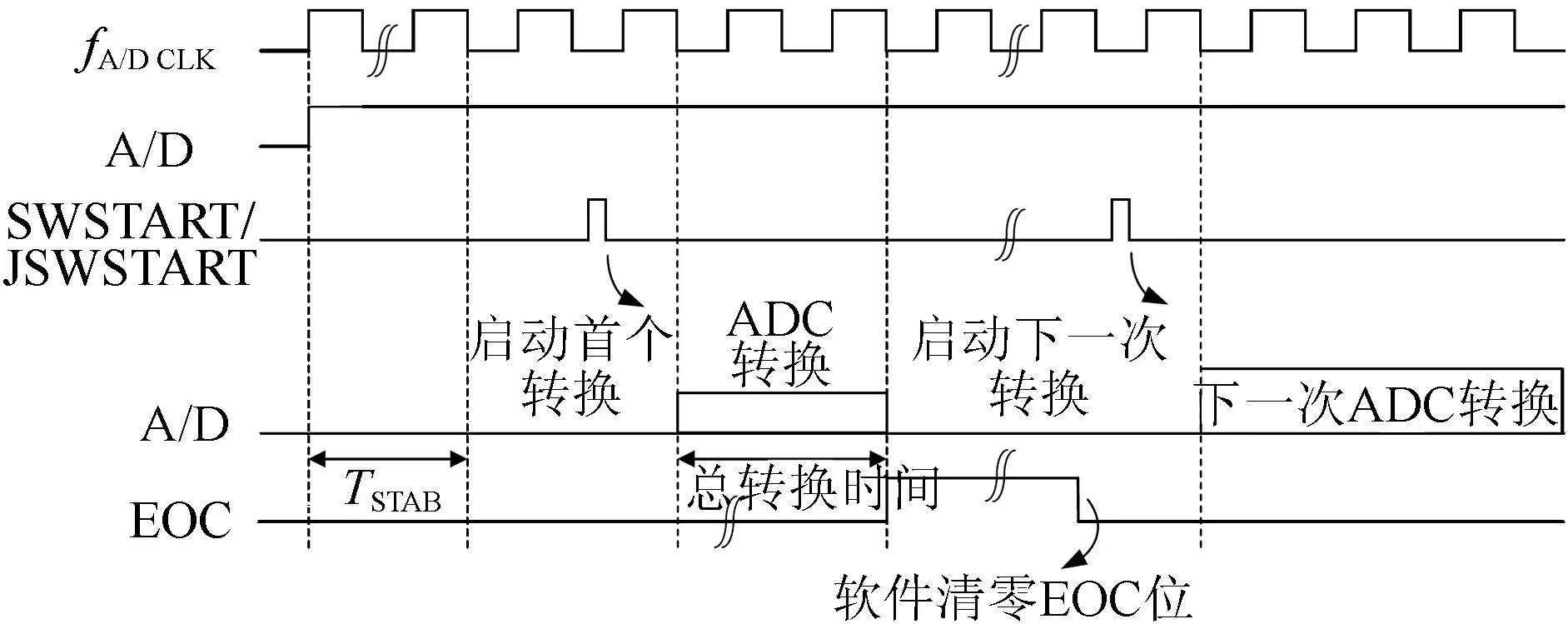

DMA传输工作的开始,首先需要将总线的权限给予DMA模块,然后再结束时将总线权限还给CPU。完整的DMA传输包括:请求;响应;传输;结束。DMA数据传输流程如图2所示。

图2 DMA数据传输过程图

2.2 STM32F767中的DMA模块

本文使用的STM32F767模块包含两个DMA控制器,共16个数据流(每个DMA控制8个数据流),每一个DMA控制器都用于管理一个或者多个外设的存储器访问请求。DMA的每个数据流总共可以有多达8个通道(或请求)。每个数据流通道还配有一个仲裁器,用于处理DMA不同通道间的优先级。在每次传输中还可以配置独占尺寸,设置独占尺寸的通道优先级最高,并且在传输完独占尺寸规定的数据后,传输才会停止,转向下一个优先级通道的传输。

DMA对于数据传输,需要确定的4个核心参数是:数据源地址、数据传输位置的目标地址、传输的数据量和数据传输的次数。

当用户将参数配置好,主要对源地址、目标地址、传输数据量进行配置,DMA控制器就会启动传输,当完成所需的数据传输量,就结束DMA传输,并对外设接口发出中断。当DMA设置为循环传输模式时,DMA每次到达传输终点都会重新开启DMA传输。

2.3 软件设计结构

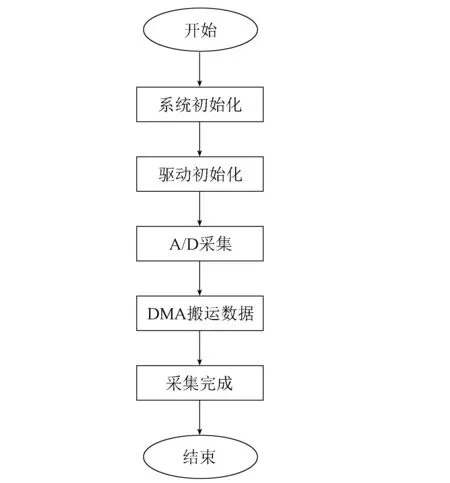

本文的主要工作为数据采集和数据传输。首先应该完成数据采集前的驱动初始化,包括A/D初始化、DMA初始化和系统初始化。A/D的初始化是采集过程中至关重要的一步。本文启用了4个A/D转换通道,转换后的数据存放在专属寄存器A/D_DR中,每次转换之前都要进行初始化。而DMA初始化是因为要将前面寄存器中保存的转换数据搬运至内存中,这样提高了数据的传输效率。系统初始化包括系统时钟初始化、中断源配置、GPIO端口配置和定时器初始化及其参数配置。数据采集过程是系统启动,并进入初始化过程,当完成初始化后,A/D开始进入数据采集过程,然后通过DMA搬运数据,不断循环,直至系统发出停止命令结束。数据采集流程图如图3所示。

图3 数据采集流程图

3 数据采集测试

3.1 电压峰值误差测试

为了检验经过配置后STM32F767内置的A/D多通道采集稳定性和测量精度,本文使用信号发生器GFG-8019G作为信号源,对其发出的符合采集量程的正弦波进行采集测试。正弦波峰值测试值结果如表1所示。表1中的信号频率为50 Hz,采样频率为800 Hz,并通过示波器DS1102C进行同步采集进行结果比较。比较结果表明,STM32F767的内置A/D在合理配置的情况下可以进行多路数据采集,并满足一定的精度要求。 电压峰值误差在2%以内。

表1 正弦波峰值测试表

3.2 同步性测试

当使用A/D的多个通道进行数据采集时,需配置扫描模式,即多个通道按照配置的顺序进行循环采集,同时相邻通道间还存在一定的信号串扰,这些因素使得相邻进行采集的通道间不可避免地存在一定延迟,造成一定误差,影响采集的同步性。这些差异会增大后期信号处理的误差,因此考察相邻采集通道的同步性是个非常重要的问题。

为了验证经过配置后A/D多个通道采集的同步性,本文使用STM32F767中的A/D 3中的通道4和通道5,使用信号发生器GFG-8019G作为信号源,对其发出的符合采集量程的正弦波进行采集同步性测试。

测试一个周期内两相邻通道的采集误差如表2所示。信号频率设置为100 Hz,采样频率设置为1 600 Hz,偏置电压为0.5 V。测试结果表明,STM32F767自带的A/D在合理配置的情况下,相邻通道的延迟误差较小,同步性也可以得到保证。

表2 相邻通道电压值对比表

4 结语

针对数据采集系统中对于高精度、高速率的要求,选择使用STM32F767为主控芯片,利用自带的A/D进行数据采集。最后验证了其4通道同步模数转换的能力,并且具有一定灵活性,同时可以对其通道数、采样时间、采样频率进行更改。经过试验测试,电压峰值误差小于2%,频率测试精度和多通道采集的同步性也满足绝大部分采集过程中的要求。