基于MCM 技术的小型化频率合成器设计与实现

2022-01-08程建斌

郭 鑫,程建斌

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

无线通信系统中,频率合成器是射频收发系统的核心部件,高性能的频率合成器是保证通信系统性能的关键[1-2]。随着电子系统小型化及更高性能的需求,对频率合成器的小型化、捷变频、细步进、低杂散、低相噪设计也提出了更高的要求。而多芯片组件(Multi-Chip Module,MCM)是实现电子装备小型化、轻量化、高性能、低成本专用集成电路不可缺少的关键技术[3-4]。本文详细介绍了一种基于MCM 技术、采用国产GM4704 芯片设计的频率合成器。

2 工作原理及实现方式

频率合成器指标如下:参考输入100 MHz;输出频率13.4 GHz;输出功率不小于5 dBm;相位噪声不大于-85 dBc/Hz@10 kHz;杂散不大于-60 dBc;尺寸15 mm×15 mm×6 mm。

MCM 技术是将多个裸芯片组装在同一个复合基板上,经密封后形成高集成度的微电子组件。其核心思路是摒弃传统的大体积封装元器件,选用集成度更高的裸片(Die)、利用微组装工艺实现电气和射频信号互联。现阶段微组装工艺已经非常成熟,裸片的选择成为制约MCM 实现的关键因素。

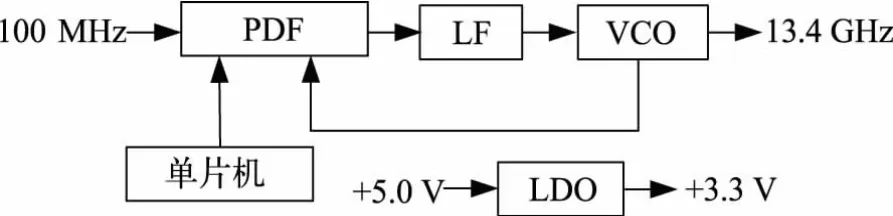

为实现小型化设计,选择单环锁相环(Phase Locking Loop,PLL)实现,原理方案见图1。100 MHz外部参考信号经锁相环直接合成得到13.4 GHz 信号。链路中包含的器件有鉴相器(Phase Detector,PFD)、环路滤波器(Loop Filter,LF,一般会包含运算放大器)、压控振荡器(Voltage-Controlled Oscillator,VCO)、单片机、低压差线性稳压器(Low Dropout Regulator,LDO)等。下面对频率综合器中最关键器件的裸片选择一一进行介绍。

图1 小型化频率合成器方案

鉴相器选择振芯科技公司生产的GM4704,厂家可提供裸片。它是一款低相噪小数锁相环芯片,结合外部环路滤波器、外部基准频率源、压控振荡器使用时,可以实现0.2~10.0 GHz 小数、整数分频频率合成器,其中小数分频频率合成器具有24 bit 固定小数分母,在10 GHz 时能够达到亚赫兹步长精度的频率分辨率。GM4704 的最高鉴相频率可达115 MHz,可获得极低的带内相位噪声性能,归一化相位噪声优值为-233 dBc/Hz。

运算放大器选择ADI 公司的OP284,厂家可提供裸片。它是一款轨到轨运算放大器,带宽4 MHz,可将VCO 的压控电压拉高至18.0 V,覆盖大部分VCO 压控范围。

VCO 选择中国电子科技集团公司第十三研究所的BW434,厂家可提供裸片。压控振荡器芯片工作频率覆盖12.0~13.5 GHz。该振荡器内部集成了负阻振荡电路、谐振电路及变容二极管,同时提供1/2 次谐波频率输出。+5 V 工作电压下,BW434 的输出功率达14 dBm,相位噪声低至-109 dBc/Hz @100 kHz,适合应用于点对点通信、VSAT 等各种通信系统。

单片机选择SILICON LAB 公司的C8051F300,厂家可提供裸片。它是完全集成的混合信号片上系统型MCU 芯片,具有高速、流水线结构的8051,兼容CIP-51 内核,集成高精度可编程的25 MHz 内部振荡器,16 kB 可在系统编程的FLASH 存储器及1280 B片内RAM,可通过串行外设接口(Serial Peripheral Interface,SPI)对鉴相器进行控制。

低压差线性稳压器选择TI 公司的TPS76733,厂家可提供裸片。该稳压器输入4.3~10.0 V,输出3.3 V,可提供1 A 的负载电流。其外围电路简单,噪声特性良好,稳压后为鉴相器供电。

3 参数设计

由器件资料可知,VCO 在13.4 GHz 处对应的压控电压为10 V 左右,所以应选择有源环路滤波器[2],拓扑结构见图2[5]。

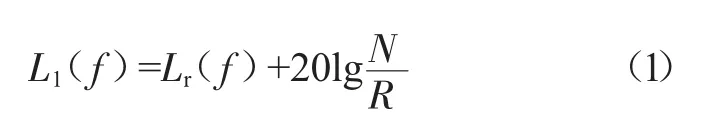

频率合成器采用PLL 设计,在PLL 带宽内,参考信号和鉴相器引入的噪声由如下计算得到[6]。

参考信号的相位噪声对输出信号相噪的贡献L1(f)为:

式中Lr(f)为外部参考晶振的相位噪声,N 为反馈分频比,R 为参考分频比。

鉴相器的基底相噪对输出信号相噪的贡献L2(f)为:

在环路带宽外,相位噪声主要取决于压控振荡器自身的相噪特性[7]。

频率合成器考查10 kHz 处的相噪,设置环路带宽为50 kHz,相位裕度约为45°,10 kHz 处相噪主要由式(3)保证,设置鉴相频率为50 MHz,VCO 的1/2 频率反馈到GM4704 中。

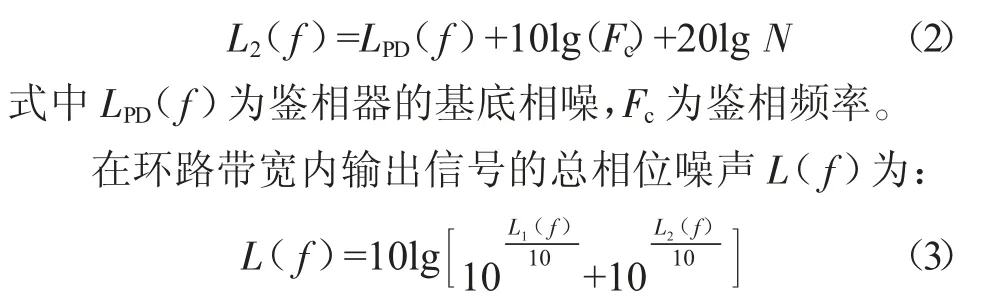

对环路滤波器的开环增益和闭环增益分别进行CAD 仿真[8],结果如图3、4 所示。优化R2、R3参数后,可得到比较理想的环路特性。环路参数见表1。

图3 13.4 GHz 处环路滤波器开环增益仿真结果

图4 13.4 GHz 处环路滤波器闭环增益仿真结果

表1 环路滤波器设计参数

4 实物及测试结果

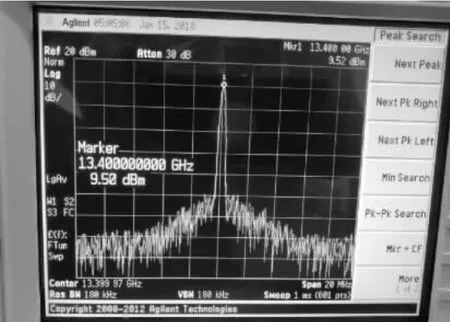

图5 为频率合成器在高倍显微镜下的实物图,可以看出,除阻容器件选用0402 封装之外,所有集成电路均为裸片。通过微组装工艺将集成度大大提高,整个模块尺寸仅为15 mm×15 mm×6 mm。利用Agilent E4440A 对信号频谱和相位噪声进行测试,图6 为输出13.4 GHz 的频谱图,图7 为相位噪声,优于-88 dBc/Hz@10 kHz。

图5 频率合成器

图6 信号频谱测试

图7 相位噪声测试

5 结论

本文介绍了一种基于MCM 技术的X 频段小型化频率合成器设计与实现。所有集成电路选择裸片,利用微组装方式大大缩小了模块体积,另外借助CAD仿真工具,实现了频率合成器的低相噪。出于节约成本的角度,外形结构采用了铝件机加工方式制造,后续外壳可采用LTCC 基板,预计尺寸有望进一步缩小。合适的裸片选择为MCM 技术的核心,本文从频率合成器角度出发,阐述了MCM 技术的设计与实现,未来还可以推广于其他射频模块中,对小型化组件的实现有一定的参考价值。