56G高速背板连接器结构设计与分析

2021-12-29曹永泉陈群强木青峰

曹永泉,王 勇,陈群强,木青峰

(贵州航天电器股份有限公司,贵州贵阳,550009)

1 引 言

随着系统升级、数据处理量的快速增长,客户对高速连接器品种需求和性能提升需求越来越旺盛,特别通信设备领域(如骨干和城域网络传输设备、高端核心路由器等)及IT行业(如服务器、存储、数据中心、高性能计算机等)对高速背板连接器性能要求最高。

目前,市场上通用的连接器速率是10Gbps~40Gbps,未来新一代高速背板连接器的传输速率将达到56Gbps(NRZ),甚至达到112Gbps(PAM4),主要是为满足刀片式服务器内部主板与背板之间的高速数字信号传输而采用的高速互联接口,它们作为高速背板的“桥梁”与“枢纽”,其性能的优劣直接关乎整个系统能否正常工作,在整个通信链路中的可靠性传输至关重要[1-3]。

2 国外产品情况

国外在高速背板连接器领域一直处于领先地位,而且发展十分迅猛。目前,随着系统速率的急剧攀升,国外TE(原TYCO公司)、Amphenol ICC、Molex、Samtec等厂商都已开发出传输速率40Gbps以上的高速背板连接器,其代表产品系列有美国TE公司的STRADA Whisper系列,美国Molex公司的Impel系列,美国Amphenol ICC公司的ExaMAX系列及Paladin系列,各厂家产品图片如图1示。

图1 国外56G高速背板连接器图片

各系列产品均具有其独特的优点,彼此之间不具有兼容性,其共同的特点为:1)采用鱼眼压配形式实现连接器与PCB安装;2)差分对周围至少270°屏蔽+互补屏蔽结构;3)接触件多点接触;4)引脚间距尺寸各不相同,但是都满足阻抗匹配和高密度要求;5)印制板上差分对周围多点接“地”;6)差分对内两条走线电长度在3ps以内。

3 设计要点分析

为了确保56G高速背板连接器在使用中发挥较好的传输性能,我们需要重点考虑连接器设计、工艺设计和印制板开孔设计三个方面。

3.1 连接器设计

连接器设计重点考虑接触方式设计、屏蔽设计、阻抗设计、传输延时设计和插入损耗设计。

(1)接触件方式设计

(a)接触件

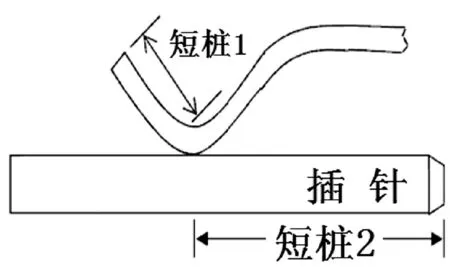

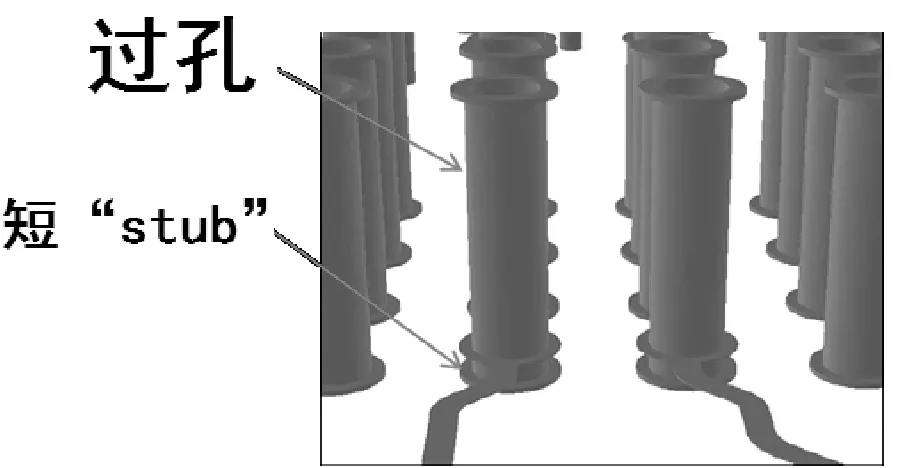

连接器对接接触区是阻抗失配较为严重的区域,通常为防止接触件插合时“兑针”和满足一定接触长度的要求,弹性接触件头部一般伸出一小段作为接触件插合的导向,刚性插针端会伸出较长一段(>1.5mm),如图2(a)所示,正是这两段长度易造成高频谐振,称之为“短桩(stub)效应”,其对插损指标影响很大,如图2(b)所示,连接器在24GHz以后出现了明显的谐振点。

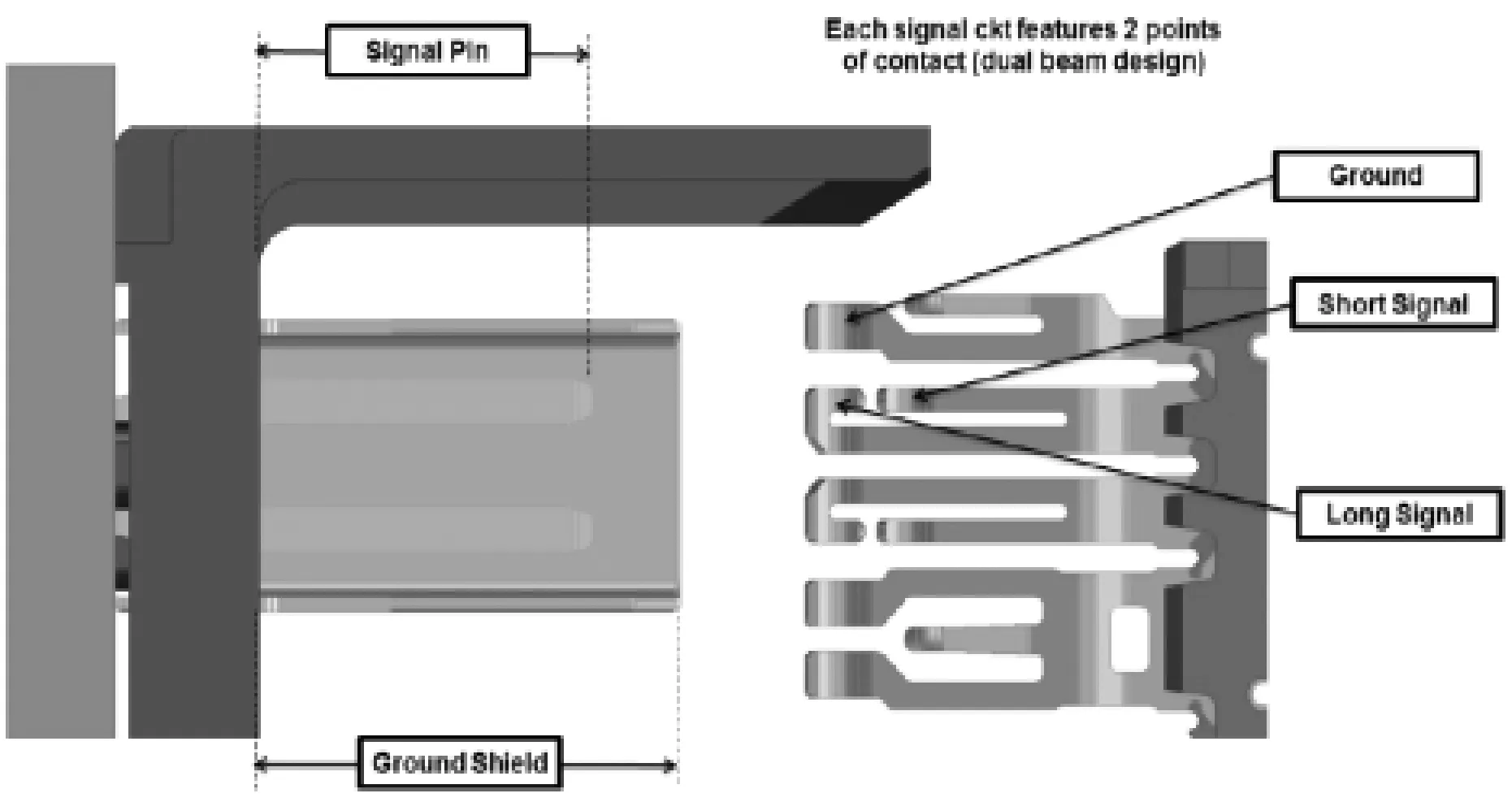

因此,为了降低接触区短桩影响,国外产品在接触件设计上都采用前后多点同时接触的设计方式,如3所示。

(a)Impel系列

(2)屏蔽设计

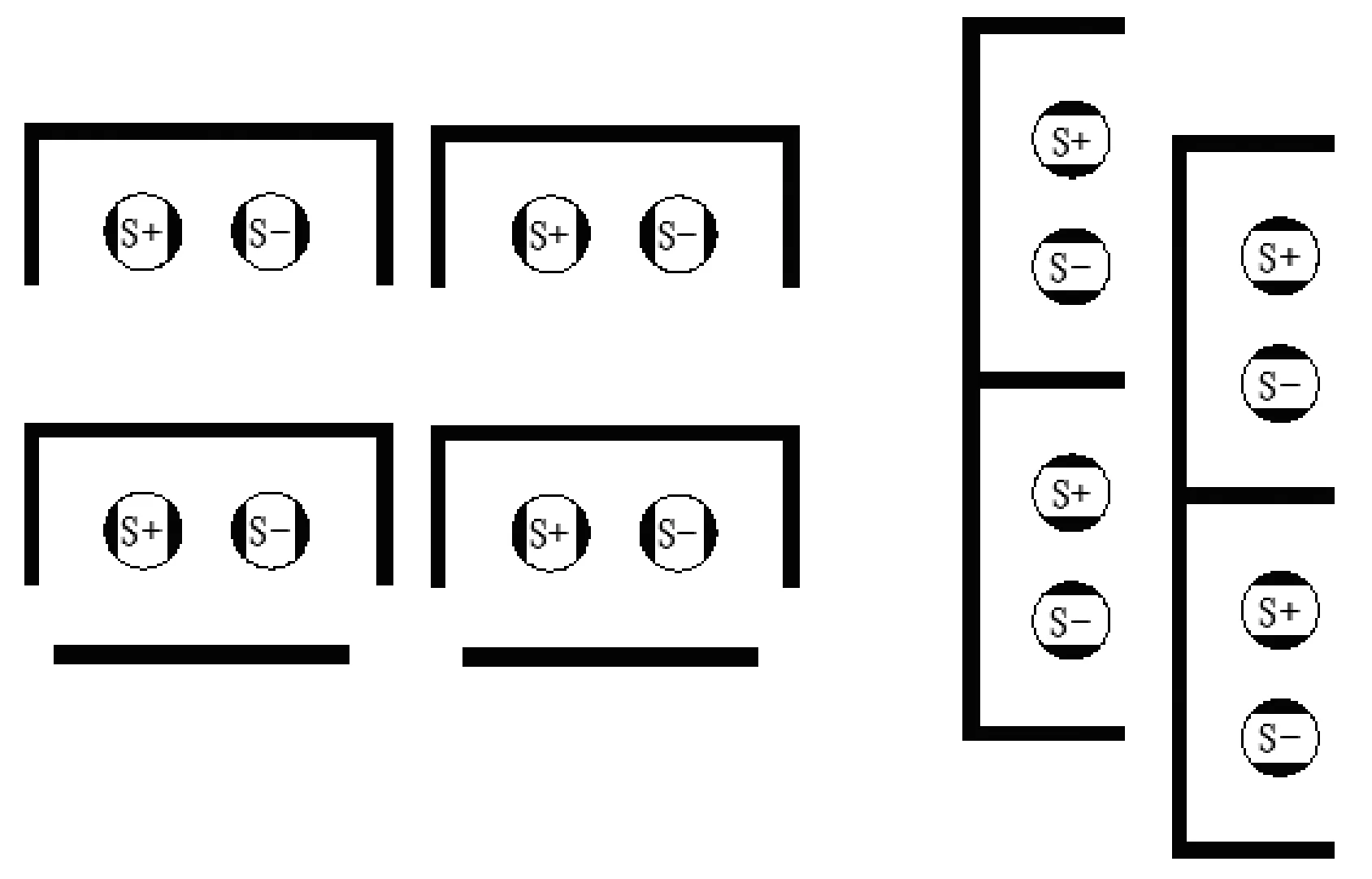

串扰对于高速信号传输影响很大,通常连接器上串扰来源于对接区域、连接器与DC(子板)和BP(背板)衔接区域,或者其它非线性不连续突变区域。因此,为满足56Gbps速率传输要求,屏蔽结构设计非常关键,连接器需要采用金属片全屏蔽或180°屏蔽方式,降低差分对之间的串扰,提升产品传输速率。这种屏蔽方式目前使用较多,如图4所示,国外速率≥40Gbps的产品屏蔽方式。

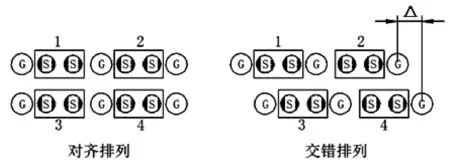

另外,相邻之间差分对交错排列也是降低串扰的有效方法,这主要是差分对之间的电磁场位置发生改变,受到干扰的能量减少所致。如图5所示为相邻差分对错开一定距离Δ示意图,Δ的优化设计对串扰性能提升改善明显。

(a)Whisper Stradal (b) ExaMax

图5 差分对引脚的错位排列

(3)阻抗设计

连接器的阻抗匹配非常重要,它包括连接器自身的阻抗设计和连接器与PCB板的匹配阻抗设计。

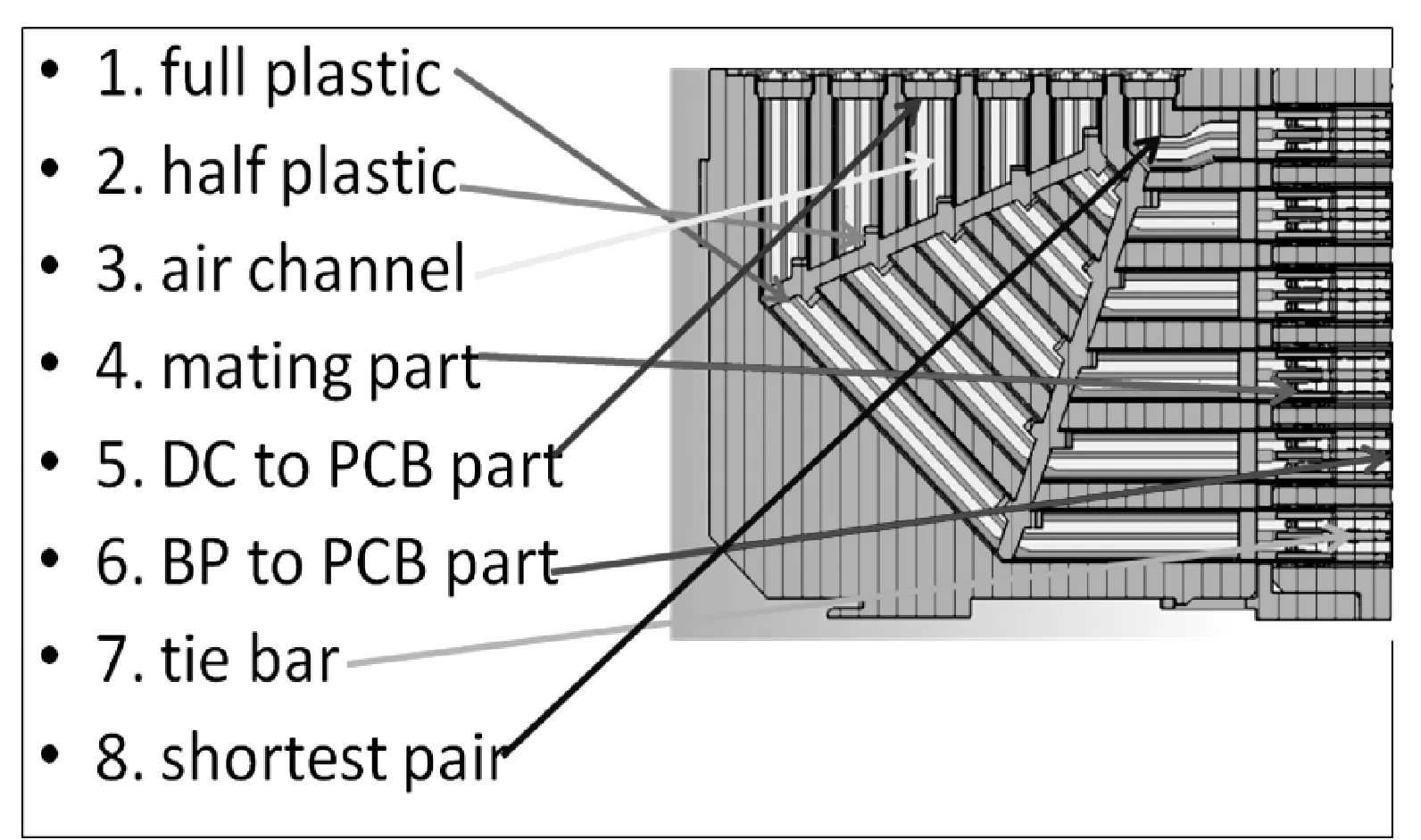

通常我们会用理论公式进行所有连续截面阻抗计算,初步设定好整体结构,然后用HFSS或CST等电磁场仿真软件进行仿真,找出所有不连续部分,并对其进行优化,使其阻抗满足目标阻抗+/- ΔR。如图6所示是背板连接器仿真模型,包括一个直式插座和一个直角插头,需要重点考虑的是接触件接触区、全塑胶区、半塑胶区、空气段、与PCB连接区的阻抗匹配。

图6 背板连接器仿真模型

(4)传输时延设计

差分对间两根传输线的长度要求等长,如果传输线长度不相等,那么差分信号将不能得到同步传输,两个信号间就会出现相位差,从而产生共模信号[4]。通常直式连接器两条传输线的等长控制非常容易,但直角连接器从结构上不可避免的形成不等长的结构,内侧走线会比外部走线段,所以需要进行等长补偿设计。

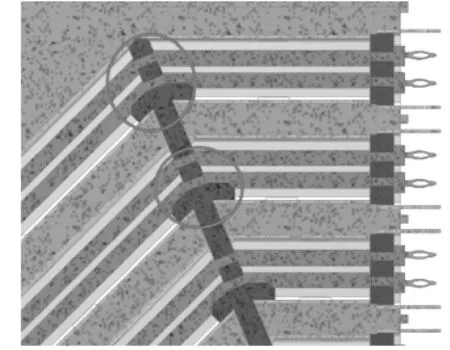

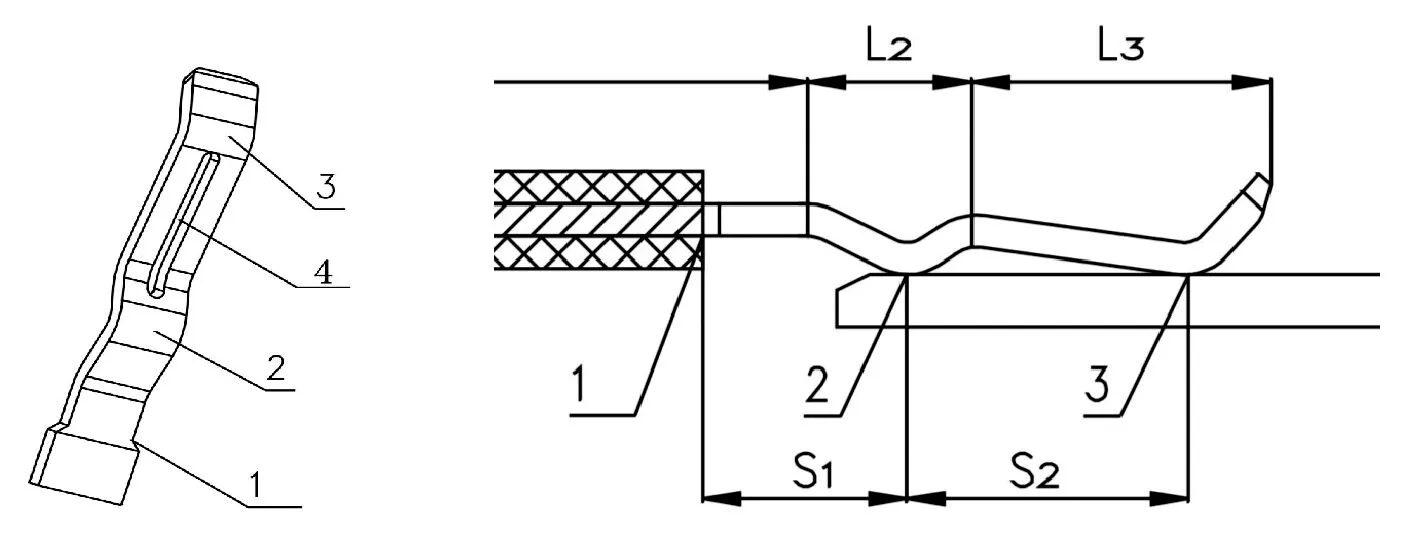

常用的设计方法有:(1)用单端激励求延时差,调整介质线宽满足阻抗和skew要求;(2)用差分激励求Scd21,调整介质线宽使其<-20dB,若成本无明显增加应尽量压低Scd21;(3)最短差分对须单独仿真skew/Scd21;(4)如图7所示,内侧短线增加LCP塑胶以增加延时,同时减小线宽以增加阻抗,或者外侧挖空LCP以减小延时,同时增加线宽以降低阻抗。

图7 时延补偿

(5)插入损耗设计

连接器的插入损耗损耗一般包括导体损耗和介质损耗,当介质为空气时,损耗最小,因此整个传输路径可考虑尽量减少介质材料,即以空气作为传输介质。另外导体的表面粗糙度需要降低,包括电镀后的表面质量,因为随着传输速率的提高,导体的屈服效应越加明显。最后整个传输通道的阻抗一致性控制和减小各个部位的短桩效应(如接触区、连接器与PCB连接区)也需重点考虑。

3.2 工艺设计

产品的工艺设计也要重点考虑,由于产品设计时,通常会偏向优化传输性能方面考虑,但实际生产时,零件加工需要有连料、有避让、有防止变形等多方面的工艺考虑和批量生产的考虑,所以最原始的模型往往会做较大的改动,因此每次改动都要进行相应的传输性能仿真。如图8所示,连料(tie bar)部分需要挖空,为了满足阻抗匹配同步需要金属加宽,另外,接触件Mating点前后也需金属加宽,可以降低容性储能震荡不能立即回稳而产生的感性过冲。

图8 工艺tie bar示意图

3.3 印制板设计

高速PCB印制板的设计主要包括板材选择、开孔设计、反焊盘设计、背钻设计等。

(1)材料选择

由于PCB材料的DF(Disspation Factor)参数会影响插入损耗,因此高速传输会选用较低的DF值材料。典型的低速材料有FR-4材料,一般带宽小于2.5GHz,典型的高速材料有Nelco 4000-13EP、Megtron6材料,其带宽可以达到15GHz,通常高速PCB板材选用M6高频材料用做PCB介质材料。

(2)开孔设计

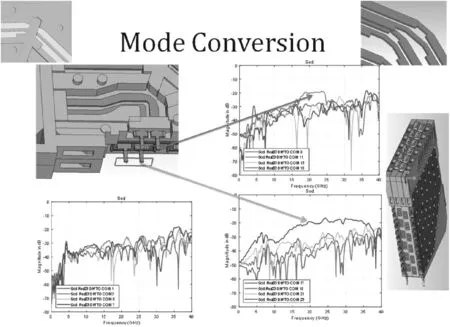

为了获得较高的引脚密度,连接器针脚间距通常较小,在保证阻抗的同时过孔直径也会比较小。目前56G高速背板连接器通常采用的PCB孔径为信号针0.31mm或0.36mm,接地针为0.4mm或0.46mm。另外,推荐信号针周围设置尽可能多的地回路,这样可获得较好的高速性能;多个地针应该均匀的分布在差分信号针周围,这样可以为差分信号提供均衡的回流路径,避免因不平衡的回流路径导致差分对内的实时偏斜,造成模式转换,产生误码。

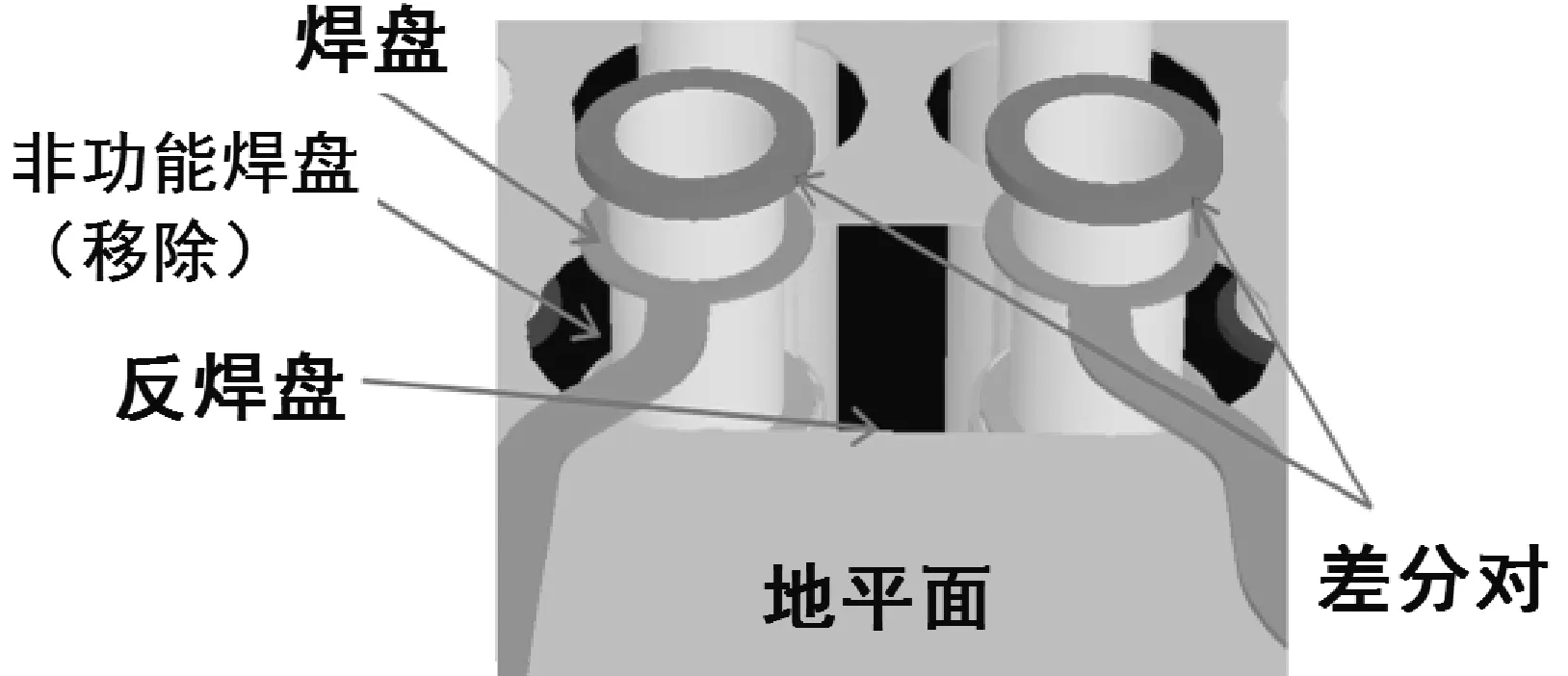

(3)反焊盘设计

如图9所示,反焊盘设计对电性能影响很大,较大的反焊盘直径可以减少过孔的容性耦合,获得更高的阻抗和耐电压性能。但是其减少了PCB布线或走线的宽度,较长的走线在反焊盘下面也会出现不匹配的情况。较小的反焊盘直径尺寸可以减少电磁干扰和临近信号对的串扰,改善了信号走线与“地”之间的参考。因此为了获得较小的反焊盘尺寸,同时考虑阻抗偏小问题,一定要将内部与底层同层的走线非功能焊盘去除。通常推荐所有不用的过孔终止于地平面,以改进isolation,而且减少高速信号反射。

图9 反焊盘示意图

(4)背钻设计

通常,电镀通孔的传输带宽受限于过孔深度,通孔结构成本低,但是会在信号线下面留出一个较长的容性“短桩”。较长的过孔短桩或者信号针短桩都会降低信号传输性能。如图10(a)、(b),同样深度的过孔,印制板走线位置关系到短桩长度,进而影响传输线带宽。为了获得较短的过孔短桩影响,在PCB加工时会把多余的过孔去除,即采用背钻技术减少短桩,如图10(c)所示。留下的部分仅为连接器鱼眼长度,背钻工艺增加了加工成本,但是可以提升高速传输性能,短桩长度可以减少到0.254mm,大大地提升了过孔传输带宽。

(a)短“短桩”

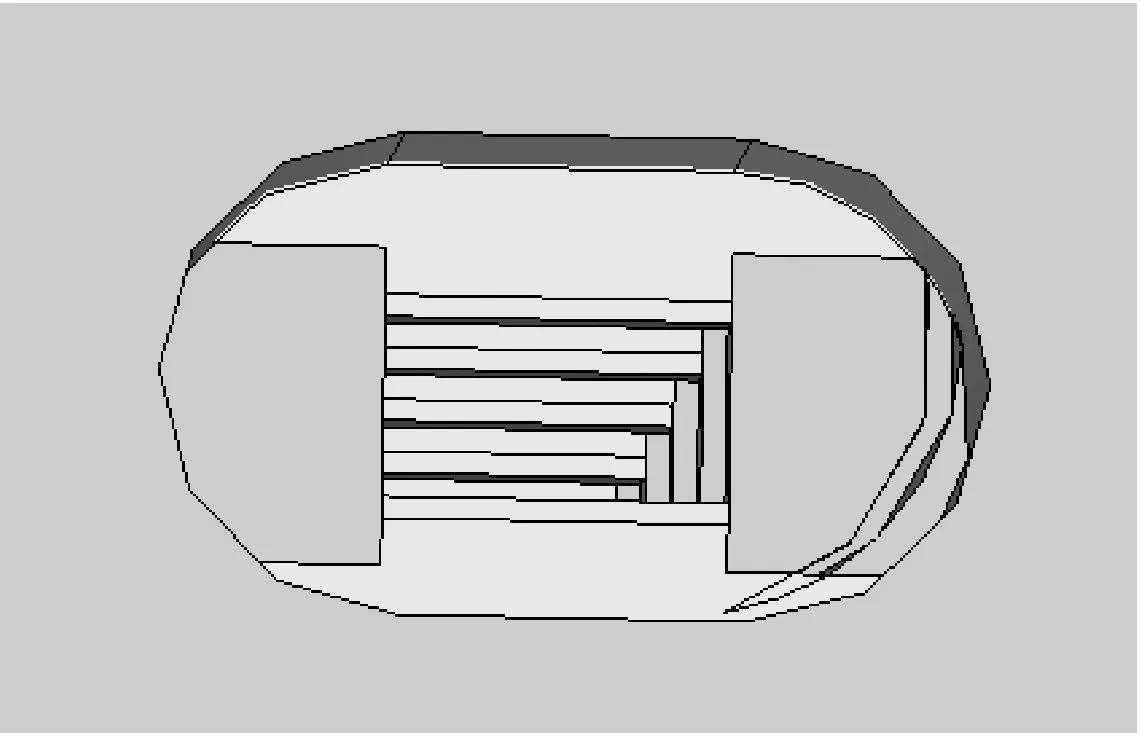

4 产品验证

根据56G高速背板连接器设计、工艺设计和PCB板设计等主要因素的分析,我们开发了一款56Gbps高速背板连接器,如图11所示。该款连接器的接触件采用了多点接触方式,如图12(a),有效地减少接触区的“短桩”效应;在屏蔽方面,通过屏蔽片组合式结构,全链路形成360°包围结构,并进行了错排设计,进一步提升串扰性能,如图12(b)所示。

图11 插座结构

(a)接触区

图13 产品仿真示意图

对于弯式差分对不等长问题,我们根据电磁波在不同介质中传播速度不同的原理,调整了差分对周围介电常数的方法,完成差分对两条线路电气等长设计。并对每一路差分对进行了等长设计和仿真,每个差分对的Scd21均≤-20dB。

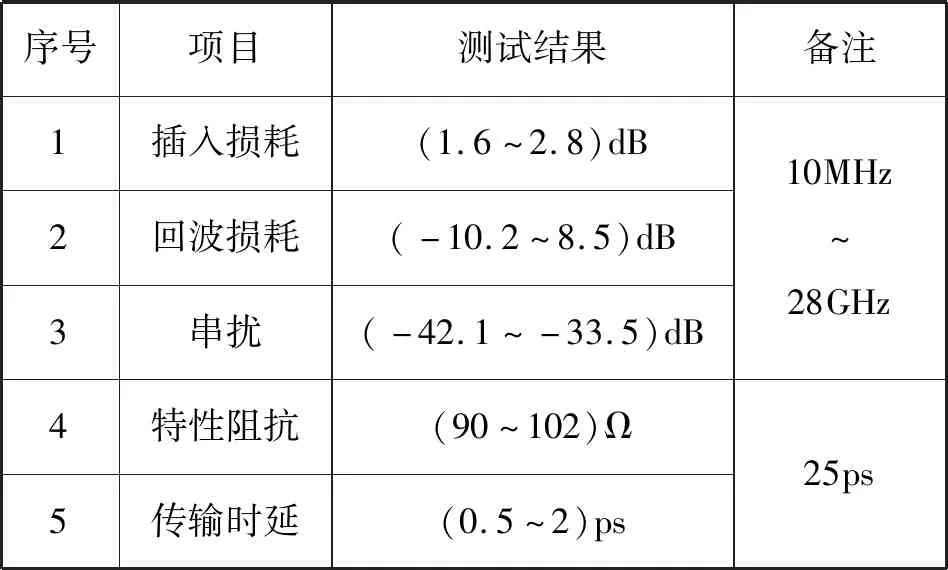

产品最终测试结果如表1所示,指标与国外产品指标相当,满足56Gbps的传输要求。

表1 产品测试结果

5 总结

本文介绍了目前国外传输速率56Gbps的高速背板连接器基本情况,然后对56G高速背板连接器设计方面需要考虑的关键点进行了分析,最后根据设计要点进行了产品实物开发,测试结果满足指标要求,证明设计的合理性,为后续同类高速背板连接器的开发提供了参考与借鉴。