光通信中信号的多通路适配研究

2021-12-27顾艳丽孙科学

顾艳丽,孙科学,肖 建

(南京邮电大学 电子与光学工程学院、微电子学院,江苏 南京210023)

0 引 言

光传送网(Optical Transport Network,OTN)作为新一代光传输技术,从试用到现在,经历了长期的现网验证,其凭借诸多技术优势已经成为干线传输网的主要技术。随着通信行业日新月异的变化,各类通信产品从无到有,从简单到复杂,数据通信业务不断增大,对网络通信容量的需求也急剧增长,这对网络功能提出了更大的挑战。目前干线传输网的传输速率主要为100 Gb/s,400 Gb/s的传输速率也已出现。在应对不断增大的数据传输要求时,几种传输速率并存的情况会持续一段时间[1]。现有的传输网络设备成熟、价格稳定,若能继续使用现有设备实现几种速率的混传是经济、最有效的解决方法。以100 Gb/s传输速率为例,IEEE 802.3ba标准中规定了物理层接口规范,100 Gb/s信号可以在4条或10条物理通路上并行承载传输,即可以在每个波道为25 Gb/s或10 Gb/s的光模块上使用[2-3]。G.709标准中规定光通路传送单元4(Optical Channel Transport Unit 4,OTU4)是采用100 Gb/s信号进行映射复用[3-4],但OTU4接口是否可以重用于基于IEEE 802.3ba的信号开发的光模块有待研究。为了能实现重用,将收到的100 Gb/s信号进行映射,形成OTU4帧后分发到多通路并行接口上,同时能满足IEEE 802.3ba物理层接口规范即可。

通过提高单模带宽来提高以太网速率,并减小开发难度,是改进网络问题的有效办法。但这个发展过程需要时间,在技术还未成熟之前,会有一段过渡时期。在这个期间,能有一个合适的方式很好地衔接发展前后的设备使用和技术变化有着重要的意义。多通道的复用就是其中一个有效的办法。在单通道高速化的基础上进行多通道复用,可以在成本较低的情况下获得更高的传输速率,满足用户更高的传输需求[5-6]。由于目前全球主要为100 Gb/s骨干光传输网,所以下面以100 Gb/s光传输网络为例进行多通道并行接口的设计分析。

1 多通路并行接口实现

用于支持OTN接口的信息有电信号和光信号两种。其中电信号包括光通路传送单元OTUk、光通路数据单元(Optaical Channel Data Unit-k,ODUk)和光通路净荷单元(Optaical Channel Payload Unit-k,OPUk)。OTU4是100 Gb/s光传输技术客户侧的光传送单元[7]。多通路并行接口在OTU4信号底层传输系统中的位置如图1所示。

图1 OTU4底层传输系统图

当100 Gb/s信号经过Mapper/Framer后,输出数据格式为一个通道的并行数据。通过某种方式将这一个通道的并行数据变成多个通路的并行接口信号,这样可以降低对系统时钟频率的要求。选择合适的通道数量,可以将多通道复用到不同光模块的物理通道从而将信号传输出去。设计中考虑该多通路并行接口须能消除传输中的通道延时、便于对齐,并保证在接收方向能够正确恢复和易于恢复。下面阐述多通路并行接口的具体实现方法。

1.1 发送方向的多通道分发

首先从发送方向来看如何将100 Gb/s信号分发到多通道上。对于OTU3信号,由于OTU3帧的尺寸为4×4 080 B,按照16 B为一组,循环分布到4条逻辑通道,所以OTU3信号的多通道旋转和分配可以利用帧开销中的复帧定位信号(Multi-Frame Alignment Signal,MFAS)来决定,MFAS字节有256种组合,将MFAS字节中低两位比特值的4种组合作为OTU3的通道标识。

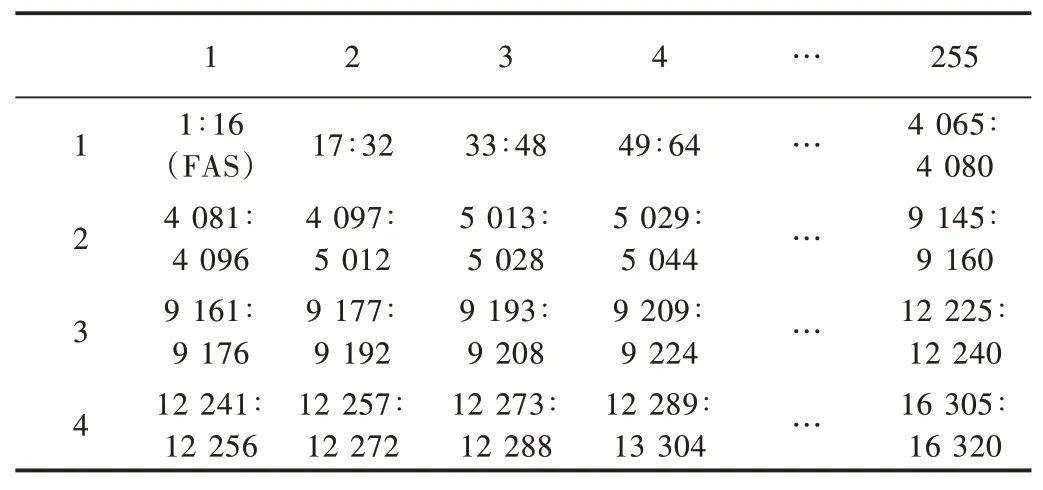

ITU-T G.709和G.798规范中定义了光通路传输链路(Optical Channel Transport Lane,OTL)使用20个逻辑通道[4,8]。OTU4帧的尺寸也是4×4 080 B,将OTU4帧按每16 B一组,循环分布到20条逻辑通道,在到OTU4帧边界通道分配进行轮询调度(Round-Robin,RR)。OTU4帧基于16 B的分组情况如表1所示[9]。循环分布方式如图2所示。

表1 OTU4帧基于16 B的分组

图2 OTU4信号循环分布方式

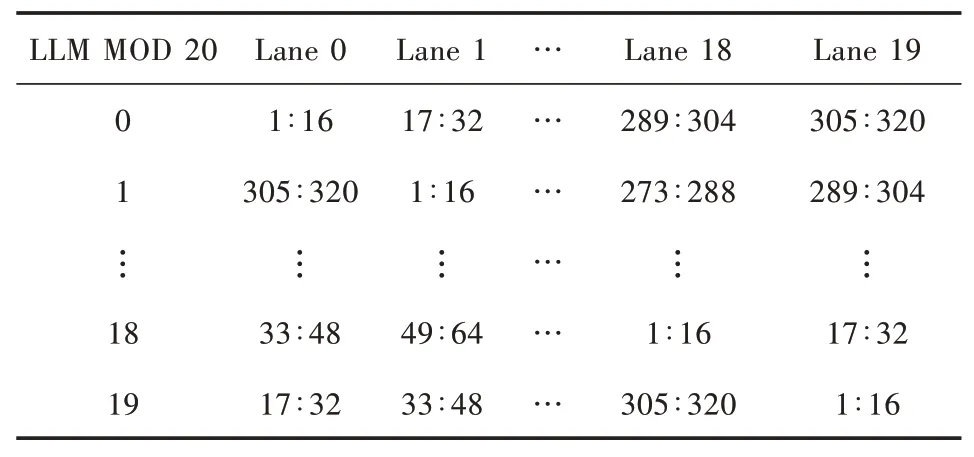

在将OTU4帧分配到20条逻辑通道时,由于MFAS不是20的倍数,不能采用类似于OTU3的标记机制,需考虑其他标识方法。OTU4帧中的帧对齐信号为“F6F6F6282828”,共6 B,48 bit,而依据ITU-T G.798规定,在接收方向的帧对齐流程中仅要求检测32 bit,因此帧对齐字节中的第6 B可借用为逻辑通道标识(Logical Lane Marker,LLM),对逻辑通道标识LLM进行取模得到逻辑通道编号。在接收方向可利用LLM对通道进行识别,调整通道顺序,消除通道间的传输延时后恢复出OTU4数据。将OTU4帧按照每16 B一组,依次递增分发到20个逻辑通道上,规律如表2所示。

表2 OTU4循环分布规律

传输时的最大时延检测范围为3 840帧周期,由于逻辑通道标识LLM随着复帧从0~239连续增加(LLM为8 bit信号,共有256个取值,其中240是20最大的倍数),所以帧周期取240和256的最小公倍数为3 840,这样LLM=0的位置与MFAS=0的位置对齐。

1.2 接收方向的通道重组恢复

在接收方向,从光模块接收到的数据经过比特解复用后,先恢复出每个并行通道的帧,再恢复逻辑通道标识LLM,最后进行时延对齐,重组通道信号。帧对齐、通道标识恢复和多通道对齐的具体实现过程如下。

1.2.1 帧对齐

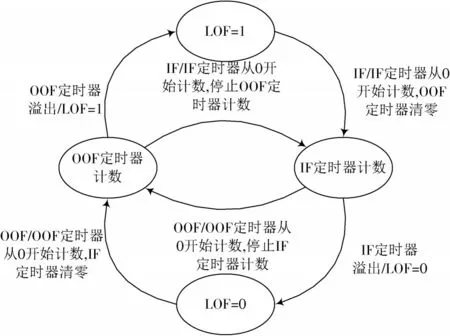

ITU-T G.798标准中规定帧对齐的处理流程中包括帧失步(Out of Frame,OOF)和帧已同步(In Frame,IF)两个状态。帧对齐的过程即搜索FAS中OA1(0xF6)和OA2(0x28)字节的过程[8]。

帧的默认状态是OOF状态,在OOF状态下不断搜索帧中是否存在规律为OA1OA1OA1OA2的字节,即FAS中的前4个字节,若存在,则在1帧之后进入IF状态。在IF状态下,仍然连续对帧信号进行检查,但此时是判断帧信号中是否存在规律为OA1OA2OA2的字节,即FAS中的第3个、第4个和第5个共3个字节,如果连续5帧未检测到正确的字节,则进入OOF状态。当OOF状态持续时间达到3 ms,则产生帧丢失(Loss of Frame,LOF)告警;若IF状态持续3 ms,则LOF告警消失。LOF的帧对齐检测状态机如图3所示。

图3 LOF告警检测状态机示意图

1.2.2 通道标识恢复和多通道对齐

通道标识恢复的过程就是独立恢复出每条通道的逻辑通道标识LLM。连续检测5个16 320(4×4 080)字节周期,得到的数值经过取模运算后与预设的LLM相同,则确认为该通道的LLM,进入恢复(In-Recovery,IR)状态。多通道对齐处理过程包括恢复和脱离恢复(Outof-Recovery,OOR)两个状态。IR状态下,若在连续5个16 320 B周期中检测出一个不一致的LLM,则进入OOR状态。在OOR状态下,最后接收到的LLM将被认为是LLM值。每条逻辑通道根据通道对齐处理结果决定帧丢失恢复(Loss of Frame Recovery,LOR)信号是否生效。如果OOR状态持续3 ms,则LOR信号生效;若IR状态持续3 ms,则LOR信号消失。LOR告警的检测状态机如图4所示。

图4 LOR告警检测状态机示意图

最后将不同的LLM延时对齐后和通道数据重组回原始的OTU4帧。MFAS可以和通道标识相结合提供额外的延时检测范围,该范围最大可以达到“LCM(240,256)2-1”(即1 919)个OTU4帧周期(大约2.241 ms)。另外,在接收方向信息映射到OTU4帧时,将每个OTU4帧中第6个字节恢复为OA2,该字节在发送方向被借用为通道标识。

2 接口的比特复用与解复用

前面提到OTL规定使用20条逻辑通道,而100 Gb/s线路侧的光模块物理通道可能是4条或10条,未来甚至可能是2条或1条。为了保证OTL层设计不受光模块的影响,在物理媒介适配层(Physical Medium Attachment Sublayer,PMA)采用复用和解复用的方法[6]。这样只需修改PMA的设计,就可以适配不同数量物理通道的光模块。在IEEE 802.3ba标准第83章节中对PMA接口的复用和解复用功能进行了说明[2]。PMA收发方向的复用功能框图如图5所示,图中m值为逻辑通道数,n值为光模块实际物理通道数。若图5中采用OTM-0.4v4接口光模块,m值为20,n值为4。OTM-0.4v4接口将20条逻辑通道比特复用到4条物理通道上,即每条物理通道由5条逻辑通道比特交织而成。光模块允许每条物理通道适配任意5条逻辑通道,且这5条逻辑通道的比特复用顺序也可任意。解复用的过程,即将4条物理通道的比特信息返回给20条逻辑通道,逻辑通道根据LLM进行区分,然后组装、恢复原来的通道信号。由于每条物理通道比特复用的顺序是任意的,因此在解复用时,宿端要有能力接受逻辑通道位置的任意性[10]。图5中光模块实际物理通道数n的值随着光模块的变化而变化。接口的比特复用和解复用的设计与实现简单直观,但这只是解决逻辑通道和物理通道之间连接与过渡的方式之一,目前发展较快的FlexE技术可以更好地处理两者之间的耦合关系[11-12]。将前面的多通路接口技术与FlexE技术相结合,可以更灵活地满足不同带宽要求,实现自适应适配,这样在使用中更方便,并更有实用价值[13-14]。

图5 PMA收发方向的复用功能框图

3 结 论

本文设计使用Xilinx公司型号为XCKU5PFFVB676I的可编程逻辑阵列(Programmable Gate Array,FPGA),对多通路并行接口的分发功能和恢复方法进行了实现[15]。FPGA芯片有16个GTY Transceivers,传输速率最高为32.75 Gb/s。将OTU4帧分发到20条逻辑通道的设计满足标准协议,经过比特交织将20条逻辑并行通道复用到物理通道上,可以适配不同光模块。100 Gb/s的以太网设备可以适配不同的光模块,对不同光模块进行通用处理设计,实现网络对接,既减少了设备的更新成本,也降低了技术开发成本。若将FlexO技术、FlexE技术与文中设计的多通路并行接口结合使用[16],则可以在现有技术标准和网络设备的基础上,实现更大的带宽和更灵活的速率。