一种高分辨率图像采集传输系统的FPGA设计

2021-12-16韩卫红

韩卫红

(山西工程职业学院 计算机信息系,山西 太原 030009)

0 引言

图像采集技术广泛应用于医疗、安防系统、工业生产等各种领域,为了能够采集到更高质量的的图像,除了提高图像处理技术以外,对前端图像的采集以及传输也成为研究的关键[1]。为了能够实时地采集具有高分辨率的图像,提出一种高分辨率图像采集传输系统的FPGA设计。在图像传感器选型方面,采用CCD图像传感器采集到的图像质量好,但其成本及功耗均较高[2];对比CMOS图像传感器,其采集到的图像质量好,制作成本低且功耗低[3]。因此系统选用硬件像素达到500万的CMOS图像传感器OV5640摄像头模组,对图像进行实时采集。在图像数据处理器的选择上,对比PC、DSP等,FPGA具有集成度高、小型化、携带方便、并行处理能力强大、以及灵活编程的特点,能够对图像快速采集传输时序进行很好的控制[4]。系统测试性能良好,对高分辨率图像处理技术的发展具有重要意义。

1 系统总体设计

图1 总体设计框图Fig.1 General design block diagram

基于FPGA的图像采集传输系统的总体设计如图1所示,系统主要由图像采集模块、DDR2 SDRAM缓存模块、USB控制模块以及上位机组成。系统工作流程为:FPGA通过串口接收上位机指令,采用SCCB接口实现对图像传感器OV5640内部寄存器的配置。在对图像进行采集时,为保证数据传输无误,采用FIFO对采集的图像数据进行暂时缓存。同时将采集到的图像数据缓存至DDR2 SDRAM中,最后通过USB3.0接口实现图像数据的上传及显示。FPGA通过对各级模块进行仿真及在线调试,验证了其功能的正确性,测试表明采集的高分辨率图像显示良好,符合设计预期。

2 系统硬件电路设计

2.1 USB接口电路设计

系统上采用USB3.0接口(型号为CYUSB3014)实现对图像数据的上传。当FPGA与上位机进行信息交互时,首先需要启动USB控制芯片[5]。由于该芯片硬件设计特点,上电时可以通过IIC接口对该芯片完成初始化启动过程,USB控制芯片的硬件连接图如图2所示。

2.2 高速缓存设计

系统采用一片DDR2 SDRAM芯片对采集的高分辨率图像数据进行实时存储,该芯片型号为MT47H64M16IT,容量为128 MB,标准工作电压为1.8 V.芯片工作时,FPGA采用双边沿对图像数据进行读写操作[6],FPGA与该存储芯片的通讯连接图如图3所示。为简化设计,FPGA在软件设计上采用IP核来控制DDR2 SDRAM芯片,大大节省了FPGA内部资源。

图2 USB控制芯片的硬件连接图Fig.2 Hardware connection diagram for the USB control chip

图3 FPGA与DDR2的外围接口图Fig.3 External interface diagram between FPGA and DDR2

3 系统软件设计

图像采集传输系统的核心控制芯片采用XILINX公司生产的FPGA芯片,型号为XC6SLX75.其强大的数据并行处理能力,能够实现大量数据的快速处理。系统上电后,FPGA通过SCCB接口启动对图像传感器OV5640的初始化配置[7];配置完成后依照图像传输时序从OV5640读取图像数据,由于数据来源于不同的时钟域,为平衡图像传输前后的速率,系统采用FIFO对图像数据进行缓存,进而实现对图像数据的同步处理[8]。将同步后的图像数据存储至DDR2 SDRAM中,并通过USB3.0接口将其上传至上位机进行显示。整个系统通过ISE开发环境实现,软件总体设计如图4所示。

图4 软件总体设计图Fig.4 General design diagram of the software

3.1 OV5640模块设计

为实现对高分辨率图像的采集,系统选用OV5640图像传感器作为前端。系统上电后,首先对OV5640图像传感器进行初始化操作,FPGA中的OV5640初始化模块按照SCCB接口协议实现对图像传感器内部多个寄存器的配置[9],该过程的启动与结束由FPGA进行控制。

3.1.1SCCB接口协议

SCCB接口协议与IIC协议类似,均由两条信号线实现数据的传输,SCCB接口传输主要由单向时钟线SCCB-C以及双向数据线SCCB-D实现。总线空闲时,时钟线和数据线均保持高电平。当时钟线电平在‘1’的状态下,数据线由高电平变为低电平时,标志着传输的开始[10],SCCB启动时序如图5所示。反之,当时钟线电平在‘1’的状态下,数据线由低电平变为高电平时,标志着传输的结束。

图5 SCCB启动时序图Fig.5 SCCB start-up timing diagram

3.1.2SCCB写时序

FPGA对图像传感器OV5640中的寄存器进行配置时,需要对其进行写入操作。SCCB写时序如图6所示,写操作由三部分组成,每一部分由9 bit构成,高8 bit表示地址、数据,最低位LSB表示应答位,写操作时可忽略[11]。FPGA对图像传感器的相应寄存器进行配置时,需要明确OV5640的设备地址、寄存器所在地址,才能够将配置值正确地写入该寄存器中。

图6 SCCB写时序图Fig.6 Diagram of SCCB writing time slots

3.1.3SCCB读时序

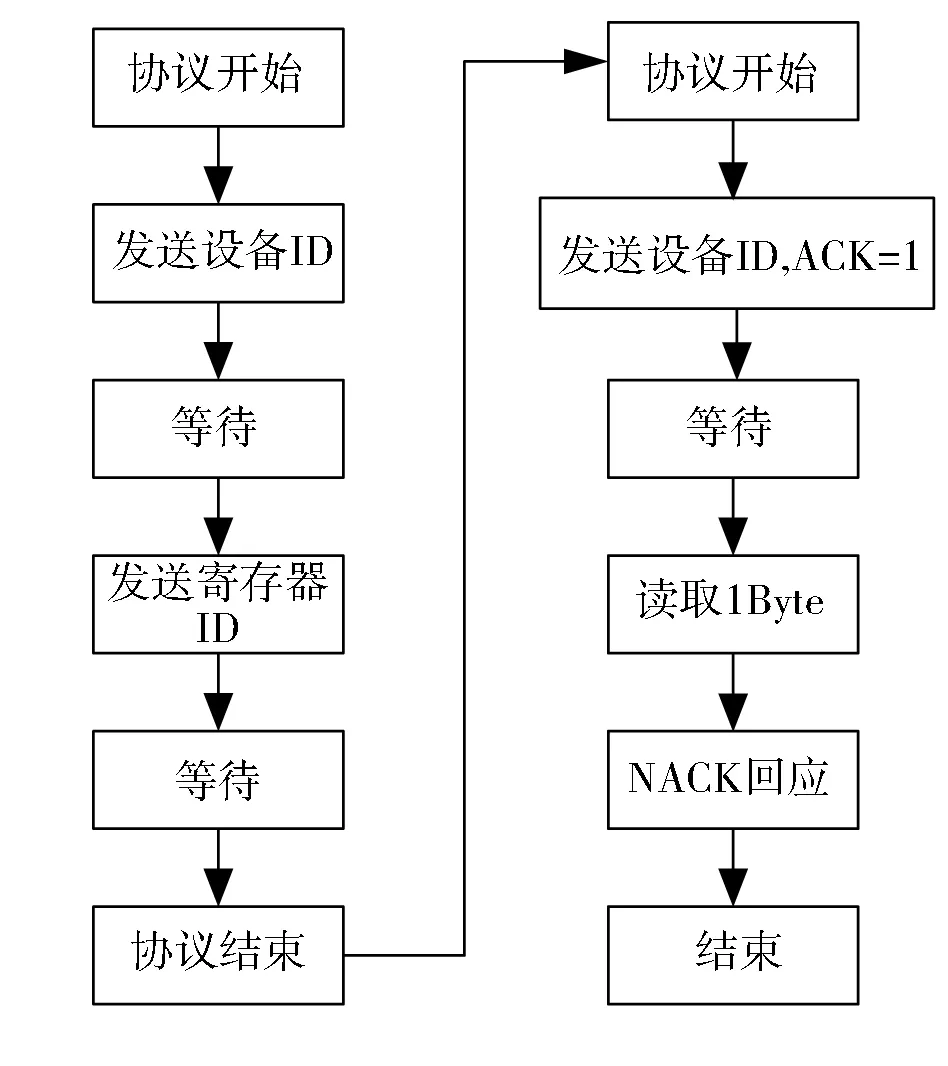

图7 SCCB读时序流程图Fig.7 Flowchart of SCCB reading slots

FPGA读取图像传感器OV5640中的寄存器时,由两段时序实现。首先SCCB传输时序启动后,FPGA发送设备地址至图像传感器,然后发送要读取的寄存器ID,SCCB传输结束。SCCB传输时序再次启动,FPGA首先发送设备地址,并将其最低位设置为1,表示读操作。最后修改数据线SCCB-D的方向,循环读取1 B后,等待NACK回应,SCCB传输结束。SCCB读时序流程图如图7所示。

3.2 OV5640图像输出设计

图像传感器在输出图像数据时,每个像素点的位宽为16.按照SCCB接口协议可知,数据在传输过程中每次只能传输8 bit,因此一个像素点需要两个传输周期完成。OV5640输出的像素周期是数据输出的时钟周期的两倍。设计上采用3个寄存器实现单个像素点的传输时序,其中寄存器REG-1的位宽为8、REG-2的位宽为16、REG-3的位宽为1,系统上电将这3个寄存器初始化为0.当FPGA检测到OV5640输出的时钟上升沿后,首先判断单bit图像行参考信号HREF的值。若HREF=1时,继续判断REG-3的值,若REG-3=0,则将OV5640输出的8 bit图像数据缓存至REG-1,并将REG-3置为1;若REG-3=1,则将REG-1的值缓存至REG-2的高8 bit,将OV5640输出的8 bit数据存至REG-2的低8 bit,然后将REG-3置为0.若HREF=0时,REG-1和REG-3的值清零,REG-2的值保持不变。基于像素时钟与数据输出时钟为2倍关系,因此当数据输出时钟的上升沿到来时,REG-2中的值为一个完整的像素点数据。

3.3 DDR2 SDRAM读写图像数据设计

当FPGA将采集到的图像数据存储至DDR2 SDRAM时,为避免数据传输前后速度不匹配引起的错误,设计上采用两个缓存器FIFO-rx、FIFO-tx来对数据传输进行平衡。当对DDR2进行写操作时,采用状态机的设计形式实现。写DDR2流程图如图8所示,写操作的空闲状态为IDLE,写操作启动时,写入DDR2中的数据首先会存至FIFO-rx,当FIFO-rx中存入一行图像数据后,状态进行连续两次跳转(WRST、WR)后,产生一个写请求信号 Wreq,FPGA在DDR2 SDRAM处于空闲时,完成写操作;若在完成DDR2写操作后,需要对其进行读操作,FPGA将继续采用状态机的设计形式实现对DDR2中存储的图像数据的读取。系统首先将读取图像数据至FIFO-tx中,FPGA检测FIFO-tx的空满状态,决定状态机的跳转状态。当FIFO-tx为空时,无操作;当FIFO-tx不为空时,状态进行连续两次跳转(RDST、RD)后,产生一个读请求信号 Rreq,FPGA在DDR2 SDRAM处于空闲时,完成读操作。

图8 写操作控制逻辑状态转换流程图Fig.8 Flowchart of write operation controling logical state conversion

4 系统测试

4.1 OV5640初始化仿真测试

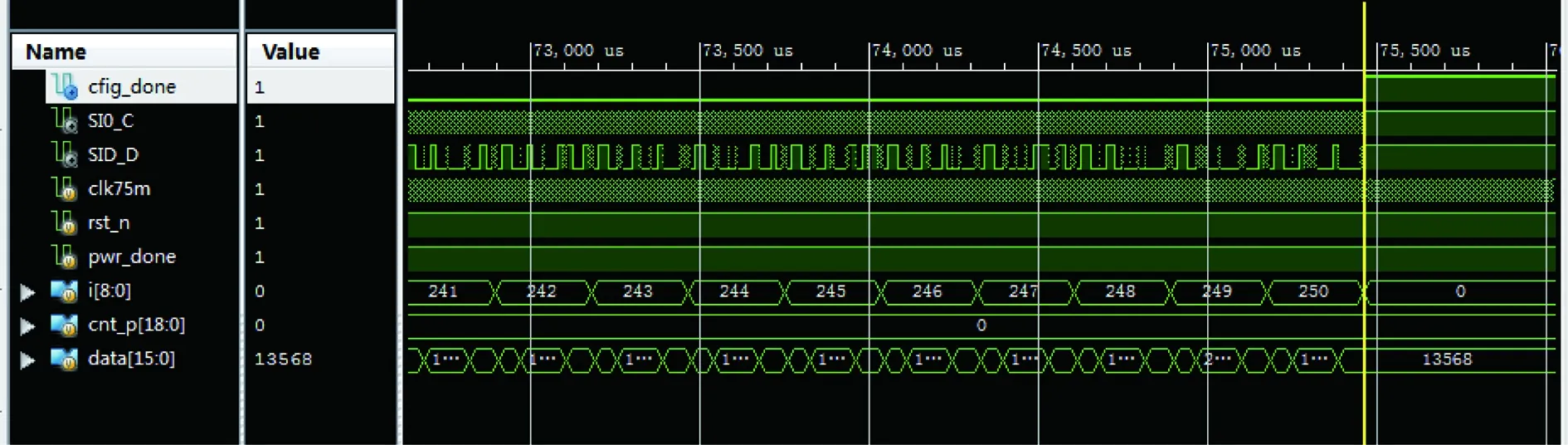

为完成对图像传感器OV5640输出的图像数据的正确采集,首先需要在系统上电时对图像传感器进行正确的配置。根据OV5640数据手册可知,FPGA在上电后需要对OV5640内部的所有寄存器依次进行配置。为验证OV5640初始化功能是否实现,编写测试代码对该模块进行仿真测试,测试结果如图9所示。从图中可以看出,当配置寄存器个数cnt-p计数至250后,cfig-done拉高,表示配置完成。

图9 OV5640初始化仿真测试图Fig.9 Diagram of the simulation test of OV5640 initialization

4.2 DDR2 SDRAM在线测试

为验证DDR2 SDRAM控制模块的正确性,采用在线逻辑分析仪Chipscope对写入和读出DDR2 SDRAM的数据进行对比,为方便对比,设计上写入DDR2 SDRAM中的数据为连续递增的数据。在线测试图如图10所示,从图中可以看出,从DDR2 SDRAM读出和写入DDR2 SDRAM的数据对比一致,验证该模块设计的正确性。

图10 DDR2 SDRAM在线测试图Fig.10 DDR2 SDRAM online test diagram

4.3 图像采集系统测试

系统实物测试图如图11所示,图中①处为图像传感器采集部分,②处为FPGA主控部分以及USB3.0接口部分。

图11 实物测试图Fig.11 Physical test diagram

图12 图像显示测试图Fig.12 Test diagram of image display

系统对图像传感器OV5640采集到的图像通过USB3.0接口进行上传显示,上位机显示的图像如图12所示。从图中可以看出,系统设计实现了分辨率为2 592×1 944的图像采集,采集帧频达到14 f/s,图像显示良好,未发生丢帧错帧现象。

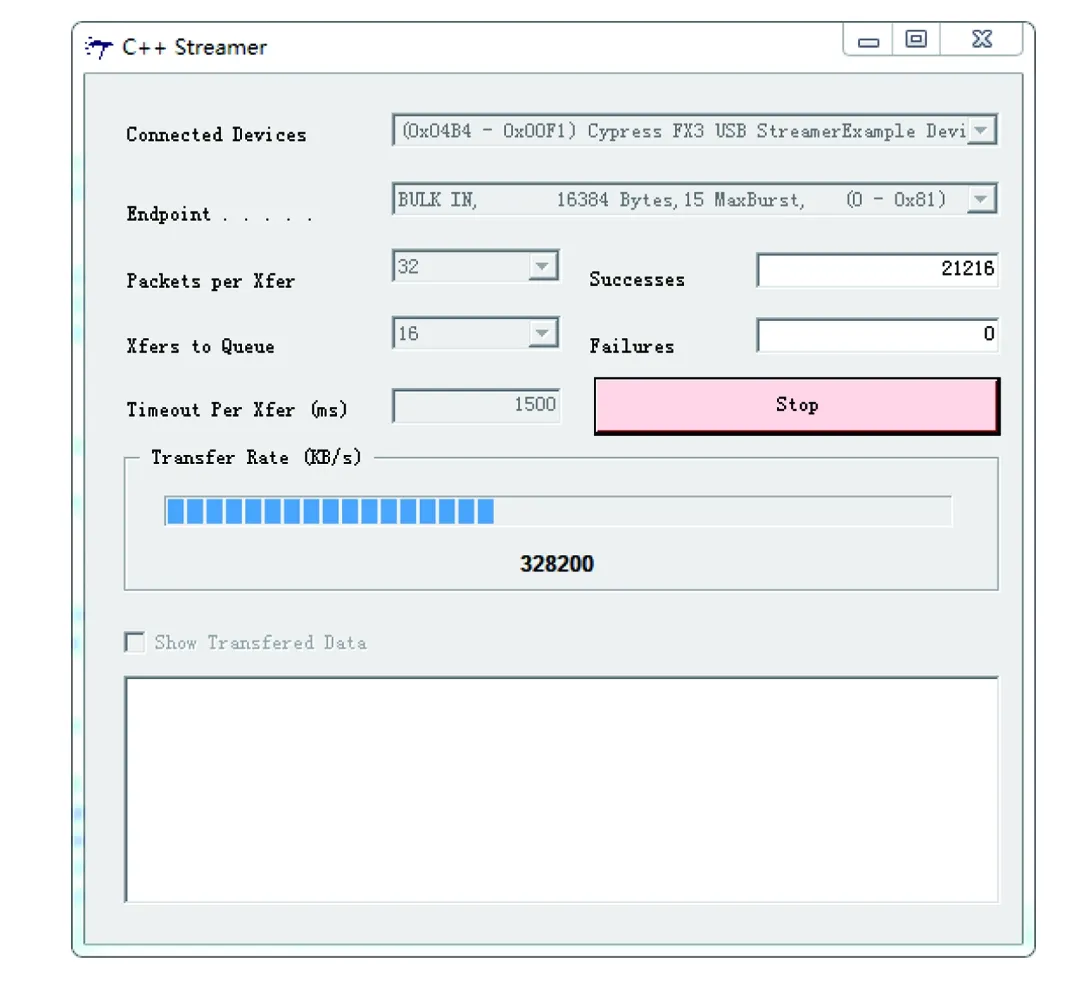

图13 图像传输带宽结果图Fig.13 Diagram of the bandwidth of image transfer

同时,采用专用的带宽测试工具来测试图像传输带宽,测试结果如图13所示,从图中可以看出,图像传输带宽大致为320 MB/s.

5 总结

系统针对高分辨率图像的采集,设计了一种高分辨率图像采集传输系统的FPGA设计。通过对图像传感器OV5640输出的高分辨率图像进行采集存储,并通过USB3.0接口将其上传至上位机进行显示。经过系统测试验证,本设计能够实现分辨率为2 592×1 944的图像的稳定采集,帧频达到14 f/s.同时,图像传输带宽达到320 MB/s,图像传输质量良好。系统设计正确,对于高分辨率图像的采集设计具有一定的意义。