视频图像数据采集的FPGA实现方案

2021-12-10雷妍

雷妍

(西安石油大学电子工程学院,西安 710065)

0 引言

随着电子科技的发展,视频监控技术已经广泛走入人们的生活,得到了各行各业的青睐[1]。视频图像采集的速度快慢和采集图像分辨率大小的问题,都会直接关系到工业的生产效率。常见的图像传感器分为CCD图像传感器和CMOS图像传感器。虽然CCD图像传感器在成像方面要优于CMOS传感器,但CCD传感器具价格昂贵、功耗大,不适合工业化大批量生产[2]。故CMOS图像传感器以其开发周期短、功耗小的特点成功进军工业、监控、航天等领域。传统的方法是对采集的视频图像进行采样处理,以牺牲图像的分辨率为代价来换取较高的控制速度。这样的方式显然不适合与分辨率要求高的场合。近年来,随着集成电路技术的发展,为现场可编程门阵列进入现代电子舞台开辟了新的路径[3]。FPGA不仅具有灵活、方便的可编程能力,而且因其并行处理特性非常适合于高速控制场合[4]。

本文将视频采集中的问题与FPGA自身的优势相结合,对图像传感器的工作原理进行分析,介绍了一种CMOS视频图像数据高效采集的FPGA实现方案。该设计方案选用Intel公司的Cyclone IV系列EP4CE10F17C8芯片,和Omni Vision公司的CMOS图像传感器OV7670,在Quartus II开发环境下采用硬件描述语言Verilog设计了OV7670摄像头驱动电路,完成了摄像投的配置以及数据采集[5]。

1 图像传感器工作时序分析

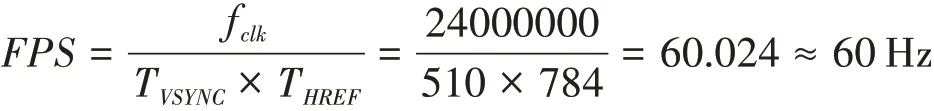

OV7670传感器内部集成了SCCB接口、图像阵列、时序发生器、A/D转换器、DSP处理器等电路。光源信号照射到图像阵列产生相应的电荷,传输到模拟信号处理器电路,再经A/D转换电路将模拟信号数字化,最后将数字信后传送至DSP处理器变为RGB信号输出。在OV7670的视频时序知,当VSYNC视频流的场同步信号有效,则表示一帧图像的结束;当HREF行同步信号有效时,在传感器的工作时钟驱动下输出图像数据[6]。一幅图像中每一行中有784个像素单位时间,共有510个行时间。而OV7670传感器的输出时钟为24 MHz,因此帧率为60 Hz。计算方法见公式(1)。由于本设计输出的视频数据格式为RGB565,每个像素需要输出两个数据,因此行时间为原来的2倍,最大帧率只能达到30 Hz[7]。

2 图像数据采集的FPGA实现

本设计采用自顶向下的设计思想,将焊缝图像数据采集设计划分为三个功能独立的子模块,分别为摄像头工作时钟产生模块、摄像头初始化模块以及摄像头数据捕获模块[8]。

2.1 OV7670摄像头工作时钟产生模块设计

该模块主要用于提供摄像头的工作时钟,以保证摄像头准确无误的采集图像数据。本设计在Quartus II自带的MegaWizard Plug-In Manager中选择I/O的ALTPLL,创建时钟模块,将50 MHz的晶振时钟分频为24MHz,用于驱动摄像头正常工作。

2.2 OV7670寄存器初始化模块设计

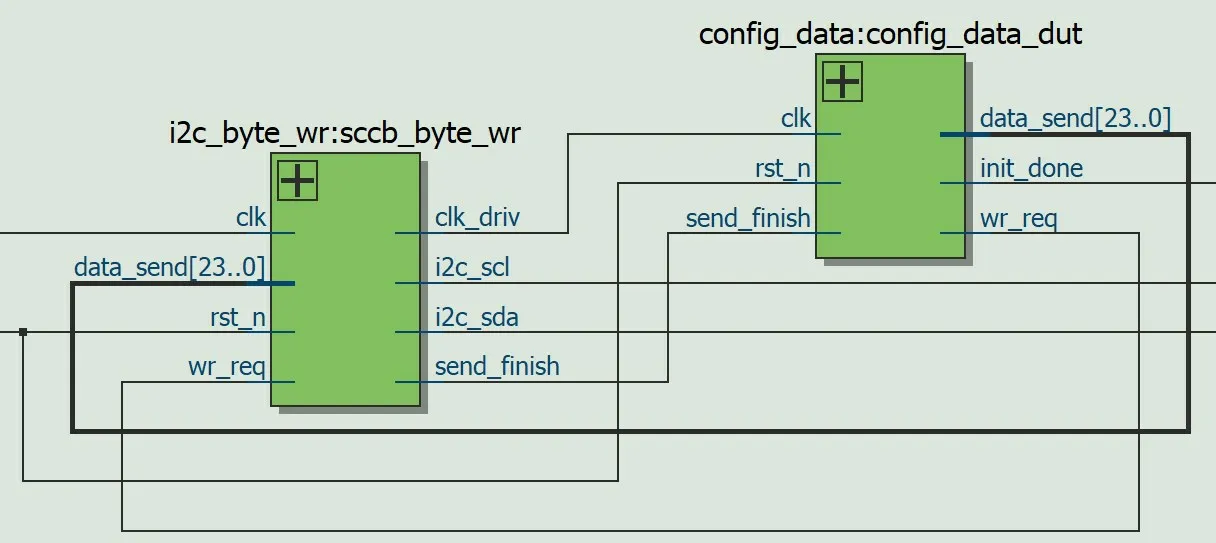

本模块主要负责摄像头的初始化工作。在本设计中,将该模块划分为两个子模块,分别为config_data子模块和i2c_byte_wr子模块。前者主要输出写请求信号wr_req,和待发送的数据data_send;后者主要完成摄像头内部寄存器配置的工作。图1为该模块的RTL视图,图中详细描述了两个子模块间信号的交互。

图1 OV7670寄存器初始化模块RTL视图

在初始上电3 ms后,当config_data子模块输出wr_req信号为高电平且待发送的数据未达到上限时,启动参数配置计数器进行计数。根据参数配置寄存器的计数值输出待发送的数据。当待发送数据达到上限时,拉高init_done信号,标志摄像头初始化已完成,可进行数据捕获。

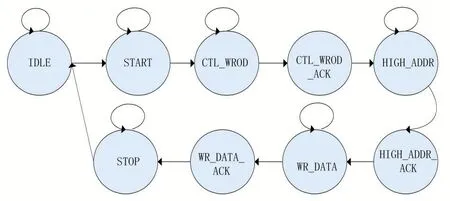

当i2c_byte_wr子模块检测到wr_req为高电平时,使用SCCB通信协议传输寄存器的参数。根据SCCB协议特点,该子模块采用状态机的思想,进行程序设计。图2为OV7670摄像头寄存器参数配置状态机示意图。

图2 OV7670摄像头内部寄存器参数配置状态机示意图

当系统复位结束后,该子模块的状态处于IDEL状态,在此状态检测cofig_data子模块输出的wr_req是否为高电平,如果该信号为低电平,状态不发生跳转,否则在i2c_scl时钟高电平期间状态跳转到START状态。在START状态,当i2c_scl为高电平期间,将i2c_sda信号从高电平变为低电平,标志着SCCB协议的起始位,同时状态跳转至CTL_WORD状态,发送OV7670的器件地址,经一个非应答位,状态跳转到HIGH_ADDR状态,传输摄像头内部寄存器的地址。同理状态跳转到HIGH_ADDR_ACK,经一个非应答位,状态跳转到WR_DATA状态,完成参数传输,等待一个时钟周期的非应答位,状态跳转到STOP状态,发送停止位,即在i2c_scl高电平期间将i2c_sda信号由低电平变为高电平。同时send_finish信号维持一个时钟周期的高电平,并且状态跳转到IDEL状态,等待下一个寄存器的配置。

2.3 视频数据采集模块

考虑到图像数据采集的稳定因素,该模块丢弃前十帧图像数据。从第十一帧图像开始,对摄像头输出的8位位宽数据进行数据格式的转换。由于本次设计在摄像头寄存器配置时,选择RGB565数据格式进行输出,所以需要两个时钟周期进行8位数据到16位RGB565数据格式的转换。由时序可知,当行同步时序开始有效时,首先输出RGB565数据格式的高八位,其次输出RGB565的低8位。根据这一时序特性,本模块在程序设计时,设置了数据转换使能信号。当行同步信号有效时,该使能信号没经过一个时钟周期进行一次取反操作。当其为低电平时,将摄像头输出的数据传递给RGB565数据的高八位,当其为低电平时,将数据赋值给RGB565的低8位,最终可在两个摄像头工作时钟周期内输出一个完整的RGB565图像数据格式。考虑到视频流的行同步信号于输出的数据对其的情况,该模块将行同步时序打拍操作,目的在于在摄像头的工作时中下,将行同步信号与输出的RGB565数据进行同步。此外,该模块在进行两个八位数据拼接时候,为表示有效的RGB565正常输出,该模块在数据拼接完成后设有数据有效标志信号。

3 实验结果及分析

为保证本设计的可行性,对本设计进行两种验证方式,分别为基于Modelsim的仿真验证和基于SignalTap II的板级验证,并对两者的实验结果进行分析。

3.1 基于Model si m环境下的仿真结果及分析

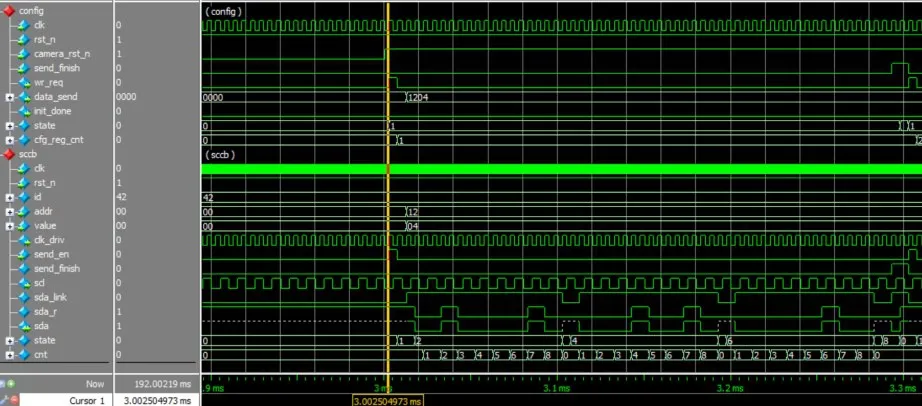

图3为OV7670内部第一个寄存器配置的仿真结果。由仿真结果可知,上电3ms后,cofig_data子模块拉高写请求信号data_send,并发送写入OV7670内部寄存器的参数0X1204,0X12表示配置寄存器的地址,0X04表示寄存器内部的参数。i2c_byte_wr模块检测到data_send(send_en)信号后,状态跳转到1状态产生起始位。随后状态跳转到2状态发送摄像头器件地址0X42,发送完成后跳转到3,经过一个非应答位后,状态直接跳转到4发送寄存器地址0X12,随后以同样的方式发送寄存器内的参数0X04,最后状态跳转到8状态发送停止位,即证明地址为0X12的寄存器配置完成,继续检测data_send信号,进行下一个寄存器的配置。

图3 OV7670内部第一个寄存器配置的仿真结果

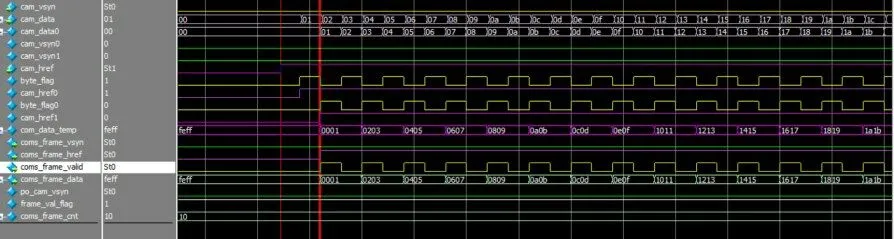

图4 为视频采集模块的仿真结果图。仿真图中的byte_flag为8位数据转16位数据的标志信号,从图中可以看出,当图像传感器的行同步信号cam_href有效时,byte_flag信号每经过一个时钟周期取反一次。当byte_flag为高电平时,可发现图像传感器首先输出的8位数据传送至com_data_temp的高8位,即16位的RGB565数据的高八位,其次输出的数据传送给com_data_temp的低8位。故经图像传感器的数据采集模块电路后。可将两个8位的数据转化为1个16位的数据,如图中图像传感器输出的数据0X00和0X01被转换为0X0001,即图中的coms_frame_data寄存器中存储的数据。coms_frame_valid表示RGB565数据有效标志。为了满足视频流时序中行同步信号与图像数据输出对其的时序要求,本设计对行同步信号cam_href进行打3拍处理,即处理之后的coms_frame_valid信号。

图4 视频采集模块仿真

3.2 基于Si gnal Tap II的板级验证及结果分析

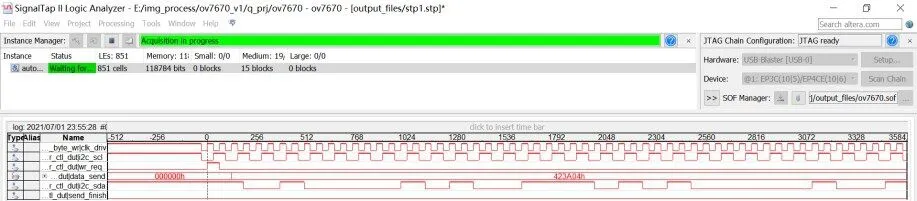

SignalTap II,是一款FPGA片上Debug工具软件,用于捕获设计中硬件与软件之间的信号传递。图5为OV7670硬件配置真实数据变化,从图中i2c_sda由高电平变为低电平看起,i2c_sda数据信号线上传输的数据为0100_0010,十六进制的42,即FPGA选中OV7670摄像头为从机,经一个i2c_sda高电平后,i2c_sda上的数据信号为0011_1010,十六进制的3A,实现OV7670内部地址为3A的寄存器寻址。同理经过一个i2c_sda的高电平后,其数据变化为0000_0100,十六进制的04,实现的功能是将地址为3A的寄存器数据配置为0X04。

图5 OV7670硬件寄存器配置

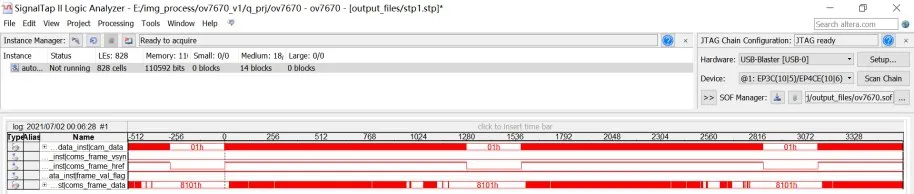

图6 为OV7670视频数据捕获模块的验证结果,从图6可知该模块在com_frame_href为高电平时,输出有效数据,符合RGB565在行同步信号有效时输出有效的图像数据的时序要求。

图6 OV7670视频数据捕获模块的整体验证结果

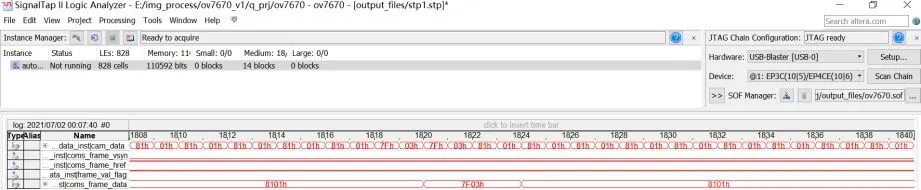

图7 为RGB565数据格式验证结果。该模块实现了当coms_frame_href为高电平时,将OV7670输出的两个八位数据转化为一个16位的RGB565数据格式。

图7 RGB565数据格式验证结果

4 结语

本文针对提高视频控制的实时性的传统方式,以图像分辨率为代价换取控制实时性这一问题,提出了一种CMOS视频图像数据高效采集的FPGA实现方案。该方案利用FPGA的并行处理能力,提高了视频控制的实时性能。通过上述仿真可证明,该方案逻辑的正确性。为保证该方案的硬件实现,本次实验在Intel公司的Cyclone IV系列EP4CE10F17C8 FPGA硬件开发平台上进行验证,并用在线逻辑分析仪对实验结果进行采集和分析。结果证明,该方案具有硬件可实现性。