基于FPGA的ADC128S022数据采集系统

2021-11-19西华师范大学物理与空间科学学院雷小英肖顺文吴静瑜陈韵文郑瑞

西华师范大学物理与空间科学学院 雷小英 肖顺文 吴静瑜 陈韵文 郑瑞

本文设计了基于FPGA的8通道12bit分辨率的数据采集系统,利用FPGA控制ADC128S022芯片进行数据采集和模数转换,将采样到的数据与理论值对比,经分析验证,电压值在误差范围内。该系统设计精简,可广泛应用于实时数据采集与转换。

0 引言

数据采集系统是将模拟信号转换为数字信号,利用计算机对信号进行处理[1]。ADC是数据采集中最重要的部分之一,高精度、高速度的ADC已广泛应用于导航、手持终端、无人驾驶等领域[2]。现场可编程门阵列的出现,令系统设计拥有高灵活性;与传统单片机作比,FPGA具有数据处理能力强、开发设计周期短等优势。本文设计了基于FPGA的数据采集系统,选用具有8通道,12位分辨率的ADC128S022芯片,转换速率可达200ksps,利用FPGA对ADC128S022进行控制,实现数据采集,不仅可以将数据存储在RAM中,也能将数据进行处理,最后在PC机显示。

1 ADC128S022数据采集系统的工作原理和时序分析

1.1 ADC128S022型数据采集系统工作原理

ADC128S022中VA/4096是1bit的电压值,当模拟输入电压小于它1bit所含电压值时,输出数据是0000_0000_0000b,当输入电压比模拟电源VA减去1bit所含电压值的1.5倍大或相等时,输出数据是1111_1111_1111b。本设计电源采用独立的模拟供电及数字供电,数值为3.3V,模拟电源和数字电源间用串联磁珠来稳压和滤波[3]。数据采集系统设计框图如图1所示。模拟信号输入后,电源模块为各部分供电,在采样时钟下,FPGA对ADC128S022进行控制实现数据采集,通过四线制SPI总线与处理器进行通信[4]。FPGA对数据进行处理后,根据需求将部分数据存储到RAM中,数据也可在PC端显示。

图1 数据采集系统内部设计框图Fig.1 Internal design block diagram of data acquisition system

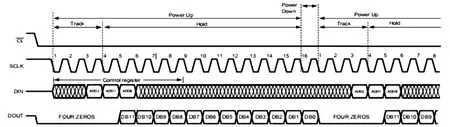

1.2 ADC128S022型接口时序分析

按串行外设接口的时序逻辑来构造控制电路。设备工作频率是0.8~3.2MHz,将1.92MHz(周期为520ns)设置为工作频率。为适配不同频率需求,设计一个可调计数器,令采样时钟为系统时钟的13分频3.84MHz,即两倍于SCLK的SCLK2X时钟信号。时序图如图2所示,一个串行帧在 下降沿的时候开始转换,在其上升沿结束[5]。一帧中有16个上升沿。ADC在前3个循环处于采样,后13个循环处于保持状态,最后转换完成输出数据。DOUT是转换结构输出脚,在SCLK的下降沿时输出。1至4为前导零,5至16是输出结果。若处于持续测量模式,ADC会在N×6个SCLK的上升沿自动进入采样模式,在N×16+4个下降沿进入保持或转换模式。DIN有8个控制寄存器,其中ADD[2∶0]是数据输入时的通道选择,输入通道从IN0~IN7中选择。根据线性序列机的设计思想,能够验证出各个信号不同情况下计数器对应的值。

图2 ADC128S022 SPI接口时序图Fig.2 SPI interface timing diagram of ADC128S022

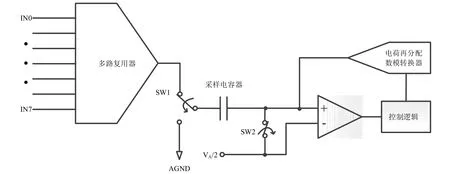

2 ADC128S022芯片的内部结构原理

设计选用8通道及12位分辨率的逐次逼近型的低功耗芯片—ADC128S022。模/数转换使用逐渐逼近的方式,转换速度虽会低于并联比较型ADC,但高于双积分型,是中速ADC。且3.3V/5V的输入电压均可,和主控制器通过SPI的方式实现交互通信。其中片选信号CS_N,ADC的时钟信号SCLK以及地址信号DIN都是其驱动信号。ADC128S022内部结构框图如图3所示,当开关1连接多路复用器和采样电容器,开关2将平衡比较器输入的时候,在 下降沿的前3个周期,ADC128S022处于采样状态。当开关1将采样电容与模拟地连接,开关2断开,保持采样电压时。控制逻辑会引导电荷再分配数模转换器添加或减少固定数量的电荷,直至比较器平衡。即在 低电平的后13个周期,ADC128 S022处于保持状态。

图3 ADC128S022内部结构功能框图Fig.3 ADC128S022 interface logic module diagram

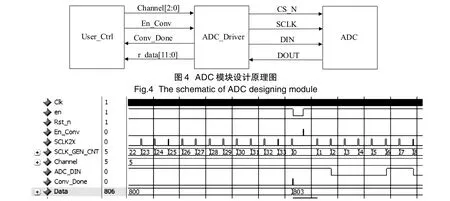

3 FPGA控制的ADC模块设计

本设计系统中FPGA控制的ADC模块的设计原理图如图4所示,该设计利用FPGA控制ADC128S022开始数据采样,并处理采样数据,随后将转换后的数据输出[6]。ADC_Driver产生ADC位宽为1的CS_N、SCLK、DIN以及DOUT驱动信号,且接受ADC的转换数据DOUT。User_Ctrl产生3位地址信号Channel让驱动选择八个输入通道中的一个。En_Conv是外部使能信号,使能单次转换,且此信号单周期有效,高脉冲使能转换一次;为防止转换中Channel的值改变影响数据,当使能转换时,寄存当前状态通道选择的Channel值。DIN把3位地址信号转化为串行的1位DIN。Conv_Done将所有数据输出至驱动,驱动接受并产生转换完成信号;若ADC128S022芯片运行良好,完成一次转换,就会将内部寄存器r_date的数据输出至输出端Date。将ADC采样到的多组数据与理论电压值对比,经验证,误差合理,ADC模块正确。

4 仿真结果及分析

在Quartus II 13.0中与Modelsim进行联合波形仿真,结果如图5所示。当控制器的工作时钟频率为50MHz时,控制器先低电平复位,随后拉高。在En_Conv高脉冲使能时进行一次转换,若有效,便将使能信号en置于1,每次使能转换之后,对SCLK2X时钟计数[7]。当SCLK2X计数器值为33d且为高,就输出一个高脉冲信号。代表一次转换结束。ADC_DIN是FPGA控制采样时的通道选择,由图5可知,此处每个循环输出均为101b,即通道5。在每个ADC_SCLK上升沿,ADC_ DOUT都会输出一位数据。由图5知,第一次转换中,ADC_ DOUT先输出四个前导0,再输出1000_0000_0000b,即第一个数据800h。在一次转换完成后,输出并行数据Date。连续进行三次转换,输出数据分别为800h、803h、806h。随后进行板级仿真,在Quartus II中新建顶层文件ADC_test,将ADC128S022、TLV5618模块例化,生成两个ISSP文件形成系统,再分配其引脚进行全编译,下载程序,打开ISSP抓取ADC电压。发现电压值均在误差范围内。符合设计需求。

图5 总体设计仿真波形图Fig.5 Simulation waveform of the overall design

5 结语

本文用Verilog HDL完成了ADC128S022的数据采集系统设计,不但进行了功能仿真设计,而且进行了ADC和DAC的联合板级调试。考察整个系统的性能,结果表明,该设计符合预想。本设计采样精度高,采样速度较快,能运用在航空、军事、医疗等领域[8],具有较大的实用价值。

引用

[1] 徐智轩.一种16位200Msps的ADC数据采集系统设计[D].合肥:中国科学技术大学,2019.

[2] 杨兴文,雍珊珊,王新安,等.AETA数据采集系统的设计与实现[J].北京大学学报(自然科学版),2020,56(4):600-606.

[3] 李海涛,李斌康,阮林波,等.应用于高速数据采集系统的超低抖动时钟电路[J].数据采集与处理,2020(6):1192-1199.

[4] 范宋杰.多路数据采集系统的FPGA方案实现[J].电子世界,2021(6):170-171.

[5] 赵晨,周义明.基于FPGA的模数转换芯片AD7705/AD7706控制电路设计[J].北京石油化工学院学报,2019(4):54-58.

[6] 张月,陶林伟.基于FPGA与STM32的多通道数据采集系统[J].西北工业大学学报,2020(2):351-358.

[7] 丁宁,常玉春,赵健博,等.基于USB 3.0的高速CMOS图像传感器数据采集系统[J].吉林大学学报(工学版),2018(4):1298-1304.

[8] 王睿.Lidar控制与数据采集系统研究[D].合肥:中国科学技术大学,2020.