基于M80C186与M80C187的联合验证系统设计与分析

2021-11-02吕东明

张 彬,吕东明

(中国电子科技集团公司第四十七研究所,沈阳110000)

1 引言

Intel公司的16位高精度微处理器M80C186将15~20个最常见的微处理器系统组件集成在一个芯片上,它具有很多8086系列处理器的新特性,例如DRAM刷新控制单元、直接数字接口以及省电模式等。此外,M80C186在原有的8086指令集上增加了10种新的指令,可以在兼容模式和增强模式下工作。在增强模式下增加了节能控制、DRAM刷新、协处理器接口这三个新功能[1]。M80C186以其丰富的功能及强大的运算能力在通信系统、信号处理系统中有着广泛的应用。

M80C186具有16根数据线和20根地址线,可寻址空间为1MB,I/O地址空间为64kB。它的硬件仅支持对整数的算术运算,不能进行高精度的数值运算,而高性能数学协处理器M80C187的诞生为解决该问题提供了新的可能[2]。M80C187与M80C186的目标代码是兼容的,能够并行工作,协同分工。故此可基于各自特点,将两者配合起来使用,设计出一套改进的联合验证系统。

2 总体设计方案

微处理器M80C186的中央处理单元(CPU)主要包含总线接口单元和执行单元。总线接口单元包括6字节的队列和16位的段寄存器。执行单元包含16位算数逻辑单元和16位通用寄存器组,以及用作总体控制的程序控制器[3]。片内电路还包含时钟发生器、可编程定时器、可编程中断控制器、可编程DMA控制器、片选单元等。

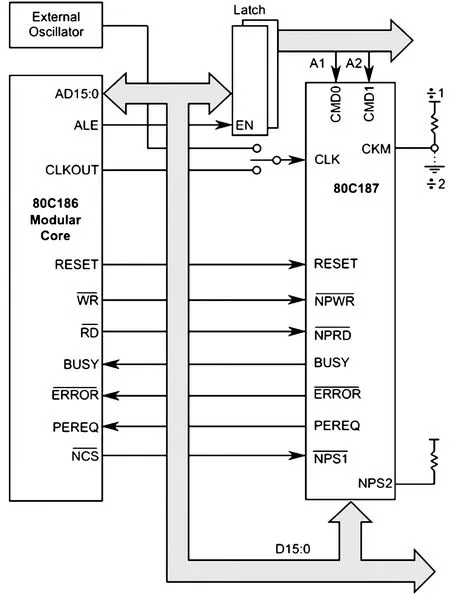

M80C186没有存储单元和一些必要的外设,不能构成一个完整的系统,因此需要用户自己设计电路来搭建系统。在所设计的联合验证系统中,除了占主体地位的16位高精度微处理器M80C186与高性能数学协处理器M80C187之外,还包括以下几个重要组成部分:外部时钟源、电源电路、串口通信电路、地址锁存器、缓冲器(数据收发器)、存储器(包含数据存储器和程序存储器)等。系统的总体设计框图如图1所示。

图1 M80C186与M80C187联合验证系统总体框图

作为控制系统的核心,微处理器M80C186与协处理器M80C187通过BUSY、ERROR、PEREQ、NCS等端口直接连接,以并行协同的方式进行工作。微处理器和协处理器供电电源均为5V直流电。时钟发生器为M80C186提供系统时钟。M80C186的数据线和地址线是分时复用的,因此需要地址锁存器(LATCH)将地址信息保存起来,为外设提供地址信息[4]。当系统总线所挂外设过多时,需要利用缓冲器(BUFFER)来增加总线的驱动能力。M80C186内部也没有存储器,因此需要外接程序存储器(E2PROM)和数据存储器(RAM)。增加串口(Serial Port)的目的是为了将微处理器与PC建立通信,进而把系统的运算结果输出到PC上。

3 电路设计

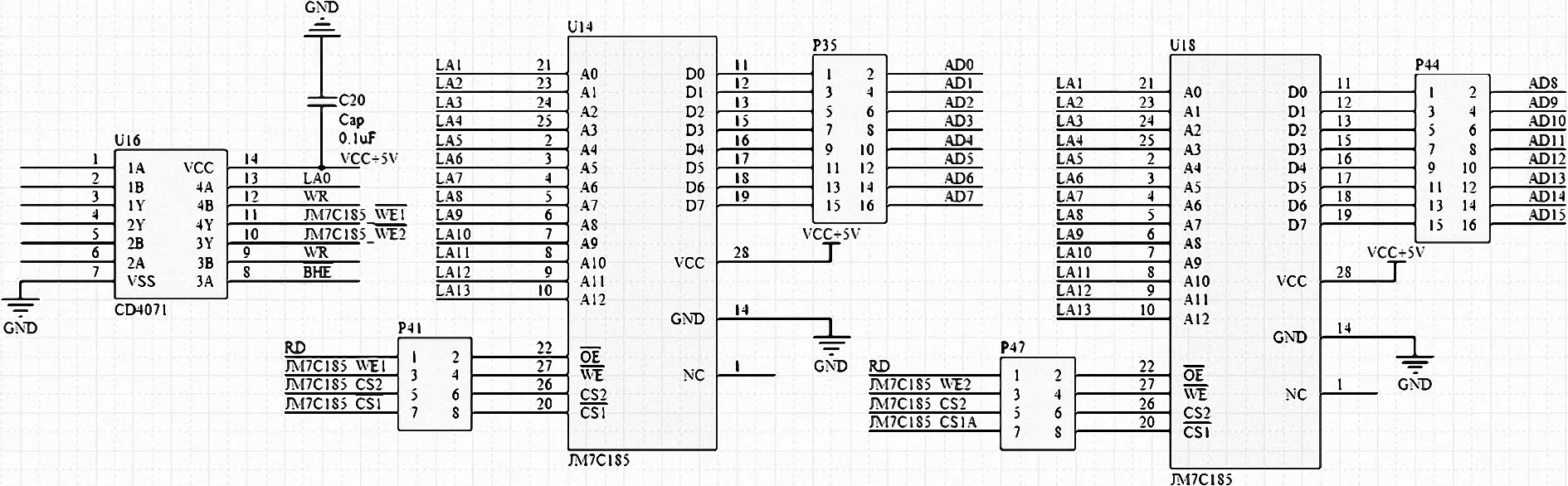

3.1 协同电路

此联合验证系统设计中最重要的是M80C186和M80C187的协同电路设计。在该协同电路中,主处理器M80C186处于最大工作模式,一切控制指令均由M80C186发出,M80C187作为协处理器进行高精度的数值浮点运算[5]。

高性能数学协处理器M80C187的指令集增加了70多种助记符用来进行复杂的数值计算。它通过浮点运算和BCD数据扩展了8086架构,且两者的外围接口电路和指令集完全兼容,这为硬件电路设计和软件编写都带来极大的便利条件。M80C187的接入,可大幅提高系统的数值运算速度与运算能力。协同电路的设计架构如图2所示。

图2 M80C186和M80C187的协同电路架构

M80C186与M80C187的部分控制接口通过通过BUSY、ERROR、PEREQ、NCS四个接口进行信息交互,这四个接口的信号分别与TEST、MCS1、MCS0、MCS3这四个信号进行复用。当M80C186处于非复位状态时,M80C187会自动将M80C186置于增强模式,并自动配置引脚功能,此时M80C186处于编程就绪状态[6]。

AD0~AD15是数据与地址的复用总线,在总线周期的T1状态,用作总线的低16位地址总线;在总线的T2、T3、Tw时,用作数据总线。

AD16~AD19是状态与地址的复用总线,在总线周期的T1状态,用作高4位地址线;在总线的T2、T3、Tw时,用作状态信号线。通过引脚的分时复用,可以在不同的时刻传递不同的信息,进而减少引脚数量又不缩减芯片的功能。

在此协同电路中,M80C186和系统总线相连,当需要M80C187进行高精度数据运算时,M80C186的处理器扩展请求引脚(PEREQ)发出总线请求进行取指令,从CPU获取总线控制权限,由M80C187从数据总线获取数据并准备操作数,忙信号(BUSY)有效表示M80C187的数值执行单元正在执行数值运算指令。M80C186的读、写信号直接与M80C187的读、写引脚相连。该设计减少了总线上挂载的外设,也降低了系统的复杂度。

3.2 锁存电路与缓冲电路

M80C186的AD0~AD15是数据与地址的复用总线,AD16~AD19是状态与地址的复用总线。它们需要地址锁存器将地址信息保留起来,为存储器等外设提供地址信息。此处选用的锁存器是三态输出的8路D类锁存器74ACT573T芯片。

采用三片74ACT573T芯片对地址信息AD0~AD19进行锁存,设计出的锁存电路如图3所示。将微处理器M80C186的地址锁存信号ALE连接到锁存器的LE引脚。锁存器的输出使能引脚OE直接接地。第一片74ACT573T对地址信息AD0~AD7进行锁存;第二片74ACT573T对地址信息AD8~AD15进行锁存,第三片74ACT573T对地址信息AD16~AD19进行锁存。

图3 三片74ACT573T芯片构成锁存电路

当系统总线连接外设较多时,就需要为系统增加缓冲器电路,以便增加总线的驱动能力。此处设计由两片74LS245芯片构成缓冲电路,如图4所示。微处理器M80C186的数据总线允许信号DEN接到74LS245芯片的使能引脚OE上。M80C186的数据收发信号DT/R接到74LS245芯片的DIR引脚上。这样通过两片74LS245芯片组成的数据收发电路,对M80C186的数据传输起到缓冲的作用,增加了总线的驱动能力。

图4 两片74LS245芯片构成缓冲电路

3.3 程序存储电路与数据存储电路

在所设计的联合验证系统中,存储器以字节为单位进行地址分配。容量为1MB的存储空间被分成了奇体单元和偶体单元。奇体单元的地址是奇数,偶体单元的地址为偶数,它们各自的存储空间大小即为512kB。但在电路的逻辑上,M80C186的存储单元还是按照地址顺序进行排列。

在此设计出基于AT28C256(E2PROM)芯片的程序存储电路,用来读取程序代码并加载运行。电路选用两片32k×8bit的AT28C256芯片,一片作为奇体存储单元,另一片作为偶体存储单元,如图5所示。在电路中,M80C186的片选信号UCS连接AT28C256芯片的片选引脚CE。M80C186的读取信号RD连接AT28C256芯片的使能引脚OE。M80C186的数据总线的高8位与奇体单元的数据线相连,低8位与偶体单元的数据线相连。

图5 两片AT28C256芯片构成程序存储电路

数据存储电路则是基于JM7C185(RAM)芯片进行设计,用来保存临时数据。该部分电路采用两片8kB×8bit的JM7C185芯片与一片四通道或门逻辑器件CD4071,一共可以存储8kB×16bit的数据,所设计电路如图6所示。M80C186的片选信号LCS连接JM7C185芯片的片选引脚CS。对于低字节RAM,M80C186的LA0和RD作或逻辑运算,输出接到第一片JM7C185的使能引脚OE。M80C186的LA0和WR作或逻辑运算,输出接到第一片JM7C185的写引脚WE。同理,对于高字节RAM,M80C186的LA0和RD作或逻辑运算,输出接到第二片JM7C185的使能引脚OE,M80C186的LA0和WR作或逻辑运算,输出接到第二片JM7C185的写引脚WE。

图6 两片JM7C185芯片构成的数据存储电路

3.4 串口通信电路的设计

M80C186不具有串口功能,因此要想把运算结果输出到PC上,需要设计串口电路,让M80C186和M80C187联合验证系统与PC建立通信,为此所设计的基于8251芯片的串口通信电路如图7所示。

图7 基于8251的串口通信电路

在该电路中,M80C186的片选信号PCS接至8251的片选引脚CS;地址信号LA0接至8251的寻址引脚CD;读、写信号分别接至8251的读、写引脚。8251芯片采用查询的方式与M80C186进行信息交换。当8251的状态寄存器D0为信号1时,M80C186可以向8251数据端口写入数据,完成串行数据的发送。当8251的状态寄存器D1为1信号时,M80C186可以向8251数据端口读出数据,完成一帧数据的接收。

4 分析与验证

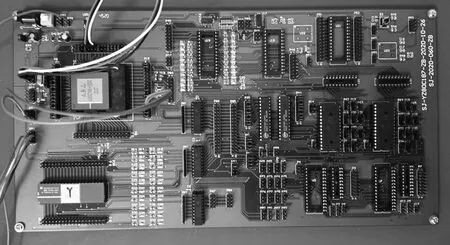

基于上述设计方案,依据原理设计图,对实际电路进行布局布线、PCB制作,最后搭建出此款基于微处理器M80C186和协处理器M80C187的联合验证电路,实物图如图8所示。M80C187协处理器主要包含三个单元:控制单元、数据接口单元和浮点运算单元。控制单元通过数据接口单元与微处理器M80C186进行通信[7]。M80C187的指令分为六个功能组:数据传输、计算、比较、超越、常数、控制。M80C187的浮点运算单元在控制单元和数据接口单元的监控下进行取指、执行。为验证该系统的双精度浮点数运算能力,首先对E2PROM进行编程使系统进行常数计算:3+5。然后通过逻辑分析仪进行多通道信号采集、逻辑分析与时序判定,得到系统的运算结果(双精度浮点数)并与标准值进行对比,进而验证系统的可操作性与准确性。逻辑分析仪采集的信号如图9所示。

图8 所设计联合验证电路实物图

图9 逻辑分析仪采集信号

利用逻辑分析仪采集以下信号:总线上的数据、PEREQ、BUSY、ERROR、NPRD、NPWR、CMD0、CMD1、NPS1、RESET、CLK。其中,CLK为系统时钟;PEREQ信号有效表示M80C187从M80C186获取局部总线控制权限;BUSY信号有效表示M80C187的浮点运算单元正在执行指令。

在系统发生错误时,ERROR信号变为有效,BUSY信号变为无效。M80C187的接口电路状态始终与M80C186保持一致。为了便于指令的区分,M80C187的指令都是以“11011”开始的。M80C187内部包含了临时寄存器、移位寄存器等。当系统执行逃逸指令(ESC)时,无需数值执行部件参加运算,由控制部件单独完成运算[8]。

通过分析图9的信号时序可知,系统运算的结果为双精度浮点数“41000000”,该数表示十进制数“8”,因此系统计算正确。同配置下的后续实验也进一步证明了该联合测试系统可以计算三角函数、指数和对数等高精度浮点数数值运算。

5 结束语

M80C186和M80C187的联合验证平台的设计不仅可以用于验证M80C187数字协处理器的功能,还可以用于验证M80C186的一些其他重要功能,为设计M80C187协处理器提供有力的参考依据。验证系统的整体电路的设计可以为以后基于80X86、80X87、8096、8XC196等一系列16位MCU应用验证的硬件设计提供参考依据。