基于单片机的多功能抢答器的设计与实现

2021-11-01郑辰瑛

郑辰瑛

【摘 要】随着竞赛活动的日益丰富,人们对智能抢答器的需求不断增加。为更深入地研究抢答器并对其功能进行改善,论文采用89C51单片机及外围接口设计了一个八路抢答器,用按键模拟选手抢答,并结合单片机定时器/计数器的功能实现抢答计时。论文介绍了抢答器的总设计方案,并对其工作原理和功能进行了探讨。该多功能抢答控制系统能够实现抢答器参数修改、抢答倒计时、抢答结果显示、抢答报警指示等功能。

【Abstract】With the continuous enrichment of competition activities, people's demand for smart answering device continues to increase. In order to study the answering device more deeply and improve its function, this paper uses 89C51 single chip microcomputer and peripheral interface to design an eight-way answering device, using buttons to simulate the player's answering, and combining the timer/counter function of the single chip microcomputer to realize the answering timing. This paper introduces the general design scheme of the answering device, and discusses its working principle and function. The multi-function answering control system can realize the functions of answering device parameter modification, answering countdown, answering result display, answering alarm indication and so on.

【关键词】抢答器;多功能;51单片机;功能模块

【Keywords】answering device; multi-function; 51 single chip microcomputer; functional module

【中图分类号】TP368.1 【文献标志码】A 【文章編号】1673-1069(2021)11-0191-03

1 引言

抢答器可以提高比赛的质量和效率,并且保障比赛的公平开展。随着人们对抢答器功能需求的增加,需要对其功能进行完善,使抢答器向集成化、智能化方向发展,即采用一种基于单片机的智能抢答器设计方法,这样不仅能使设计与生产制造规模化,也能使抢答器功能多元化,从而得到广泛应用。抢答器是被广泛用于各种竞赛活动的通用工具,但使用抢答器的频率相对较低,所以长期存放会使抢答器内部电子器件损坏。为避免采购带来的成本损失,本文设计了基于单片机的多功能抢答器。

2 抢答器系统的总体设计方案

本文简要介绍了一种多功能数字抢答器显示电路的基本结构及其基本组成、设计和使用功能,该数字抢答器电路除了应当具有基本的数字抢答显示功能外,还应当同时具有快速计时和自动报警2种功能。主持人可通过抢答时间的预置自动开关来设置每次抢答的持续时间。随即系统将自动进入倒计时模式,若在规定的时间内有人进行本次抢答,则计时器将自动停止,自动进入答题模式。若在规定的时间内没有人进行抢答,则系统的蜂鸣器将会自动发出警报,提示本次抢答失败,即时间超出本次抢答的规定时间则报警表示本次抢答失败。

本设计将硬件功能代入现实应用场景,即有八组抢答选手以及一位裁判员。裁判员按下倒计时的清零复位按键,使得单片机负责倒计时部分的功能清零复位,随即倒计时部分程序启动,通过一个数码管提示倒计时,提醒参赛者进行抢答。倒计时结束后,抢答部分的程序就会开始执行,选手在倒计时结束前进行抢答才被视为有效。选手抢答瞬间其信息将被锁存,抢答成功后由蜂鸣器警报提醒,同时,数码管上会显示当前抢答成功的小组组号。如果小组在非法时间内按键抢答,蜂鸣器也会发出警报。下一轮的开始由裁判员控制,循环往复。

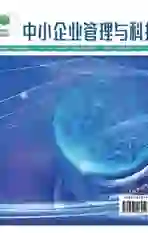

主程序工作流程如图1所示。

3 51单片机的功能

51单片机是对兼容英特尔8051指令系统的单片机的统称。51单片机的指令系统、内部结构相对简单,广泛应用于家用电器、汽车、工业测控、通信设备。89C51是一种具有4kB闪烁可编程、可擦除只读存储器的低电压、高性能CMOS8位微处理器,俗称单片机。单片机的可擦永久存储器可擦写1000次。该器件采用ATMEL高密度非易失性存储器技术制造,与行业标准MCS-51指令集和输出引脚兼容。由于多功能8位CPU和闪存结合在一个芯片中,89C51 ATMEL微控制器是一个高效的微控制器,而89C2051是一个简化版本。单片机为许多嵌入式控制系统提供了灵活且廉价的解决方案。其结构如下:

①8位CPU;②片内振荡器和时钟电路;③32根I/O线;④外部存贮器寻址范围ROM、RAM64K;⑤2个16位的定时器/计数器;⑥5个中断源,2个中断优先级;⑦全双工串行口;⑧布尔处理器。

4 抢答器功能模块设计及实现

本文中的多功能抢答系统以AT89C51单片机作为控制核心,其基本工作原理为在抢答过程中有多个信号同时或不同时送入主电路时,内部响应者寄存器工作并识别和记录响应第一个请求的玩家的数量。同时,内部定时器开始运行,记录相应的时间并产生超时信号。在答录机、显示电路、语音电路等整个工作流程中,还要根据现场的实际情况输出相应的信号给外部电路。其控制系统主要组成包括:复位清零模块、倒计时模块、选手抢答锁存模块、数码显示模块、抢答结束报警模块。

4.1 复位清零模块

复位清零端的主要功能是在人为按下按键后,单片机内部锁存信息清零,与抢答有关程序复位,准备进行下一轮抢答,并使单片机内部倒计时功能相关程序执行,正式开启下一轮抢答。

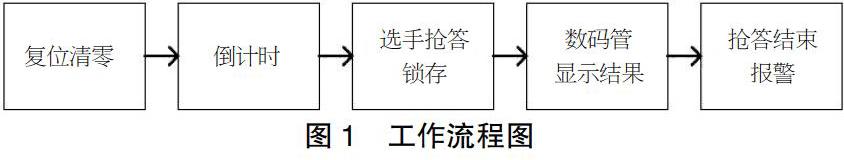

实现方法:外部中断和内部中断并存。硬件复位端只要保持4个机器周期就可以复位。硬复位后,寄存器和内存值被恢复到原始值。本设计使用机械弹性开关来实现复位清零功能,当机械触点连接状态转换时,由于其弹性作用,在转换瞬间会产生抖动。为避免该现象,就需要进行按键消抖。按键的抖动对于人类来说是感觉不到的,但对单片机来说,则是一个很“漫长”的过程,因为单片机处理的速度在“微秒”级,而按键抖动的时间至少在“毫秒”级。如果单片机在抖动期间发生误判,即按键按下或断开将被误认为是进行了多次操作,从而引起整个程序的错误(见图2)。所以,为确保单片机对一次按键动作只作一次响应,就必须考虑如何消除按键抖动的影响。

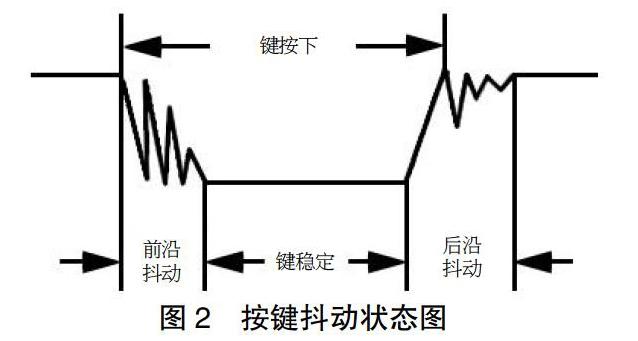

进行按键消抖的关键即提取一段稳定的电平状态,滤除电平稳定前后的抖动。当按键次数较少时可使用硬件方法对按键消抖。硬件消抖的一种典型做法是:使用R-S触发器进行双稳态消抖或使用RC积分电路进行滤波消抖。由于复位清零端单独独立于选手按键端,且为使布线更方便,可以选择应用RC积分电路进行滤波消抖。根据RC积分电路积分时长估算得出能消除机械抖动的电阻与电容值。图3为硬件电容消抖初步电路图,KeyIn1接入单片机9号引脚RESET端,用来实现复位清零功能。

4.2 倒计时模块

倒计时模块的主要功能为在复位清零按键被按下后自动进入10s倒计时,准确固定抢答开始时间,同时可以进行修改抢答时间。有小组抢到后直接进入30s倒計时,准确固定回答开始时间,同时也可以修改回答时间。同时,本实验电路的倒计时最后5s,程序会让蜂鸣器发出响声作为倒计时将要结束的提示。

实现方法:本电路使用计数器的计时中断法实现倒计时功能。

为提高系统效率,AT89C51单片机设置了中断系统。在CPU与外设交换信息时,存在一个快速的CPU与慢速的外设之间的矛盾。为解决这个问题,发展了中断的概念。CPU在处理特定事务时,如果发生外部或内部紧急情况,CPU必须暂停处理以应对紧急情况。处理完成后,返回原中断位置,恢复原中断操作,这个过程被称为中断。AT89C51有3个片内定时器/计数器溢出中断TF0-TF2,/INT0和/INT1外部中断,1个TI或RI片内串行口中断。

该系统的晶振频率为12MHz,每个计时脉冲为1μs,设定中断每次移除时间50ms,循环20次即1s。晶振主要用于为系统提供基本的时钟信号。为使整个系统各部分保持时钟同步,经常在一个系统内使用同一个晶振。晶体有一个很重要的特性即机电效应,如果给它通电,它就会产生机械振荡,反之,如果给它机械力,它又会产生电。即晶振可以将机械能和电能相互转化,在单频共振的状态下得到稳定振荡。由于抢答器电路设计较简单,所以可以选择较为简单的无源晶振。无源晶体振荡器是一种晶体,它本身不能振荡,并与其他IC的内部振荡电路一起工作。本电路应用内部晶振,选择振荡频率为12MHz石英晶体。

4.3 选手抢答锁存模块

抢答锁存模块的主要功能为将选手抢答结果准确及时保存,为小组回答问题提供基础。5s倒计时结束,开始回复会话后,参与者可以通过按下按钮进行回复操作。当其中一组成功按下接听键时(例如,第2组按下S2键),AT89C51单片机P0口对应的P0.2口线由高变低。当CPU检测到端口线为低电平时,将P1.0端口线从原来的高电平状态切换为低电平,DS1发光二极管亮,P1.7端口线也从原来的高电平状态变化,切换到低电平状态,蜂鸣器会响起,提醒主持人和观众部分玩家已成功完成响应,同时,用数码管将当前抢答题目的题号、抢答成功小组的组号显示出来。

实现方法:选手抢答锁存模块的重点为8个参赛小组抢答按键互相干扰,这些问题可以通过“自锁”与“互锁”操作解决,即当一个小组抢答成功后,抢答器控制系统及时将其按键信息进行保存,并且在有一组抢答成功后将其他组的按键信息屏蔽,从而保证每次的抢答环节只会有一组抢答成功。

抢答器中选手抢答信息输入电路用S1~S8这8个独立按键和8个上拉电阻组合来模拟选手抢答按钮。P0.0~P0.7的初始状态均为高电平,当没有抢答键被按下时,便保持高电平状态,而当有小组按下其抢答按键时,对应的口线就会转换为低电平状态。单片机通过对按键输入口的电平采样判断选手抢答情况。

4.4 数码显示模块

数码显示模块通常有2种显示方式,一种是静态的,一种是动态的。静态显示的一个特点是显示稳定不闪烁,编程简单,但占用的端口资源较多;动态显示的特点是显示稳定性不如静态,编程难度大,但相比静态显示,占用端口资源少。

实现方法:本设计使用BCD编码在6位共阳7段数码管上通过查表法动态显示当前题目号、抢答成功小组号、抢答时间和回答时间等信息。主持人预设抢答时间后,按下STA键宣布抢答环节开始,选手即可开始抢答。初始状态数码管前2位显示当前回答题目的题号,中间2位无显示,最后2位数字显示回答问题的时间和回答问题的时间。如果玩家在回答倒计时期间按下了回答按钮,数码管第3位就会显示选手编号,后2位数码管开始显示回答问题倒计时,本设计中回答时间初始值设为30s。当选手在规定时间内完成作答,然后主持人按下重置按钮手动重置。如果响应时间结束,没有人回答,则本轮抢答视为无效,程序将自动复位准备下一轮抢答。

4.5 抢答结束报警模块

在主持人按下开始按钮和选手按下抢答器按键时,蜂鸣器会发出响声。除此之外,在抢答倒计时和回答倒计时最后5s,蜂鸣器也会发出警报声,并且在非规定时间内选手按下抢答按键时蜂鸣器也会发出警报声提示非法抢答。考虑到诸多因素对本设计进行完善后使抢答器仿真更加直观逼真。倒计时最后5s发出报警声,与实际生活中的抢答器更加契合,体现了设计的实用性。

实现方法:通过芯片引脚输出的高低电平来控制蜂鸣器驱动电路的运行和关闭。蜂鸣器是一种一体化结构的电子讯响器,采用直流电压供电,广泛应用于电子产品中作发声器件。蜂鸣器的工作电流一般相对较大,所以单片机无法将其直接驱动。最简单的喇叭驱动方式就是利用达林顿晶体管,或者以2个常用的小晶体管连接成达林顿架势。蜂鸣器驱动电路中,电阻R为限流电阻,在此利用晶体管的高电流增益,以达到电路快速饱和的目的。如果要由P0输出到此电路,还需要连接一个10k的上拉电阻。在本电路程序设计中使用放大电路来驱动蜂鸣器,即使用1个NPN三极管来放大电流,从而使蜂鸣器可以正常工作。蜂鸣器驱动电路如图4所示。

5 抢答器的实现及结果验证

利用Keil软件进行程序的检查调试,调试完成后在仿真器中设置生成hex文件,编译无错误后进行Proteus仿真。所用的元器件有:15个机械按键、12MHz石英晶体、5V直流電源、2个22pF电容、1个1uF电解电容、9个10kΩ上拉电阻、共阳4位7段数码管、蜂鸣器。

本抢答器系统工作流程为:比赛开始,当主持人按下开始按键后抢答倒计时模块开始运行,系统默认的初始抢答时间为10s,而该时间可由主持人根据情况进行调整。在抢答时间内如果有选手抢到该题目,蜂鸣器则会发出警报提醒该组选手进行作答,系统默认答题时间为30s。仿真模拟情景为:当前抢答题目为第13题,数码管显示“13”。当第2组在抢答时间内按下按键时,数码显示器会显示该组组号“2”,并且显示所剩回答问题的时间“30”。仿真结果如图5所示。

6 结语

本设计采用AT89C51单片机实现多功能八位转发器,采用Proteus仿真软件实现整个设计过程的仿真。得益于强大的仿真系统,对开发的系统进行实时仿真,以确定系统设计的正确性和合理性。硬件图是根据仿真原理图制作的,这种设计具有传统逻辑设计方法无法比拟的优势。设计整体性好、人性化强、可靠性高,实现了数显控制的智能化,该抢答器不仅可以实现倒计时、数显等基本功能,还可以自定义响应倒计时和倒计时时间,让选手可以根据不同的游戏场景答题,有效判断选手非法抢答并给予警告。系统经验证工作稳定,保证了比赛中抢答的公平性。

【参考文献】

【1】黄育雁.智力竞赛抢答器逻辑电路的设计[J].硅谷,2012(6):56+33.

【2】段德功,丁莹亮.单片机原理及应用[M].北京:经济科学出版社,2010.

【3】牛甲,熊刚.基于单片机的的抢答器设计[J].电脑知识与技术,2018,14(4):240-241.