面向FPGA应用的硬件木马植入与检测技术研究

2021-10-28姜佩贺王晨旭位寅生

姜佩贺,王晨旭,郭 刚,位寅生

1.山东渔翁信息技术股份有限公司,山东 威海 264200

2.烟台大学 光电信息科学技术学院,山东 烟台 264005

3.哈尔滨工业大学 电子与信息工程学院,哈尔滨 150001

硬件木马(Hardware Trojan Horse,HTH)是一种被恶意攻击者植入在集成电路内部的冗余电路[1-2]。该冗余电路一般处于潜伏状态,只有在特定的条件下才能被触发,触发后将执行某种恶意的功能,如关键信息泄漏、芯片意外失效等[3-5]。

近年来,随着新一代信息技术的快速发展,FPGA在高性能计算、5G、人工智能、物联网等领域的应用愈加广泛。阿里云、腾讯云、百度云等先后部署了基于FPGA的云加速服务器,微软将FPGA用于加速必应搜索,在密码学领域,FPGA以协处理器的形式完成签名验签等密码算法,保障信息安全的。

FPGA生命周期的多个阶段可能被植入硬件木马,从而对信息安全造成威胁。第一,目前主流FPGA厂商均来自于国外,且在FPGA器件开发进程中,厂商会使用第三方IP以缩短开发周期,这为木马的植入创造了条件;第二,目前集成电路设计和制造相分离,FPGA芯片在第三方公司的制造过程,可能被恶意植入硬件木马;第三,在FPGA应用开发过程中,EDA软件来自国外,其对RTL代码的处理过程是黑盒的,攻击者在此阶段也可以植入木马;第四,FPGA的配置文件保存在FPGA芯片外部,恶意攻击者可以通过偷换或修改配置文件实现木马的注入。FPGA应用场景广泛,如果在国防、金融、交通等关键场景使用的FPGA被植入了硬件木马,将对国家安全造成巨大的威胁。因此,对FPGA中硬件木马检测技术的研究势在必行。

硬件木马检测技术用于发现木马的存在,近年来研究者针对硬件木马检测展开了广泛研究。目前主流的检测技术主要有物理检测[6-7]、逻辑测试[8]、内建自测试[9]和侧信道分析[10-12]等,其中基于侧信道分析的检测方法是近年来的研究主流。

基于环形振荡器(Ring Oscillators,RO)的检测方法[13-14]由Zhang等提出,该方法属侧信道分析中的一种,是在集成电路设计时,在芯片版图的不同区域设计环形振荡器,通过分析芯片中环形振荡器的频率输出特性,判断集成电路是否遭到恶意更改或木马植入。在该方法提出后,Ferraiuolo等[15]使用环形振荡器和主成分分析法检测ASIC中的硬件木马;Kitsos等[16]分析了环形振荡器级数与灵敏度的关系;在此基础上,Pirpilidis等[17]提出了级数可配置的环形振荡器结构;赵毅强等[18]讨论了工艺偏差对木马检测的影响,并提出校正方法;Alsaiari等[19]提出了基于可配置断言(RAC)的检测方法。

调研发现,基于RO木马检测方法的研究均是面向专用集成电路ASIC而展开的,而随着FPGA应用领域的不断扩展,在FPGA中开展硬件木马的检测更是不可或缺的,但由于EDA软件对RTL代码的处理流程是黑盒的,因此,如何通过添加约束在FPGA内部准确部署RO,以及如何植入木马以分析该方法在FPGA中的木马检测效果都是需要深入研究的。

基于此,本研究在分析RO检测方法原理的基础上,设计基于RO的木马检测电路,在FPGA中精确布局RO位置,在Altera FPGA中通过增量编译技术植入四种类型的典型木马,使用归一化差值进行数据分析,最终实现木马的检测和定位。

1 环形振荡器及硬件木马检测原理

环形振荡器是由奇数个反相器首位相接而构成的电路结构,它可以利用门电路的传输延迟特性产生自激振荡,图1为由3个反相器构成的环形振荡器。

图1 由三级反相器构成的环形振荡器Fig.1 Ring oscillator composed of three-stage inverter

在环形振荡器中,假设一级门延迟为tpd,则由n级反相器级联构成RO的振荡周期为T=2ntpd。在实际集成电路中,每一级的门延迟可以由公式(1)表示[20]:

式中,CL为等效负载电容,k′为跨导,W/L为晶体管宽长比,VDSAT为饱和电压,Vth为阈值电压,Vdd为电源电压。由公式(1)可知,门延迟tpd不仅与集成电路工艺有关而且与电源电压有关。特别是深亚微米工艺下,Vdd已不再远远大于Vth+VDSAT/2,电源电压对门延迟的影响更不容忽视。

基于环形振荡器的硬件木马检测原理正是利用了电源电压对门延迟的影响。在现代集成电路中,芯片内部分布着极为密集的电源网络,元器件的增减会影响其周围的电源电压。为实现硬件木马的检测,在集成电路设计过程中,需要在版图不同的区域插入RO,如果在芯片制造时遭到了恶意木马植入,则当芯片工作时,木马周围RO的振荡频率会发生变化,木马规模越大、距离RO越近,对振荡频率的影响越大。通过将此频率与不含有硬件木马的“黄金芯片”此频率进行数据分析,即可实现木马的检测与定位。

2 检测系统设计

2.1 环形振荡器的设计

传统的环形振荡器由奇数个反相器构成,在本设计中,环形振荡器采用基于与非门的结构,原因有以下三点:一是相同级数的与非门RO比反相器RO的振荡周期更长;二是当使用与非门构成环形振荡器时,与非门的一个输入端需要直接连接到VDD,电源电压变化对振荡频率的影响更大;三是可以通过增加受控端EN实现对振荡器工作与否的控制。图2为使用三级与非门构成的环形振荡器。

图2 由三级与非门构成的环形振荡器Fig.2 Ring oscillator composed of three-stage NAND gate

RO网络中RO的数量决定了检测精度,数量越多,每个RO负责检测的区域越小,检测精度越高,但却更加浪费资源;在每个RO中,反相器(与非门)的级数也需要进行权衡,若级数过少,振荡频率就会很高、功耗更大,并且测量高频振荡频率难度更大、测量精度更差。若级数过多,虽然检测精度会提高,但却占用更多的硬件资源。综合权衡后,本设计使用的环形振荡器网络包含6个RO,每个RO包含121级与非门。在其他应用中,根据基础功能电路规模,可以对该数量进行调整。设计的RO网络如图3所示,网络中的6个RO呈分布式布局,分别用于检测自身附近区域的硬件木马。

图3 分布式环形振荡器网络示意图Fig.3 Schematic diagram of distributed ring oscillator network

在基于RO的木马检测方法中,需要根据电路系统规模将RO插入到电路的指定位置。现有研究[15,17,19]主要是针对ASCI展开,ASIC的版图完全由设计者自行规划,可以很自由地规划RO位置。但是在FPGA实现过程中,EDA软件对RTL代码的处理是黑盒的,为将RO约束在指定位置,可以在Quartus II中,将相应的RO模块设置为Logic-lock区,通过修改Logic-lock区的参数,以将其规划在理想的位置。

2.2 检测电路设计

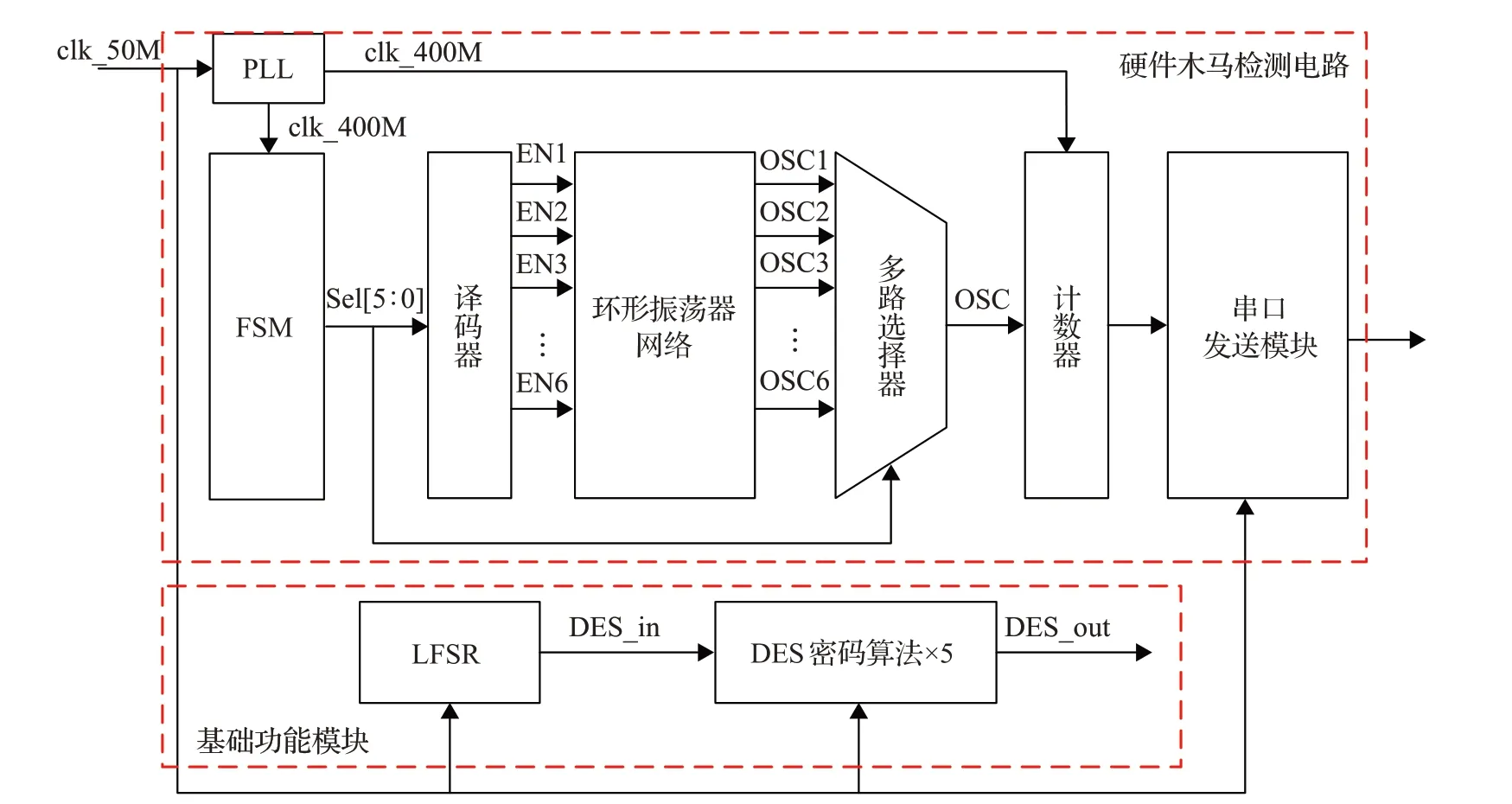

设计的基于环形振荡器的硬件木马检测电路结构如图4所示。这里假定芯片的基础功能为5个并行的DES(Data Encryption Standard)加密算法,DES算法用于保证数据传输安全,在敏感数据保护领域应用广泛。DES算法的明文输入由线性反馈移位寄存器LFSR提供,在对待测芯片和黄金芯片(已知不含木马的电路)的每次检测中,LFSR应使用相同的种子,以保证基础功能电路执行相同的逻辑运算。

图4 基于环形振荡器的硬件木马检测电路结构Fig.4 Hardware Trojan detection circuit based on ring oscillator

检测电路由锁相环PLL、有限状态机FSM、译码器、环形振荡器网络、多路选择器、计数器和串口发送模块组成。系统的输入时钟是50 MHz,为了更精确地检测出RO的振荡频率,使用PLL将时钟倍频至400 MHz。环形振荡器网络是检测模块的核心,网络中的每一个RO是分时轮询工作的,具体流程如下:有限状态机FSM包含6个状态,分别用于轮询每一个RO,在某一状态下,译码器通过ENn信号使能该RO,多路选择器将该RO产生的振荡信号OSCn输出到计数器。计数器对振荡频率进行测量,为提高测量精度,计数器每一次测量n个RO振荡周期内的时钟(400 MHz)周期数。在测量时钟频率一定的条件下,测量时间越长,检测精度越高,这里取n=2 047。最终,串口发送模块将6个RO的轮询数据打包发送至上位机。

3 硬件木马与植入技术

3.1 四种典型硬件木马设计

硬件木马通常包含触发电路和负载电路两个部分,按照触发电路和负载电路的工作情况可以将木马电路分为全激活状态、部分激活状态和静止状态三种状态。(1)全激活状态是指当触发条件满足时,木马被触发,负载电路开始工作;(2)部分激活状态是指触发条件没有满足,虽然硬件木马处于未被触发的状态,但木马电路内部部分电路节点发生翻转是不可避免的;(3)静止状态是指经设计者的精心设计,硬件木马未被触发,并且内部的所有电路节点都完全不翻转。全激活和部分激活状态下木马电路存在动态功耗,而静止状态不存在动态功耗。但静态功耗是三种状态都不可避免的,并且随着工艺尺寸的不断下降,静态功耗在总功耗中的占比日益增大。

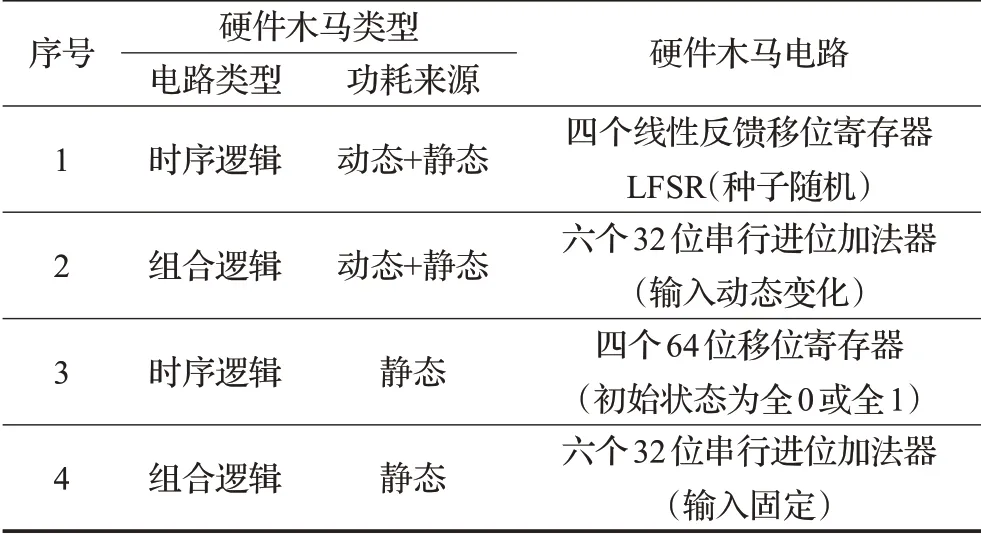

硬件木马本质上为冗余电路,因此,本研究使用线性反馈移位寄存器和串行进位加法器分别代表组合型和时序型木马。根据电路类型以及功耗的来源,设计了四种类型的木马,具体如表1所示。同时,为了方便对比,经过优化,4种电路占用的逻辑资源基本相同。

表1 四种典型的硬件木马Table 1 Four typical hardware trojans

3.2 木马的植入

为了测试木马检测效果,木马植入技术也是需要进行细致研究的。这里假设恶意攻击者通过修改版图实现硬件木马的植入。即在木马植入前后,除恶意冗余电路外,其他电路应具有相同的布局布线结果,即版图相同。这在ASIC设计中是很容易实现的[15,17,19],但在FPGA木马检测的相关研究中并没有类似的讨论,在文献[16]中也仅仅提到了在Xilinx FPGA中需要PlanAhead工具。

本研究提出了在Altera FPGA中使用Quartus II的增量编译(Smart Compilatio)技术实现该要求的方法。该方法克服了综合优化等过程由EDA工具自动完成所造成的困难。在增量编译过程中,只有增量编译前后的模块具有相同的输入输出,编译才不发生错误。即在含有和不含有木马的电路中,冗余电路模块都要具有相同的输入输出。为满足该要求,在含有木马的电路中植入真实的木马(以下简称真木马),而在不需要含有木马的电路中,植入最简单的门电路(以下简称假木马),假木马的目的仅仅是为了保证与真木马有相同的输入输出,由于仅由几个门构成,对系统的影响可以忽略。

使用增量编译技术实现木马的植入方法有两种,分别是“先预留再植入”和“先植入再移除”。“先预留再植入”是指首先编译含有假木马的电路,这个过程相当于是预留,然后再将假木马换为真木马,进行第二次编译;另一种方法是“先植入再移除”,是指第一次编译含有真木马的电路,然后将真木马换为假木马,再进行第二次编译。先植入再移除的方法更好地模拟了ASIC流程中硬件木马的植入环境,硬件木马被植入在原始版图的空白部分。因此,本设计采用“先植入再移除”的方法植入硬件木马。

植入硬件木马前后的FPGA版图如图5和图6所示。图中颜色较深的蓝色区域表示该逻辑资源已被占用,颜色较浅的区域表示未被占用。由图可知,RO1~6被约束在版图中的不同位置,并在RO3附近植入了硬件木马。对比可以发现,植入木马前后只是在木马约束区域内版图有所不同,其余部分是完全相同的。因此,在后续实验中,若环形振荡器振荡频率发生变化,则影响一定来源于硬件木马的植入。

图5 植入假木马(无木马)时FPGA版图Fig.5 FPGA layout with fake Trojan horse(without Trojan horse)

图6 植入真木马时FPGA版图Fig.6 FPGA layout with Trojan horse

4 实验结果与分析

针对四种典型的木马电路,依次进行四次实验。每次实验使用两块FPGA开发板,其中一块加载不含木马的比特流,另一块加载是含有木马的比特流。程序加载后,不同RO的振荡频率将通过串口发送至上位机,采用多次测量求平均值的方式抵消噪声和测量误差,设定的平均次数为200次。

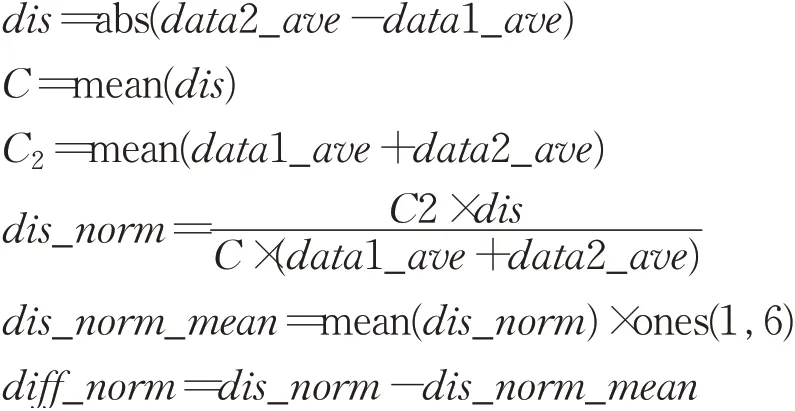

使用归一化差值算法对平均后的数据进行处理,具体算法如下:

其中,data1_ave和data2_ave分别表示含有木马和不含木马的数据采集矩阵,矩阵大小为1×6,矩阵中的6个元素分别为6个RO进行200次平均后的振荡频率;mean为求矩阵均值函数;abs为取绝对值函数;ones(1,6)表示一个大小为1×6且元素为1的矩阵。

图7(a)~(d)分别展示了不同类型木马的数据分析结果,在四幅图中,RO3处都存在明显的尖峰,即采用所提出的方法,四种类型的木马均被成功检出。在图7(c)和图7(d)中,虽然RO3出存在尖峰,但尖峰值明显小于图7(a)和图7(b)的结果,这是因为第一组实验和第二组实验中的硬件木马既有动态功耗又有静态功耗,而第三组和第四组实验中的硬件木马只有静态功耗。这与前文的分析是一致的。

图7 木马检测结果Fig.7 Detection results of Trojan horse

相关文献大都针对ASIC展开,并且在不同的文献中,作者植入的木马不尽相同,因而无法进行横向的对比,但本实验对仅具有静态功耗的木马电路3和木马电路4能够成功检测,这在相关文章中是不多见的,这不仅说明了所提出方法的有效性,更印证了其先进性。

5 结束语

保障国家信息安全,建设安全自主可控的信息体系已成为国家战略。本研究面向FPGA应用,在基于环形振荡器的硬件木马检测方法之上,通过在FPGA内部部署RO,使用增量编译技术实现了四种典型木马的植入,使用归一化差值算法发现并定位了木马。检测结果表明,基于环形振荡器的硬件木马检测方法在FPGA中具有很好的木马检出效果。所提出的方法已经在公司实际FPGA产品中使用,为及时发现木马,保证信息安全提供了一种有效途径。然而,木马种类千变万化,攻击者的植入方式也越来越高明,只有进一步提高国家综合实力,打造具有自主知识产权的中国芯,才能从根本避免受到硬件木马的侵害。