基于XC7Z045ffg-900 芯片的信号处理板功能设计

2021-10-23孙伟玮王馨悦

孙伟玮,王馨悦

(1.海军装备部,陕西西安,710069;2.西安微电子技术研究所,陕西西安,710054)

0 引言

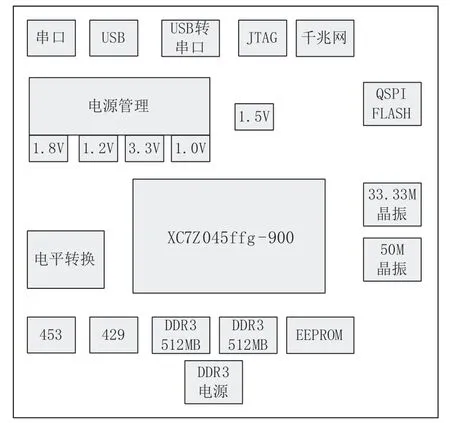

本文设计的信号处理板使用的核心芯片Xilinx 公司Zynq7000 系列,芯片型号为XC7Z045ffg-900。该芯片集成了基于ARM 公司双核ARM Cortex-A9 多核处理器的处理系统(PS),以及基于Xilinx 可编程逻辑资源的可编程逻辑系统(PL)。利用该芯片丰富的外部接口、内外部存储及灵活的配置,作者设计了一块具有DDR3 SDRAM、ARINC429、ARINC453、EEPROM、串口、USB接口、USB转串口、QSPIFLASH、JTAG、千兆网、电源管理等。

1 基于XC7Z045ffg-900 芯片的信号处理板功能设计

如图1 所示为整个信号处理板功能示意图。

通过图1 我们可以看到,该信号处理板的接口和功能。具体如下:

图1 信号处理板功能示意图

(1)核心芯片:XC7Z045ffg-900,Xilinx 的ARM+FPGA结构,为整个电路提供丰富的硬件资源和各种外部接口,以及存储资源等。XC7Z045ffg-900 芯片的PS 端拥有128 个IO 接口,用于处理系统的专用引脚,有16 对共64 个高速串行收发引脚,可用于设计SRIO、PCIE 等高速通信接口。XC7Z045ffg-900 芯片的PL 端有普通的IO 引脚362 个,其中HP 引脚212 个,HR 引脚150 个,设计的时候要注意HR 引脚的BANK 中的电压范围为1.2V 到3.3V,HP 引脚的BANK 中的电压范围为1.2V 到1.8V。XC7Z045ffg-900 芯片的BANK0 中有17 个配置引脚,如JTAG 等。另外还有32 个XADC 模数转换引脚。

设计的时候需要注意时钟端需接入具有MRCC 或者SRCC的引脚,其中MRCC 是multi-region clock,当时钟是单端时,时钟信号必须接入MRCC 的正端,SRCC 是single-region clock,当时钟是单端时,时钟信号必须接入SRCC 的正端。设计的时候也需要按照产品手册进行滤波处理,电容的大小和封装,以及数量须严格按照产品的数据手册的要求进行设计,以保证信号的质量。

(2)电源管理:外部4V-14V 宽压输入,通过LTM4644 芯片产生4 路4A 的输出,分别为1.8V、1.2V、3.3V 和1.0V。为信号处理板各个模块提供相应的电源。LTM4644 通过调节电阻值来产生不同的电压值,电容调节不同电压的上电时间,pgood 引脚可以控制XC7Z045ffg-900 芯片的上电 顺 序,1.0V-----1.2V-----1.8V-----3.3V。通 过LT1963-1.5芯片为XC7Z045ffg-900芯片的DDR部分提供电源。其他模块如串口、电平转换、FLASH、晶振等都可以使用LTM4644 和LT1963-1.5 产生的电源。

(3)DDR3:XC7Z045ffg-900 芯 片内嵌有存储器块,但一般其存储容量不大。当设计时用户设计的系统需要有大量的数据存储和读写时,需要用到片外DDR存储器,这时XC7Z045ffg-900 芯片需要有与外部存储器的高速接口。XC7Z045ffg-900 芯片中的DDR 存储器接口是为XC7Z045ffg-900 用户电路提供对片外的DDR SDRAM 的访问控制。XC7Z045ffg-900 芯片可以设计为PL 端的DDR3,也可以设计为PS 端的DDR3,或者两者皆有,本设计考虑到资源分配及实际应用,采用的是PS 端的DDR3 来完成。两片高速DDR3 SDRAM,型号为为MT41J256M16HA-125,可以用作芯片的数据缓存,也可以作为操作系统运行的内存。

(4)EEPROM:一种掉电后数据不丢失的存储芯片,IIC接口的EEPROM,型号为24LC04。EEPROM 写数据的过程为:a.IIC 的起始信号;b.发送要写数据存储地址;c.按顺序发送要存储的数据的字节。EEPROM 读数据的过程为:a.IIC的起始信号;b.发送要读数据存储地址;c.重新发送要读取的数据的地址;d.读取从器件发回的数据。

(5)ARINC429:ARINC429 总线协议规范定义了航空电子设备进入飞机数据网络所遵循的数字信息传输要求。基本的报文格式是32 位的字,主要由五部分组成,分别是奇偶校验位、符号状态矩阵、数据域、源/目的地标识符和标签号。对于有ARINC429 要求的信号处理,本设计通过HI8591 和HI8592 这两种芯片,可完成XC7Z045ffg-900 里的普通信号与ARINC 429 的转换。

(6)ARINC453:ARINC453是一种航空总线,共有1600bit的数据需要传输。本设计通过HI2579 芯片,可完成XC7Z045ffg-900 里的普通信号与ARINC 453 的转换。

(7)电平转换:在本设计中,XC7Z045ffg-900 芯片内部,DDR3 数据的电平格式为1.5V,HP BANK 中相关数据的电平格式为1.8V,HP BANK 中相关数据的电平格式为3.3V。而这些数据与外相连的芯片要求的电平往往不能与之匹配,因此,需要电平转换芯片将不同电平格式的信号转换为电平格式相匹配的信号。本设计通过SN74ALVC164245 与txs0108 这两种芯片完成不同信号电平的转换。其中SN74ALVC164245 芯片是单向转换,配置简单只需对OE 引脚和DIR 引脚进行拉高或者拉低就能确定信号的流向。而txs0108 芯片是双向转换,不需要配置即可实现信号电平的双向转换。

(8)晶振:XC7Z045ffg-900 芯片工作的时候需要外部晶振提供时钟,本设计板载一个33.33MHz 的有源芯片晶振,为PS 系统提供稳定的时钟源,接入BANK500 的CLK 引脚上;板载一个50MHz 有源晶振为PL 逻辑提供额外的时钟,设计的时候注意时钟信号必须接入PL 端MRCC 的正端。

(9)QSPI FLASH:是一种专用的通信接口,连接单、双或四条数据线SPI FLASH 存储介质。本设计使用一片256MB 的QSPI FLASH,型号为W25Q256,可用来存储用户的数据以及芯片的系统文件。

(10)串口:用来与PC 机或者外部设备通信。

(11)USB:用来连接鼠标、键盘等外部设备。

(12)JTAG:通过仿真器与PC机连接,用来对XC7Z045ffg-900 进行调试、下载和固化。

(13)千兆网:一路10M/100M/1000M 以太网RJ45 接口,可实现与其他设备的网络通信。

(14)DDR电源:使用LTM4644产生的3.3V电源和LT1963-1.5产生的1.5V电源,采用TPS51200芯片,为DDR3提供终端稳压电源VTT 和VREF。

(15)USB转串口:通过CP2102芯片实现USB转串口通信。

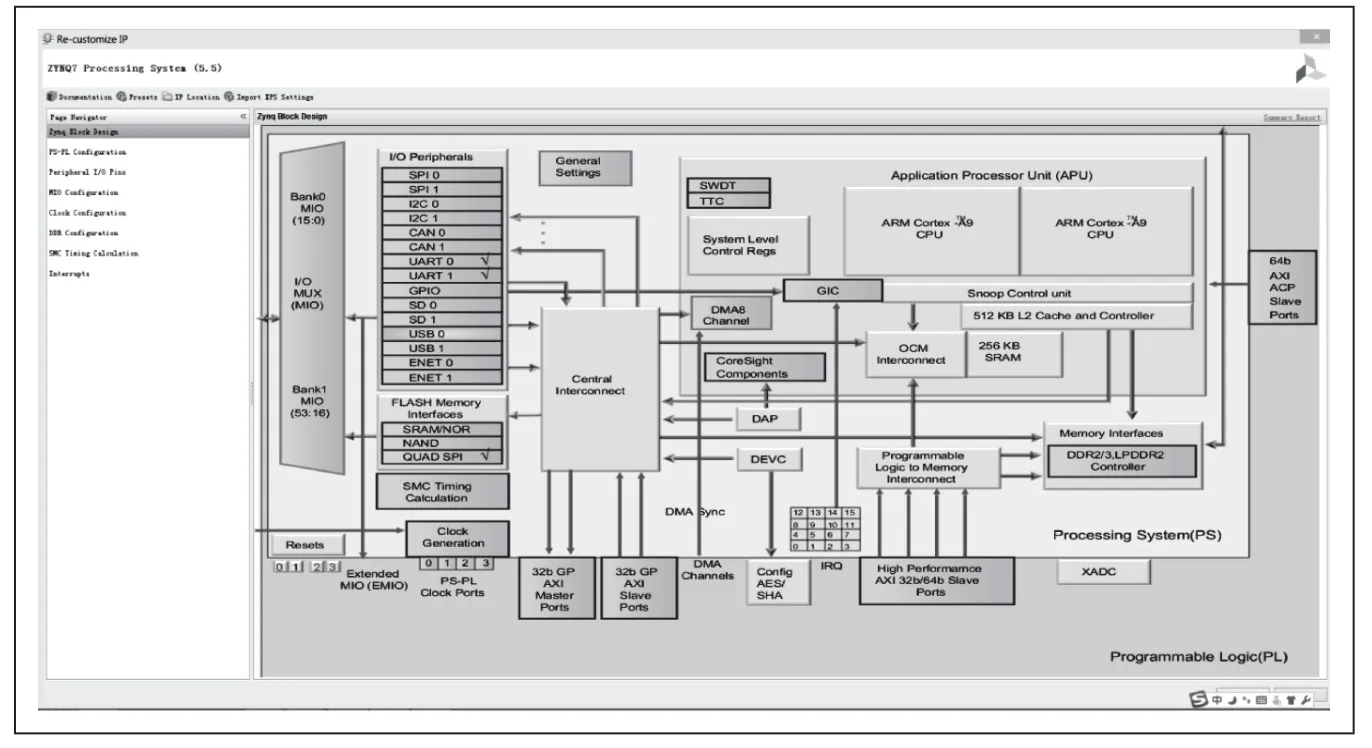

2 基于XC7Z045ffg-900 芯片的信处板PS 端主要功能介绍

XC7Z045ffg-900 芯片的PS 端的总体框图如图2 所示,可根据要求在图的页面上进行相应的选择以实现相应的设计。

图2 XC7Z045ffg-900 芯片的PS 端的总体框图

(1)DDR3 DRAM:XC7Z045ffg-900 芯片PS 端DDR3 有专门的引脚,位于PS 端BANK502 的接口上,总线宽度为32bit。DDR3 的相关引脚直接与XC7Z045ffg-900 芯片PS 端BANK502的专用引进进行相连即可。通过TPS51200 芯片为DDR3 提供VREF 和VTT 电压,确保DDR3 能稳定工作。

设计的时候要注意信号完整性,对于阻抗的控制、线宽、匹配电阻、线等长控制等要严格按照要求进行设计,以确保DDR3 高速稳定的工作。在本设计中,单端信号阻抗控制为50欧姆,差分信号为100 欧姆;数据线要组内等长,控制线、地址线和时钟线要以时钟线为参考做等长,控制误差;蛇形绕线时,单端按3W 原则,差分绕线按5W 原则(其中W 为线宽),组间个信号间距按照3H,不同组间线间距按照5H(H 为到主参考平面间距)。

(2)USB 转串口:本设计是利用XC7Z045ffg-900 芯片PS 端BANK501 的MIO 引脚来实现的,由于XC7Z045ffg-900芯片BANK501 的数据电平与CP2102 芯片的数据不匹配,我们将XC7Z045ffg-900 芯片PS 端引出的信号通过电平转换芯片转换为与CP2102 芯片匹配的信号电平,再连接到CP2102 芯片,从而实现该功能。

(3)QSPI FLASH:本设计是利用XC7Z045ffg-900 芯片PS 端BANK500 的GPIO 接口来实现的,根据要求W25Q256 芯片与XC7Z045ffg-900 芯片相应的引脚直接连接即可。

(4)千兆网:本设计是利用XC7Z045ffg-900 芯片PS 端BANK501 的GPIO 接口来实现的,将PHY 芯片与XC7Z0 45ffg-900 芯片相应的引脚直接连接即可。

(5)USB:本设计是利用XC7Z045ffg-900芯片PS端BANK501 的IO 接口来实现的,将USB3320C 收发器与XC7Z045 ffg-900 芯片相应的引脚直接连接即可实现通信,其中USB3320C 收发器需要板载一个24MHz 的晶振为其提供系统时钟。

3 基于XC7Z045ffg-900 芯片的信处板PL 端主要功能介绍

(1)EEPROM:本设计是利用XC7Z045ffg-900 芯片PL 端BANK35 的IO 接口来实现的,连接到,只需要将24LC04 芯片的SCL 和 SDA 的引脚与BANK35 的IO 引脚直接相连即可实现。

(2)ARINC429:在XC7Z045ffg-900芯片中电平为3.3V的BANK中设计8路差分信号,每一组差分信号通过HI8591 芯片转换为所需的ARINC429 信号;通过HI8592 芯片将外部4 路ARINC429 信号转换为普通差分信号再连接到XC7Z045ffg-900 芯片中电平为3.3V 的BANK 中的差分对上,实现ARINC429 通信。

(3)ARINC453:在XC7Z045ffg-900 芯片中电平为3.3V的BANK 中设计1 路差分信号,该差分信号通过HI2579 芯片转换为所需的ARINC453 信号,实现通信。

(4)JTAG:将XC7Z045ffg-900 芯片BANK0 中的专用引脚TMS、TCK、TDI 和TDO 通过10K 上拉电阻上拉,连接到外部插座上,用来连接仿真器,完成调试、下载和固化的功能。

(5)通用IO:将多余的IO 口(包括单端信号和差分信号),直接引出来连接到插座上,以便后续扩展使用。

4 结论

本文介绍了通过Xilinx 公司的芯片XC7Z045ffg-900设计的信号处理板,该信号处理板拥有丰富的接口设计,和大容量的存储,可灵活使用。具有DDR3 SDRAM、ARINC429、ARINC453、EEPROM、串口、USB接口、USB转串口、QSPI FLASH、JTAG、千兆网、电源管理等模块,通过PS 和PL 协调工作,可提高信号处理板的处理速度,加快开发人员对项目的开发进程。该信号处理板与不同的接口数据通信,并进行相应的信号处理,可以满足常规应用,通过一块芯片就可以同时实现Cortex-A9 双核ARM 和FPGA,是目前较为流行的方式。