扇区水泥胶结测井仪的低功耗设计与实现

2021-09-27杭州瑞利声电技术有限公司张亦弛

杭州瑞利声电技术有限公司 张亦弛

针对扇区水泥胶结测井仪在缆测模式下发射功耗过大问题,本文设计一种带存储功能的声波信号预处理电路,将扇区、CBL以及VDL信号进行预存储后再逐个上传,从而降低了换能器发射频率。实验表明,该设计成功适配Warrior地面系统,同时达到了降低功耗的目的。

扇区水泥胶结测井仪是一种用于检测套管水泥胶结质量及孔穴沟槽的有效仪器。在缆测模式下,仪器配接Sondex公司的Warrior地面系统,通过单芯电缆直接上传数据。由于仪器需要直接适配软件协议,而声波数据无法存储在仪器中,所以每发射一次只能上传一路模拟信号,发射换能器的发射间隔为25.6ms,因而增加了发射功耗。本文分析了传统缆测方式下电路的不足,结合存储式仪器的优点,提出一种带预存储功能的信号采集上传电路设计方法,达到降低仪器功耗的目的。

1 传统信号接收上传电路

根据Warrior地面针对RIB仪器的通讯时序,在一个工作周期中,共分为12个小周期,井下仪器需要分时上传数据,按顺序依次为起始头(内容空)、扇区1~8、3ft、校准、5ft,每个小周期为25.6ms。

传统缆测模式信号接收上传电路中,在每个小周期,逻辑控制单元产生同步脉冲与发射脉冲,并控制开关电路选择不同通道的声波信号,与同步头叠加后通过功放电路上传至地面系统。在此种情况下,一次只能将一个通道信号实时上传,因此每个小周期内均需激发换能器重新发射,即换能器的发射频率为25.6ms,发射脉冲为25us,充电时长为75us,换能器的容值约为9nF,在一次放电周期中换能器两端发射电压2700V,则根据电容电流公式(1):

其中U为电容两端最大电压,I1为放电电流,t1为放电时长,I1为充电电流,t1为充电时长,T为发射周期,功耗可预估为2.56W。当一个大周期中只发射一次时,即发射周期为307.2ms,放电周期将会减少至原先的1/12,功耗也相应的减少至0.213W。

2 带预存储功能的上传电路

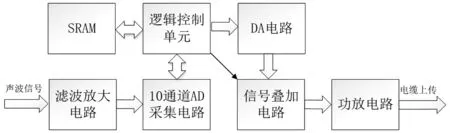

为了减少发射频率,设计带预存储功能的信号接收上传电路框图如图1所示。

图1 改进后的信号接收上传电路框图

如图1所示,在一个周期的开始,发射换能器只激发产生一次发射脉冲,接收换能器接收声波信号,转换为电压信号后,进入10通道的前放电路进行噪声抑制和滤波放大,之后再经过10通道的AD采集电路进行数字化,并且预存储在SRAM中。逻辑控制单元在之后的11个小周期控制产生同步头,同时将对应通道的声波信号通过DA电路恢复为模拟信号,经过信号叠加电路以及功放电路进行电缆上传。

2.1 滤波放大电路设计

滤波放大电路由一级前放电路、一级带通滤波电路以及一级放大电路组成。

前置放大电路的作用是对接收换能器进行阻抗匹配,同时对噪声进行抑制以提高信噪比。本设计中选用一款超低噪声、低功耗的仪用放大器,输入电压噪声为,同时在较低增益时,带宽在500KHz以上,满足输入信号的要求。

带通滤波电路的作用是滤除信号带宽以外的信号。扇区、3ft和5ft有用的声波信号在20KHz左右,所以使用低噪声运放构成一级二阶的有源带通滤波器,对声波信号进行调理。

放大电路的作用是对信号放大到合适的幅值,匹配模式转换器,使得有更好的动态范围。

2.2 存控采集电路设计

存控采集电路主要由FPGA、外部SRAM和ADC组成。FPGA作为处理器,周期性的产生发射信号,同时控制多通道模数转换芯片进行信号采集,将采数字化的采集结果暂存在SRAM中。在采集完成之后的小周期内,FPGA还负责按顺序读取SRAM中的声波数据,交给数模转换器进行复原。本设计中选用了Actel的一款FPGA,最多有100万个系统门和300个用户IO口,同时具有超低功耗的优点,资源满足需求。

ADC芯片的选用取决于信号。声波信号的频率大概为20KHz,根据奈奎斯特采样定理,要使数字化之后的信号完整保留模拟信号的信息,则采样频率应大于信号频率的2倍;而在实际应用中,采样频率会大于信号频率的10倍,所以本设计中将采样频率设置为500KHz。因此选用了一款14位双通道高速模数转换芯片,采样率最高可达到1MHz,2个通道同步采样。设计中使用了5片ADC芯片同步采样,构成了8路扇区、1路3英尺和1路5英尺的10通道信号采集。

SRAM的选用由声波数据的总采样点数决定。各扇区采样1ms,3 ft和5 ft各采样1.5ms,则一个周期内的总采样点数为5500个,所以存储空间应大于4750字。在本设计中选用了一款131072字的SRAM,同时具有出色的读写速度。

2.3 信号复原上传电路设计

信号复原上传电路的作用是通过数模转换芯片将已存储的信号恢复为模拟信号,再通过功放电路进行上传。由于前端AD的采样频率为500KHz,所以要求后端DA的输出频率也要达到500KHz以上。因此,本设计中选用了一款12通道的高速DA芯片,数字端串行接口最高达到50MHz,模拟端输出建立时间为0.2us。实际使用了20MHz作为通讯时钟,因此从开始写入到最终DA稳定输出的时间小于1us,满足了500KHz的要求,在经过长电缆滤波后,DA产生的毛刺微乎其微。

功放电路的设计是为了提高信号的驱动能力,使得经过测井电缆的衰减后,在地面还能有较高的幅值与信噪比。功放电路由两级运放组成,如图2所示。

图2 两级功放电路

图2中,第一级U1为超低噪声、低失调输入的精密运放,第二级U2为具有大电流输出的功率运放,通过R2和R3整体构成一个负反馈电路,增益为1+R3/R2。从而功放电路既有前级较好的输入特性,又有后级较强的输出能力。

2.4 电路测试结果

在整体电路设计与调试完成后,进行水压试验以检测电路性能。将声系装入压力桶中,打入3Mpa的水压,运行仪器,在Warrior地面系统监测实时波形,3ft、校准信号、5ft、8道扇区以及同步头的波形清晰,各路信号到时准确,扇区的一致性也比较好,电路达到了适配Warrior地面系统的效果。

结束语:与传统直接上传方式的电路相比,改进后的电路有以下优点:

(1)降低发射功耗。由于降低了发射频率,发射功耗得到了很大降低。同时,发射变压器以及发射换能器的使用寿命也得到了提升。

(2)由于传统方式发射间隔短,所以很容易导致上一周期的声波信号干扰到当前周期的基线。而改进后的电路,所有信号的采集均开始于同一时刻,且两个周期间隔大于300ms,间隔足够长,不存在相互影响。

(3)传统方式使用了电子开关进行不同通道的选通,而在开关切换过程中会产生毛刺影响基线。改进后的电路只存在DA输出的毛刺,实验发现此毛刺远小于开关产生的毛刺。

(4)改进后的电路实际上对存储式仪器的前端采集和缆测仪器的后端上传进行了结合,很容易拓展为兼容存储和缆测两种模式,而非完全独立的两套电路,减少了设计复杂度与成本。