带有传输零点的增益提高型N 通道带通滤波器

2021-09-24吕芸芸蒋品群宋树祥蔡超波岑明灿

吕芸芸,蒋品群,宋树祥,蔡超波,岑明灿

(广西师范大学 电子工程学院,广西 桂林 541004)

近年来,随着5G 等新的通信标准的提出,人们对多模多频无线设备的性能要求也越来越高[1-2]。为了保证信号正常处理,要求多模多频接收机系统必须能够抵抗强干扰[2-4]。传统的接收机前端常用声表面波和体声波滤波器来抑制干扰,但此类滤波器可实现的调谐范围非常有限,且不易集成,对于多模多频接收机,需要多个中心频率不同的滤波器,使得接收机体积大,成本高。为了减小接收机体积,节约成本,20 世纪60 年代,N通道滤波器[3]被提出。与声表面波滤波器相比,N通道滤波器具有中心频率可数字化调节、易于集成等优点,在多模多频接收机前端以及软件定义无线电技术中被广泛应用。

然而,受开关电阻的影响,无源N通道滤波器[5-8]带外抑制有限,无法有效滤除信号干扰[5]。文献[5]虽然详细分析了N通道滤波器中开关电阻对带外抑制的影响,但并未提出改善带外抑制的有效解决方案。文献[6]设计了一款高阶无源N通道滤波器来改善带外抑制,但效果并不显著。文献[7]则通过带通滤波和带阻滤波的组合来提高带外抑制,虽然效果较好,但电路结构过于复杂。文献[8]设计的有源N通道滤波器,通过带凹口的开关LC 来提高带外抑制,在0.7~1.0 GHz 可调谐范围内,带外抑制大于50 dB,得到有效改善,缺点是增益小,噪声系数大。

为了在提高带外抑制的同时也提高增益,本文在有源滤波器的通带两侧各引入一个传输零点,设计了一款高增益高带外抑制型N通道带通滤波器。有源滤波器中的放大器为带有N通道开关电容网络的米勒放大器,可以有效减小基带电容面积。

1 N 通道带通滤波器

1.1 整体电路结构设计

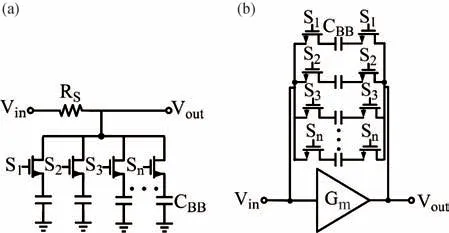

基本的无源N通道滤波器结构[3]如图1(a)所示,在一个采样周期内,由N 相非重叠时钟依次控制N个开关的通断,实现带通滤波,但该滤波器无增益提升特性,且带外抑制非常有限。图1(b)为有源N通道滤波器结构[9],引入跨导放大器来提供增益,米勒反馈网络减小基带电容面积,但带外抑制并未改善。

图1 (a)无源N 通道滤波器;(b)有源N 通道滤波器Fig.1 (a) Passive N-path filter;(b) Active N-path filter

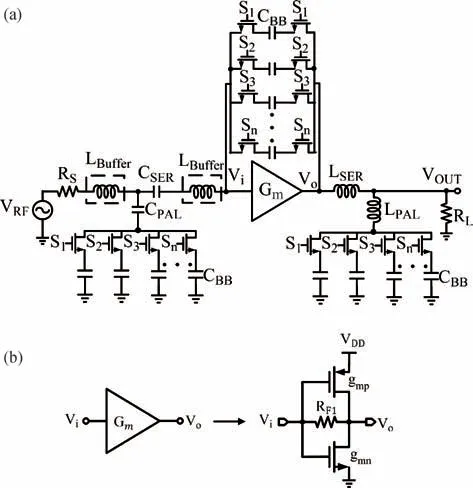

为了改善有源滤波器的带外抑制,本文在有源滤波器的通带两侧各引入一个传输零点,设计了一款高增益高带外抑制型N通道带通滤波器,其结构如图2(a)所示,由电容耦合N通道网络、电感耦合N通道网络、带有米勒反馈网络的跨导放大器、时钟发生器四部分构成。该带通滤波器在有源滤波器的基础上引入了电容(CPAL)耦合和电感(LPAL)耦合的N通道网络,在滤波器的通带两侧创建陷波,从而提高通带附近的带外抑制性能,抑制通带附近的强干扰。带通滤波器的NMOS 开关管宽长比(W/L)设置为25 μm/40 nm,由频率为fs、占空比为25%的4 相时钟发生器控制。为了防止电容器之间的瞬时电荷共享,在放大器的输入端串联了两个缓冲电感(LBuffer)。图2(b)为跨导放大器的内部结构图,由一个反相器和偏置电阻RF1构成,为带通滤波器提供增益。

图2 (a)完整的带通滤波器结构;(b)跨导放大器的内部结构Fig.2 (a) Complete band-pass filter structure;(b) Internal structure of trans-conductance amplifier

1.2 传输零点引入技术

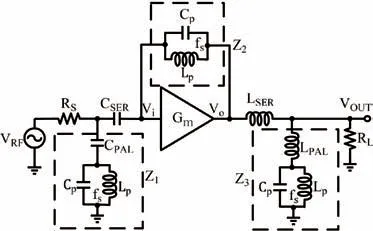

为了便于分析,用LC 谐振网络等效替换图2(a)中的N通道网络,得到图3 所示简化的带通滤波器结构图。

图3 简化的带通滤波器结构Fig.3 Simplified band-pass filter structure

由文献[10]可知,LC 谐振网络与N通道网络的等效转换关系式为:

式中:LP、CP分别表示等效后的LC 谐振网络的电感、电容;CBB表示N通道网络的基带电容;fs表示N通道网络的中心频率。

引入的两个传输零点为:

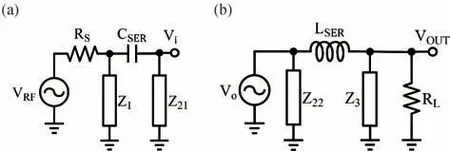

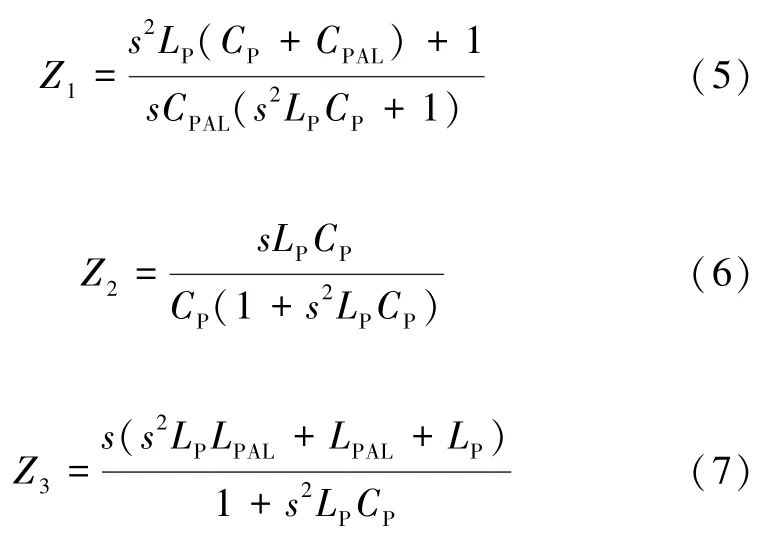

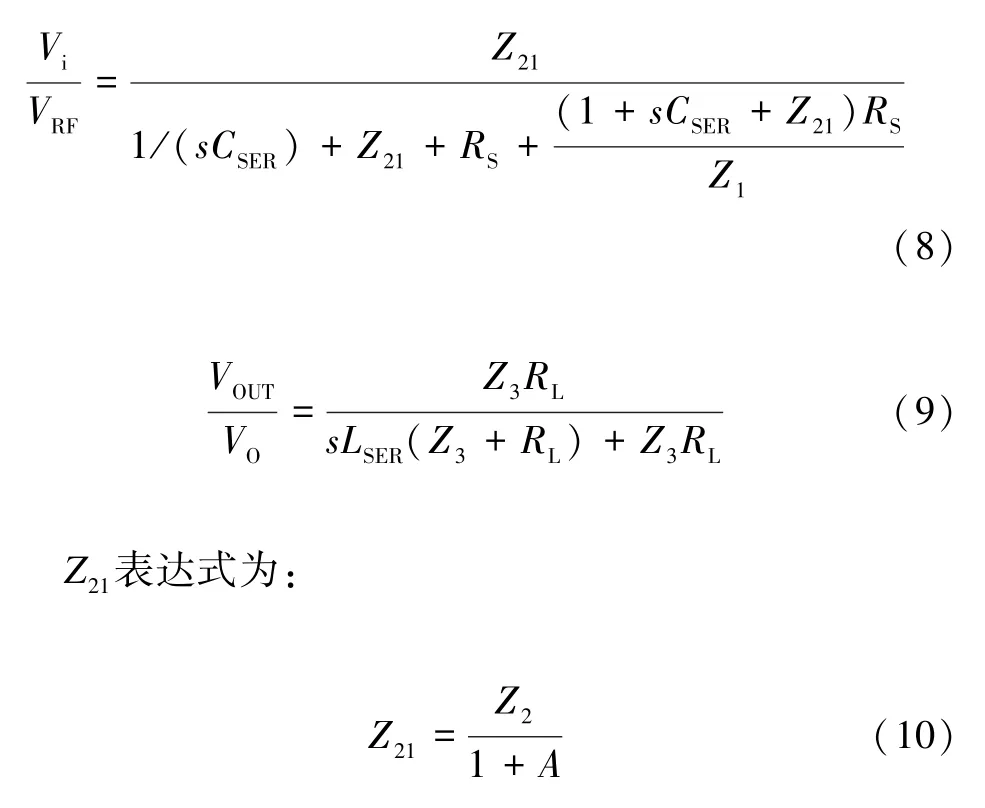

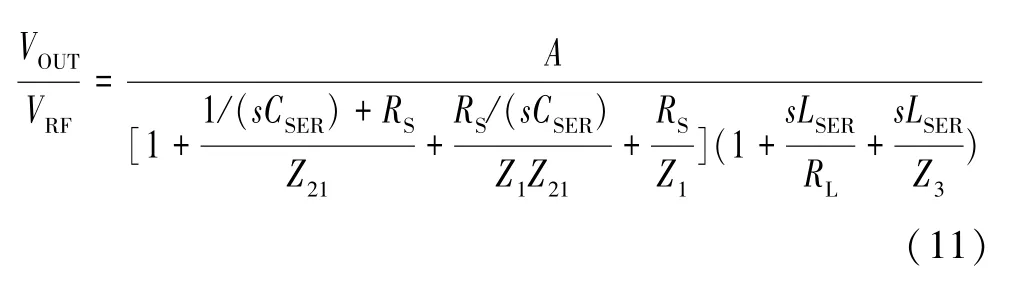

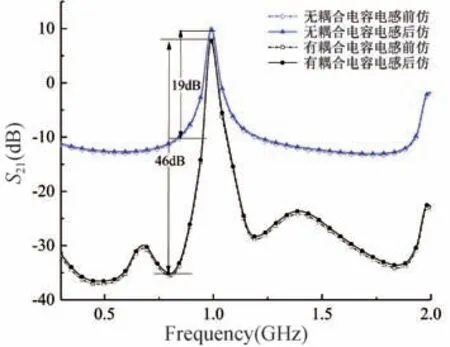

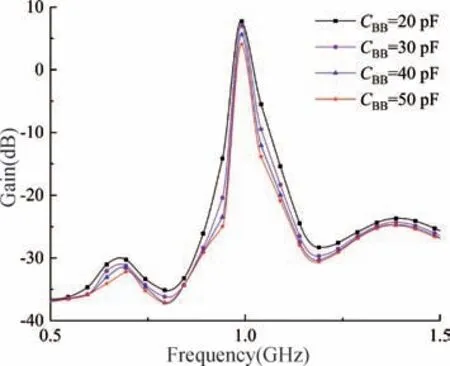

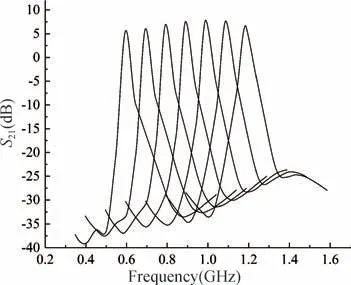

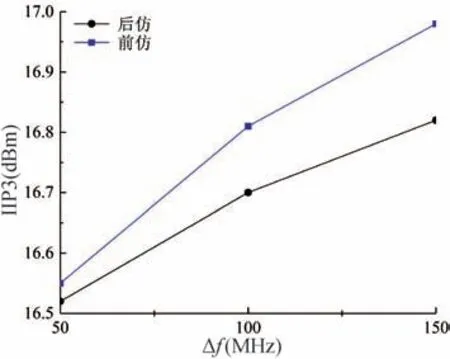

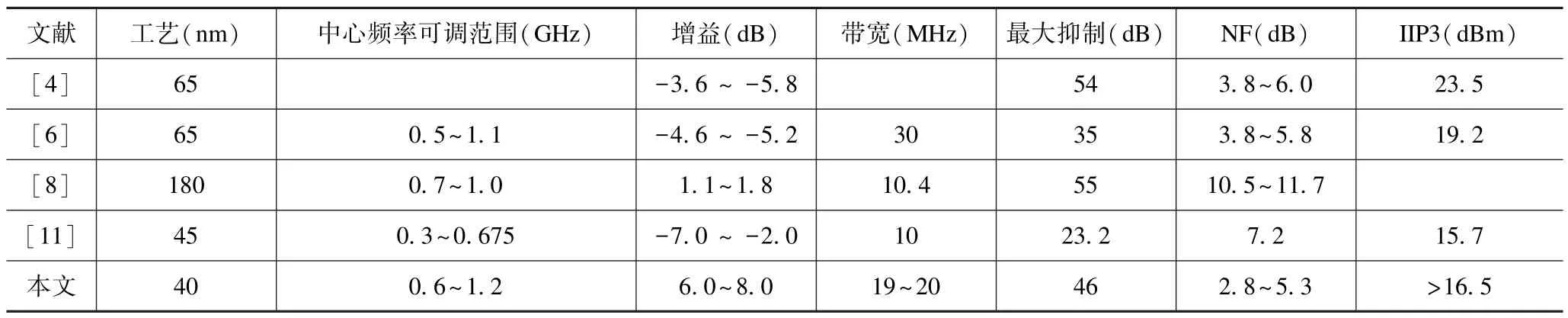

式中:Ceq=CP+CPAL;Leq=LPALLP/(LP+LPAL)。且有fL-TZ 为进一步简化分析,在图3 中,用Z1表示电容耦合LC 谐振网络的阻抗,Z2表示反馈LC 谐振网络的阻抗,Z3表示电感耦合LC 谐振网络的阻抗,并应用米勒定理[11-13],可将图3 的整体电路结构简化为图4(a)和(b)两部分。其中,图4(a)表示跨导放大器输入端Vi左侧的等效电路,图4(b)表示跨导放大器输出端Vo右侧的等效电路。 图4 (a)Gm输入端Vi左侧的等效电路;(b)Gm输出端Vo右侧的等效电路Fig.4 (a) The equivalent circuit on the left side of Gm input terminal Vi;(b) The equivalent circuit on the right side of Gm output terminal Vo Z1、Z2、Z3的表达式为: 图4(a)和(b)的传递函数表达式为: 式中:RS表示源电阻;RL表示负载电阻;A表示跨导放大器的放大倍数。 由式(8)~(10)可知,该带通滤波器的总传输函数表达式为: 式(11)表明,带通滤波器增益主要由跨导放大器的放大倍数A和阻抗Z1、Z21、Z3确定。放大倍数A和阻抗Z1、Z21、Z3值越大(基带电容CBB越小),增益越大,但考虑到噪声、线性度等综合性能,放大倍数与阻抗值不能过大。 取带通滤波器的通道数N=4,控制NMOS 开关管的时钟发生器的电路结构如图5 所示,用于产生4 个频率为fs、占空比为25%的非重叠时钟信号。带通滤波器中的每个开关(由NMOS 管实现)均已确定可接通。 图5 时钟发生电路Fig.5 Clock generation circuit 为了验证理论分析设计的正确性,在Cadence Spectre RF 环境、TSMC 40 nm CMOS 工艺前仿的基础上,对带通滤波器的性能进行了后仿。带通滤波器的版图如图6 所示。为了提高带通滤波器的性能,采取对称的版图布局布线,减小寄生电容和电阻对电路性能产生的影响。取通道数N=4,采用宽长比(W/L)为25 μm/40 nm 的NMOS 管作为开关,开关由频率为fs、占空比为25%的4 相时钟发生器驱动。 图6 带通滤波器的版图Fig.6 Layout of the band-pass filter 当中心频率fs=1 GHz 时,带通滤波器的频率特性如图7 所示。由图7 可见,与前仿相比,后仿的S21略低,且前仿和后仿的结果均表明,引入耦合电容CPAL和电感LPAL后,带外抑制有了很大改善。以后仿结果为例,引入耦合电容和电感后,最大带外抑制由19 dB 提高到了46 dB。 图7 带通滤波器的频率特性曲线(fs=1 GHz)Fig.7 Frequency characteristic curves of the band-pass fiter(fs=1 GHz) 为了验证基带电容对增益的影响,当跨导放大器放大倍数A保持不变、中心频率fs=1 GHz 时,不同基带电容CBB的带通滤波器增益仿真(后仿)结果如图8所示。结果表明:基带电容越小,带通滤波器的增益越大。但考虑到寄生电容的存在,CBB不能太小。综合考虑,设置带通滤波器的CBB=20 pF。 图8 不同电容值对应的带通滤波器增益曲线(fs=1 GHz)Fig.8 Gain curves of the band-pass filter corresponding to different capacitance values (fs=1 GHz) 图9 为带通滤波器正常工作时中心频率fs的可调谐范围的仿真(后仿)结果。由图可知,带通滤波器正常工作时,中心频率fs可调谐范围为0.6~1.2 GHz,且在该范围内,带通滤波器的增益范围为6.0~8.0 dB,这也表明带通滤波器具有良好的增益提高性能。 图9 带通滤波器中心频率可调谐范围Fig.9 Tunable range of the band-pass filter center frequency 带通滤波器的噪声系数(NF)仿真结果如图10 所示。由图可见,在中心频率调谐范围内,噪声系数(NF)为2.8~5.3 dB(后仿),表明带通滤波器具有良好的噪声抑制性能。 图10 带通滤波器的噪声系数(NF)Fig.10 Noise figure (NF) of the band-pass filter 图11 为中心频率fs=1 GHz 时,带通滤波器输入三阶交调点(IIP3)的仿真结果。由图可知,带通滤波器输入三阶交调点(IIP3)大于16.5 dBm(后仿),表明带通滤波器具有良好的稳定性。 图11 带通滤波器的IIP3Fig.11 IIP3 of the band-pass filter 表1 列出了本文提出的设计与其他类似工作的比较。从表1 可以看出,本文带通滤波器的优势表现在:最大带外抑制较大,增益较高,且综合性能也较高。 表1 与其他文献带通滤波器的性能比较Tab.1 Performance comparison of band-pass filters with other literatures 本文设计了一款带有传输零点的增益提高型N通道带通滤波器,在有源滤波器的输入端引入电容耦合N通道网络,输出端引入电感耦合N通道网络,以提高通带两侧的带外抑制能力,抑制通带附近的强干扰。带通滤波器采用TSMC 40 nm CMOS 工艺设计,应用Cadence Spectre RF 软件完成仿真验证。验证结果表明:当电源电压为1.1 V 时,带通滤波器的中心频率fs可调谐范围为0.6~1.2 GHz,增益值为6.0~8.0 dB,带宽为19~20 MHz,噪声系数为2.8~5.3 dB,当fs=1 GHz 时,带通滤波器通带两侧的最大抑制为46 dB。与其他类似滤波器相比,本文所提出的带通滤波器不仅增益获得了改善,并且具有带外抑制能力强的优点,可应用于射频接收机前端。1.3 增益提高技术

1.4 时钟发生电路

2 电路仿真与分析

3 结论