一种基于FPGA的4K HDMI转eDP视频接口的设计

2021-09-08谢绪煜

谢绪煜,龙 彬,周 军,胡 彬

(长沙湘计海盾科技有限公司,湖南 长沙 410100)

0 引 言

现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)技术以其可靠性高、速度快及设计灵活的特点广泛应用于图像处理领域。目前在民用领域,液晶显示器或者4K电视机厂商常用驱动4K eDP接口液晶面板的方案,主要是基于晨星MSTAR或者Realtek、国内海思及瑞芯微等图像处理芯片设计的,而该方案灵活性较低,如需要增加新的视频图像接口或者改变某一项图像处理功能较为困难。例如,在主显示屏幕eDP显示画面基础上再增加一个副屏幕eDP环出显示或者VGA环出显示不一样的分辨率图像就不能用上述方案来实现,局限性较大,且该方案视频接口切换画面显示较慢,多达10 s钟的时间才能完成画面切换,无法做到无缝切换[1-4]。针对上述情况,介绍一种基于FPGA将4K HDMI视频信号转为eDP接口信号的方法。

1 系统总体设计

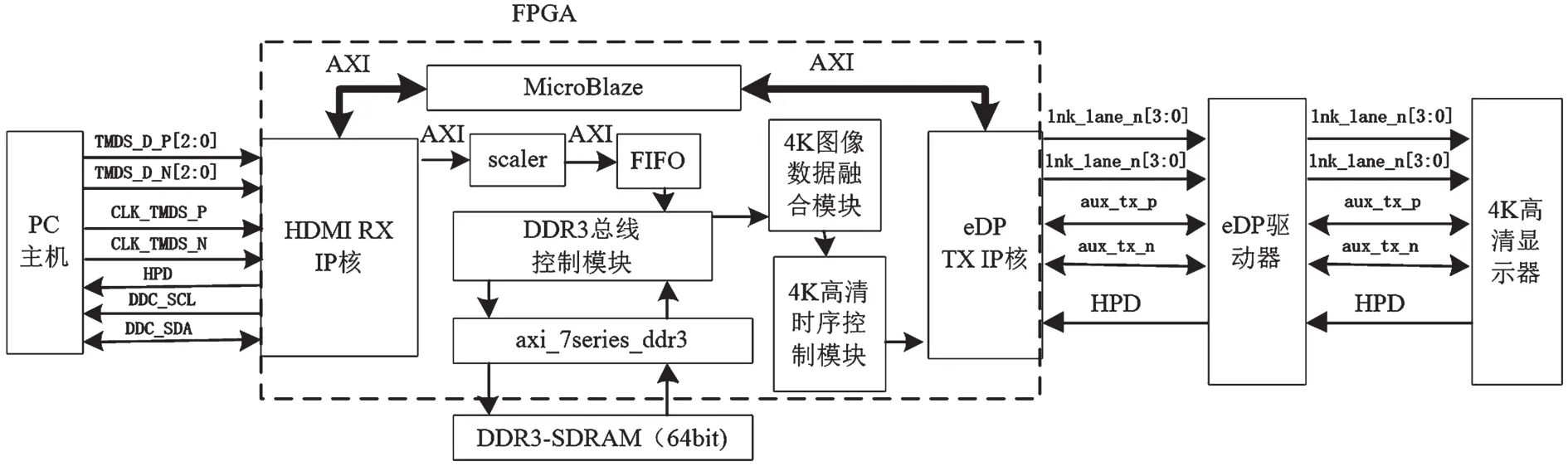

根据设计要求,本系统利用高速FPGA将HDMI视频信号通过图像处理后转为eDP的接口信号。系统中的FPGA内部采用模块化设计思路,例化的模块包括HDMI RX模块、MicroBlaze软核模块、scaler缩放模块、FIFO模块、DDR3总线控制模块、DDR3的IP核模块、4K图像数据融合模块、4K高清时序控制模块以及eDP TX模块。其中,HDMI RX模块从PC主机接收视频图像,对4K HDMI信号进行解码,并将HDMI视频图像转换为通用的图像数据处理RGB格式;scaler缩放模块采用双线性插值算法将分辨率低于3 840*2 160的RGB格式的视频图像分辨率放大至4K,缩放后的图像数据用高速FIFO模块保存;FIFO模块的保存数据达到预设像素点数量时,按行将当前保存的像素点写入DDR3 SDRAM;4K图像数据融合模块采用乒乓操作方式从DDR3 SDRAM中读取图像数据进行预处理,包括对比度调节、亮度调节及图像降噪处理;处理完成后由4K高清时序控制模块转换为eDP信号,最终由eDP TX硬件接口发送至4K高清显示器显示。本设计可使4K高清液晶显示器的显示速度加快,系统总体框图如图1所示。

图1 实现4K HDMI视频转eDP视频接口原理框图

本设计中采用的高速FPGA为美国Xilinx公司的生产的kinetx-7系列XC7K325T-2FFG900I,该系列FPGA采用28 nm工艺生产,内部含有丰富的逻辑资源,包括高速GTX接口、DDR3高速接口等,可以满足4K的高速图像处理要求。eDP驱动器采用SN65DP159RZ芯片来增强其传输数据的能力,以适应高速数据长线传输要求,避免数据时钟抖动现象[5-6]。

2 系统硬件设计

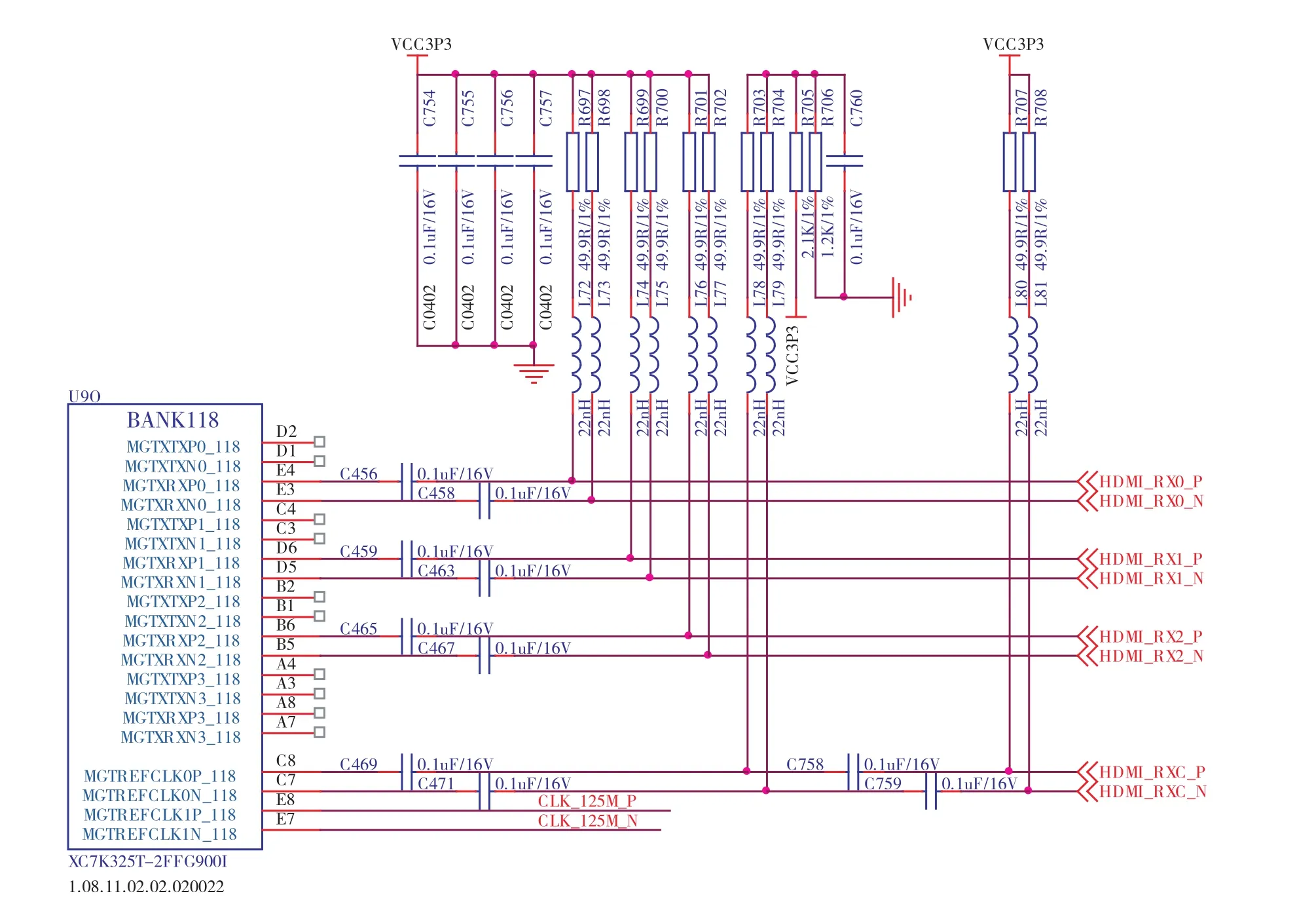

HDMI RX硬件接口与PC主机通过HDMI线缆连接,HDMI RX硬件接口由FPGA内部的MicroBlaze软核模块控制,从PC主机接收HDMI视频图像数据并做处理。在本设计中,PC电脑主机应能输出分辨率为3 840*2 160的4K HDMI视频图像,若PC主机不能输出4K图像分辨率,也可以通过缩放模块将其放大为4K图像信号。为了改善信号的传输质量,在HDMI RX模块的HDMI RX硬件接口的前端增加了视频图像信号调理电路,具体的信号调理电路如图2所示,PC主机与HDMI RX硬件接口之间上拉串联的50 Ω电阻和20 nH电感,然后在上拉点与HDMI RX硬件接口之间设置0.1 uF电容。通过该信号调理电路对PC主机传输的HDMI视频图像数据进行抗干扰处理,从而使HDMI RX模块接收到的HDMI视频图像数据质量更高,避免出现闪屏和信号出现噪点的现象。HDMI接口的EDID信息保存在硬件电路的EEPROM芯片中,EEPROM 芯片选用24LC02B。当PC主机检测到HDMI热插拔HPD信号后,通过IIC管脚的SCL和SDA管脚读取EDID信息,以确定其输出的图像分辨率大小。

图2 HDMI信号调理与FPGA GTX连接硬件电路图

3 系统程序设计

3.1 HDMI图像数据流处理设计

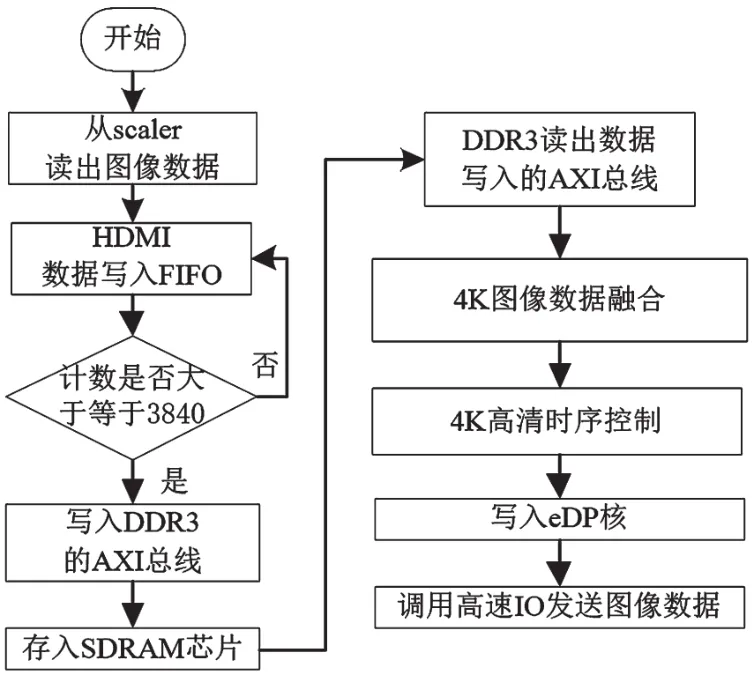

HDMI RX模块从PC主机接收到的HDMI信号包括像素时钟hdmi_clk、像素点有效指示信号hdmi_de、行同步信号hdmi_hsync、场同步信号hdmi_vsync以及像素点24 bit的hdmi_rgb[23:0]数据;对于分辨率为3 840*2 160的视频图像无需进行缩放处理,对于分辨率小于3 840*2 160的图像进行scaler模块放大成3 840*2 160的分辨率;缩放后的数据存入FIFO模块,由于DDR3程序存入图像按行存储,因此当FIFO模块的数据计数值fifo_data_count计到大小为3 840个像素点的时候,表明一行图像数据已经缓存完毕。逻辑模块调用FPGA内部的DDR3 IP核模块,将一行大小为3 840的像素点数据写入DDR3 SDRAM存储芯片中。4K图像数据融合模块读取DDR3 SDRAM中的图像数据并经过图像增强、去噪等处理之后发送至4K高清时序控制模块,4K高清时序控制模块将数据写入eDP TX IP核,最终调用eDP TX模块内部的高速接口将图像数据发送到高清显示器,FPGA内部的数据处理流程如图3所示。

图3 FPGA内部图像数据处理流程图

DDR3模块读写视频图像数据采用AXI总线控制方式。AXI总线控制方式具有读写速度快、操作规范的特点。该设计中,DDR3 IP核设置的工作主频为667 MHz而没有设置成800 MHz,目的是为了降低功耗及增加可靠性。AXI_Data_Width的位宽设置为512 bit,经过计算得出一共需要4片16 bit数据位的DDR3 SDRAM组合才能满足数据流带宽要求,AXI总线为512 bit的数据位宽需要16个hdmi_rgb[23:0]像素点来拼接,拼接的原则为:先到达的像素点存于低位,晚到的像素点存于高位。1行3 840个像素点的数据可以拼接成240个512 bit的AXI总线数据,数据拼接原理如图4所示。

图4 数据拼接原理图

3.2 双线性插值算法模块设计

双线性插值算法广泛应用于显示器图像处理领域,可以将图像的分辨率放大来适应显示屏的显示要求,核心思想是在相邻的上下左右4个像素点插入1个像素点,其计算方法为:

式中:f(i+u,j+v)可由原图像中4个像素坐标为(i,j)、(i+1,j)、(i,j+1)、(i+1,j+1)所 对应的像素值决定;u、v为浮点坐标的小数部分,通过计算得到,取值范围为[0,1)区间的浮点数。

scaler缩放模块采用双线性插值算法实现,其功能是将任意分辨率的输入图像转变为4K图像,实现图像插值放大。

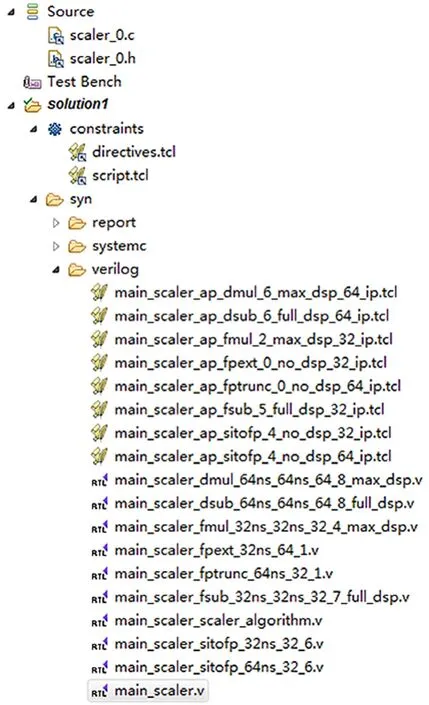

双线性插值模块用vivado HLS软件进行开发设计。vivado HLS工具可以将C语言高级综合为硬件,极大地节约了设计人员的开发时间。HLS软件部分代码如下所示,生成的verilog硬件代码如图5所示。

图5 HLS生成的verilog硬件代码图

for(col=1;col<=destW;col++){

srcCol=((float)col)*colRatio;

k=(unsigned int)(srcCol);

u=srcCol-k;

coffiecent0=(1.0-t)*(1.0-u);

coffiecent1=(1.0-t)*u;

coffiecent2=(t)*(1.0-u);

coffiecent3=t*u;

src_pixlel_coor1=getClip(k,srcW,1);

src_pixlel_coor3=getClip((k+1),srcW,1);

}

3.3 eDP发送4K高清图像数据程序设计

eDP是一种低电压摆幅的差分信号技术,它使得信号能在长距离的差分PCB线对或平衡线缆上以几百兆赫兹的速率传输,视频数据通过eDP接口标准传输时有特定的数据格式。本设计中,eDP协议包含在eDP IP核中,因此要实现eDP接口发送4K高清视频数据功能,需使用官方推荐的eDP IP核,该IP核中有一些参数如链路速度、带宽及数据位宽等需要C语言软件配置才能更好管理及使用。由于需要配置eDP IP核的参数较多,为了降低配置管理的难度,本文调用了FPGA自带的MicroBlaze软核对eDP IP硬核参数进行配置。MicroBlaze软核具有嵌入式软件管理功能,MicroBlaze核与eDP TX IP硬核的例化模块如图6所示。lnk_clk_p和lnk_clk_n分别为eDP IP核差分输入时钟的正负端口,此处设置输入的时钟频率为135 MHz;lnk_tx_lane_p[3:0]和lnk_tx_lane_n[3:0]分别为eDP IP核传输的差分数据的正负端口,若要传输4K的分辨率要同时调用4对lnk_tx_lane;tx_hpd为PC主机检测的热插拔信号;aux_tx_io_p和aux_tx_io_n分别为eDP辅助信号通道,用来与显示器的TCON板之间的信号握手和EDID信息读取。

图6 例化的eDP模块图

4K高清时序控制模块根据自身产生的有关eDP模块的控制时序,将数据预处理得到的4K视频图像数据转换为eDP信号,进而将eDP信号写入eDP TX模块。MicroBlaze软核模块控制eDP TX模块,使eDP TX模块通过eDP TX硬件接口将视频图像数据至4K高清显示器。MicroBlaze软核模块控制eDP TX硬核模块的软件控制流程如图7所示。首先初始化MicroBlaze软核模块与eDP TX模块之间的AXI总线,接收来自4K高清显示器的EDID信息,通过接收链路信息选择对应的lane通道和link rate速度;eDP TX模块使用确定的lane通道并以确定的link rate速度,通过eDP TX硬件接口将视频图像数据至4K高清显示器。

图7 eDP软件处理流程图

在vivado开发软件生成的工程导出硬件eDP_wrapper.hdf文件后,利用SDK软件开发工具导入硬件eDP_wrapper.hdf文件配置信息;根据硬件信息生成软件工程,该软件工程包含BSP底层驱动,通过编写MicroBlaze软核C语言软件程序来控制eDP参数的配置与发送数据的过程管理,可以实现4K高清图像数据的发送[7]。

4 试验验证

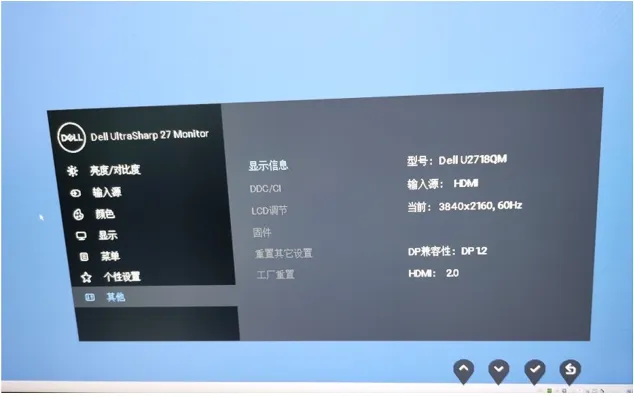

对基于FPGA的4K HDMI转eDP视频接口进行设计验证时,需要将PC主机视频显卡发送的分辨率为3 840*2 160的视频图像通过HDMI接口线缆连接到4K HDMI转eDP视频接口系统电路板,再从HDMI转eDP视频接口系统电路板用eDP线连接到4K高清显示器进行显示。测试结果如图8所示,在高清显示器上显示1路PC主机桌面图像,桌面上显示输入的分辨率信息为3 840*2 160,可见设计满足1路图像接收机显示要求[8]。

图8 分辨率为3 840*2 160的HDMI图像画面

5 结 语

试验结果表明,基于FPGA的4K HDMI转eDP视频接口系统能满足4K高清显示技术要求,具有显示速度快、可以无缝切换的特点,可以广泛应用于自主可控设计领域如军工或者航天等。本文研究对于高速4K高清显示器或者4K电视机的设计具有一定的参考意义。