AM5706通过VIP接口与FPGA图像数据传输实现

2021-08-28张海堂

张海堂

(广州中智融通金融科技有限公司,广东 广州 510663)

1 引言

随着国家大力推动政务信息化工作,智能政务自助服务终端机成为了政务大厅的一种新型设备,终端机集成了政务信息化系统的软件服务模块,为办事群众提供诸如身份证认证、资料采集、资料回执打印等服务。票据图像扫描模块是终端机的一个关键模块,它采用CIS(Contact Image Sensor)接触式图像传感器,相比高拍仪有更高的鉴伪能力可保证扫描件的真实性,用于扩展服务内容和范围、提升服务质量[1]。

票据图像扫描模块传统实现方法一般是采用DSP+FPGA的技术平台,模块采集两级CIS图像传感器信号,经模数转换后送入FPGA 进行灰度值补偿预处理,FPGA 积累到完整一行图像数据后,触发一次DSP 中断接收,然后DSP 中断触发EDMA模式通过EMIF并口总线从FPGA读取一行图像数据。该方法每次只能接收一行图像数据,存在CPU触发中断次数多和资源使用率高的缺点,一般在老一代图像处理平台例如DSP C6000系列有广泛应用,但在新一代图像处理平台例如AM5706已淘汰,取而代之的是VIP(Video Input Port)这种高效的图像数据传输接口。

本文介绍了一种AM5706通过VIP接口与FPGA实现图像数据传输的方法,AM5706 VIP 设备每接收到一幅完整的图像数据,才会触发一次CPU 中断,相比传统EMIF 并行总线+EMDA 方法的每次只能接收一行图像数据,采用VIP 接口传输图像数据可极大减少CPU中断次数、降低CPU资源使用率,这对提升系统性能和降低硬件成本都具有重要意义。

2 技术方案

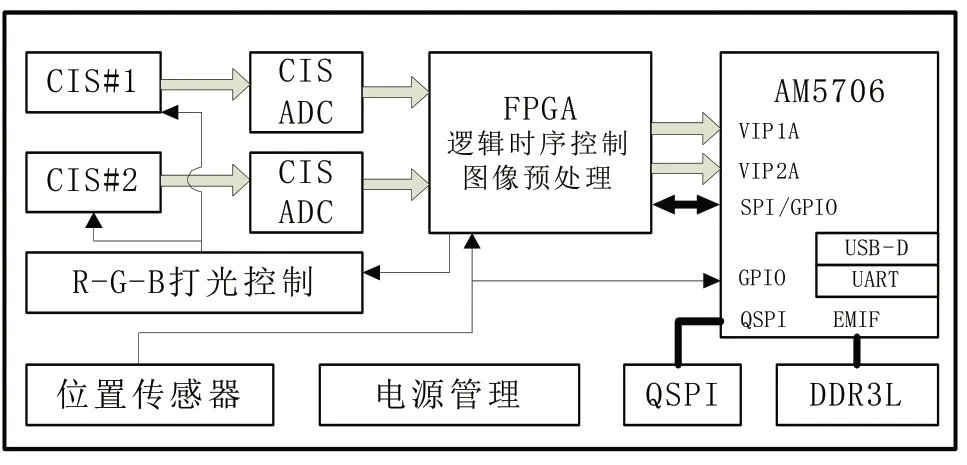

技术方案基于TI ARM+DSP 多核AM5706 和XILINX FPGA Spartan-6 XC6SLX25 平台,AM5706 作为为主处理器负责应用软件的功能实现,FPGA ARTIX-6 XC6SLX25 负责CIS 打光时序控制和图像数据预处理。技术方案总体框图如图1所示。

图1 技术方案总体框图

票据图像扫描模块可采集两个通道CIS 图像传感器的模拟信号,模拟信号送入专用ADC 进行模数转换后输出原始图像数据,然后原始图像数据送入FPGA进行图像灰度值补偿预处理,得到补偿后的图像数据,补偿后的图像数据以一个完整行为基本单位,最后送入AM5706的VIP接口(Video Input Port),AM5706 ARM内核驱动通过VIP 接口被动接收来自FPGA 的补偿后CIS 图像行数据,当积累到一幅完整的图像数据后,应用程序跳出阻塞状态并保存这一幅完整的图像数据,然后对该幅图像进行鉴别、OCR识别等操作,最后通过USB 2.0 Device 通信接口把识别结果和图像数据上传到上位机。

AM5706 VIP 接口是一个从设备,在FPGA 连续发送图像数据行到AM5706的VIP接口过程中,DMA会自动接收数据放入事先配置好的图像缓冲区中,完全无需中断ARM 的当前任务,传输效率明显要高于传统的DSP图像处理平台。

3 硬件设计实现

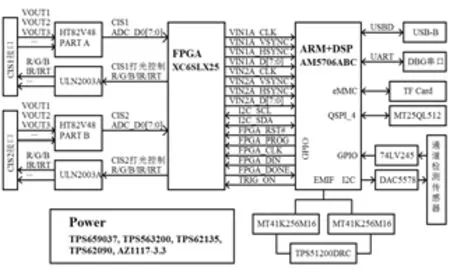

硬件电路采用TI ARM+DSP 多核AM5706 和XILINX Spartan-6 XC6SLX25 作为主芯片。AM5706 外接64MB QSPI FLASH 和512MB DDR3L SDRAM 的 运 行 内 存,QSPI FLASH 用来存放ARM Linux 系统镜像、ARM 应用程序、FPGA介质程序、灰度值补偿参数和运行日志,DDR3L SDRAM是ARM 的运行内存,上电后ARM Linux 系统镜像、ARM 应用程序会搬送到DDR然后运行。AM5706采用GPIO时序模拟来实现FPGA 程序的加载,采用I2C 来配置FPGA 工作参数。电路设计了一路USB 2.0 Device,实现和上位机的通信和图像数据上传[3,4]。

硬件电路设计有两路CIS 输入,每路CIS 支持R、G、B、IRF 光色。两路CIS 采集使用一片CIS 专业ADC 芯片HT82V48进行采集,LED打光控制由FPGA输出控制信号驱动ULN2003A 进行电流放大。CIS 光色模拟信号经过HT82V48模数转换后输出2路8-bit数字信号,数字信号输入FPGA 进行图像缓冲和灰度补偿,最后输出到AM5706 的VIP外设接口[2]。

图2 硬件电路框图

图3 VIP接口电路

4 软件设计实现

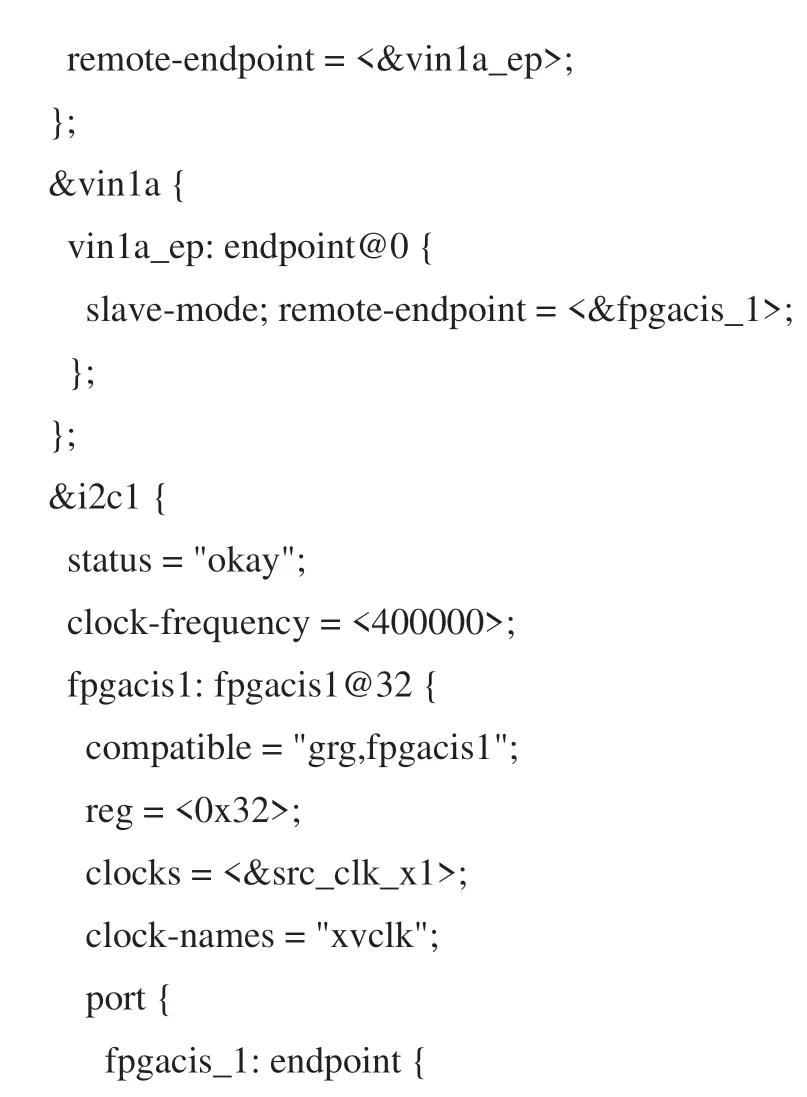

软件实现首先编写ARM 端的设备驱动FPGACIS,设备驱动开发可参考SDK 目录/kernel/drivers/media/i2c/下面的CMOS 驱动源代码和具体实现思路[4,5],本设计设备驱动FPGACIS描述符为“fpgacis”,设定输入分辨率800*480,输入格式SBGGR8,8-bit数据宽度,设备树设备节点compatible属性“grg,fpgacis1”,摘取关键代码如下:

然后对VIP 相关DTS 设备树字段进行配置,需要打开vip1,然后把设备fpgacis_1 挂载在i2c 总线下面,并与端点vin1a_ep建立连接[4,5],摘取关键配置如下:

FPGACIS 设备驱动完成配置和挂载成功后,Linux 系统便会产生设备节点如/dev/video0、/dev/video1,编写应用程序通过V4L2 接口采集视频数据,因篇幅原因不详细列举应用程序的源代码,具体实现过程参考软件流程图,如图4所示。

图4 软件流程图

5 系统实现效果

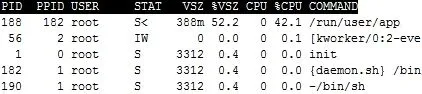

硬件上电正常后进入Linux系统后,先挂载FPGACIS设备驱动,Linux 系统会产生设备节点如/dev/video0、/dev/video1,然后运行应用程序/run/user/app,app 首先读取在rootfs存放的FPGA firmware,通过GPIO时序模拟下载到FPGA然后启动FPGA,下一步继续完成对FPGA的采集参数配置,驱动通道步进电机,就可以实现对多张票据的连续图像采集了。样张采集的图像效果如图5所示,使用大批量样张进行压力测试,图像采集稳定,未出现卡顿、图像丢失、图像缺行,图像亮线等异常现象。在设定最大采集速度下连续采集样张图像,CPU资源使用率稳定在42%左右,如图6所示,相比老一代图像处理平台的CPU资源使用率得到明显下降。

图5 采集样张图像

图6 连续模式下资源使用率

6 结语

本文介绍了一种AM5706 通过VIP 接口与FPGA 图像数据传输的实现方法,该方法是票据图像扫描模块的一个关键技术,票据图像扫描模块可采集两级CIS 图像传感器信号,经模数转换后送入FPGA进行灰度值补偿预处理,FPGA积累完整一行图像数据后,输出到AM5706的VIP接口,实现方法主要技术难点有:硬件电路图设计和PCB设计,ARM内核Linux 系统下VIP 设备驱动和配置,ARM 应用程序开发,FPGA VIP接口时序实现和图像预处理程序编写。本文详细介绍了模块的硬件电路设计、ARM内核Linux系统下的VIP设备驱动编写和配置,以及应用程序从FPGA 接收CIS 图像数据的实现方法。采用VIP 接口传输大分辨率图像数据以整张图像为单位,相比传统DSP 平台采用的EMIF 并行总线+EDMA 的图像传输传输方法,可极大减少CPU 中断次数,通过实测数据证实了较低的CPU资源使用率,该平台和数据传输方法在票据图像扫描模块产品中应用,实现了提升性能和降低硬件成本的设计目标。