FPGA 配置用FLASH 型PROM 数据失效分析及防护措施

2021-08-23段红亮张雪峰张欣光杨薇秀

刘 浩,段红亮,张雪峰,张欣光,杨薇秀

(北京航天长征飞行器研究所,北京,100076)

0 引 言

SRAM 型FPGA 需要通过加载配置文件比特流至内部存储器完成初始化配置过程。所谓的初始化配置技术,是一种FPGA 在上电后,外围设备(比如配置芯片)开始加载全比特流文件对其内部的全部逻辑资源进行第1 次配置,以实现系统的初始功能[1]。

由于SRAM 型FPGA 的配置存储器是易失型的,每次上电需要重新配置,因此必须外接存储了配置文件的非遗失存储器,通过配置接口完成配置文件比特流加载。较为常用的非遗失性配置文件存储器为FLASH 型PROM(Programmable Read Only Memory),其采用了低功耗先进的COMS NOR FLASH 工艺,可重复擦除或编程达20 000 次,支持IEEE 1149.1 和IEEE 1532 标准边界扫描(JTAG)协议[2]。以Xilinx SRAM型FPGA 为例,其通常的使用过程为:a)设计好软件工程,经过综合及布局布线等过程后生成比特型配置文件;b)根据配置存储器类型转化配置文件;c)通过JTAG 将配置文件烧写至配置存储器中;d)系统整机上电后FPGA 加载配置存储器中的配置文件并开启工作模式。

如果配置存储器内数据异常,则会导致FPGA 无法配置成功,软件无法运行,系统整机表现为失效状态,电流比正常状态偏低。本文针对一起国产FLASH型PROM 数据失效导致FPGA 无法正常配置的案例,对问题机理进行分析后,给出系统层防护措施。本系统选用Xilinx Virtex-4 FPGA 及国产某款配置PROM,此款PROM 可原位替代Xilinx XCFxxP 系列相应产品。

1 案例描述

在系统进行60 ℃高温老练试验的某一循环上电启动时出现系统整机失效现象,且系统上电后工作电流偏小,进一步排查发现系统主处理器FPGA 软件未正常加载成功,因此软件未运行。对系统重新断电上电后,故障依旧,恢复常温后故障仍然无法消除。即加电后系统再也无法正常启动。后在上电情况下通过JTAG 在线调试方式向FPGA 加载程序,系统恢复正常且所有功能运行正确,因此排除FPGA 本身及外围供电及其他电路异常情况。重新通过JTAG 接口向PROM烧写配置文件后系统恢复正常,因此确定为PROM 出现异常情况导致上述问题。此PROM 为某型国产FLASH 型FPGA 芯片,其作为Xilinx Virtex-4 FPGA的配置芯片存储FPGA 的配置文件。配置模式采用主并模式[3],配置电路见图1 所示。

图1 FPGA 配置电路Fig.1 FPGA Configuration Circuit

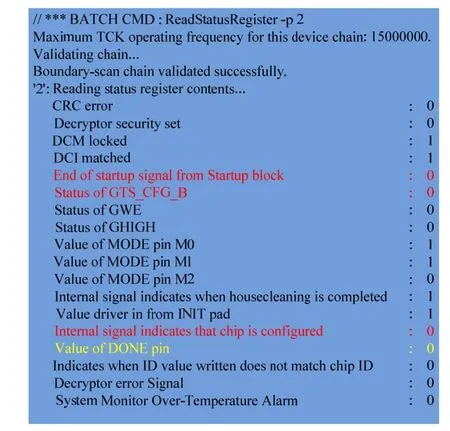

通过JTAG 接口读取异常情况下FPGA 的状态寄存器信息,读取结果如图2 所示。由图2 可见“Value of DONE pin”已置低,FPGA 已做好读取PROM 信息准备,而“Internal signal indicates that chip is configured”等信息表明FPGA 未收到或接收到错误的PROM 配置信息。通过示波器测试PROM 端CLK、/CE 及OE 端波形发现波形输出均正常,进一步排除FPGA 异常可能。

图2 FPGA 配置失败时状态寄存器信息Fig.2 Status Register Information When Configuration Fails

2 失效因素分析

此款FLASH 型PROM 原理如图3 所示,其中“JTAG 接口控制”电路及“存储单元”为其核心部件。根据故障现象推断该PROM“存储单元”数据异常因有2 种可能:a)“存储单元”数据保持能力失效;b)“JTAG 接口控制”电路异常擦写“存储单元”[4]。

图3 PROM 原理Fig.3 PROM Schematic

2.1 工艺及环境因素

“存储单元”由FLASH 闪存存储单元组成,单元内的数据在一段时间内被正确读取的能力,也称为FLASH 数据保持能力。其受到诸多因素影响,包括工艺制造、温度和电压、静电环境、辐射暴露、累积擦除周期等。常见的致数据保持能力失效的具体模式包括:

a)工艺制造缺陷导致存在浮栅电子泄漏的存储单元,通常被称为单位电荷损伤单元,表现为低于典型的数据保持能力[5]。同时浮栅电子泄漏可以在电压或高温应力的作用下被进一歩加速。所有的芯片供应商都有标准的过程来描述和识別有工艺缺陷的存储单元。

b)使用环境造成的伪单位电荷损伤单元。这类单元在物理上是合格的存储位,只是被轻微地编程,即“欠编程”,无法100%识别。通常是由于编程操作过程中出现了系统噪声或瞬变电压导致无法达到完全编程存储单元所需的阈值电压。在执行读操作时,一个“欠编程”的位可以读取为“0”或“1”。

在第1 种失效模式下,单位电荷损伤单元会导致PROM 中存储的数据为不可逆的错误配置文件,FPGA读取此配置文件将始终无法正常启动。在第2 种失效模式下,伪单位电荷损伤单元导致PROM 中存储的数据为可逆的配置文件,在不同测试工况下FPGA 应有配置成功概率。两种失效模式均与本系统故障模式不同。同时,进一步测试故障模式下D[0..7]数据端波形,并与正常模式下数据比对后发现故障产品PROM 数据内容错误。PROM 输出异常数据D0 与CLK 波形如图4 所示,正常数据D0 与CLK 波形见图5 所示。如果存储单元是一个被写入过的,相当于逻辑“0”,相反,如果这个存储单元是被擦除过的,相当于逻辑“1”[7]。经过测试排故后认为故障原因为FPGA 配置用FLASH型PROM 内部分数据被异常由“1”改写为“0”,且现象稳定。同时可排除因“存储单元”数据保持能力失效和被擦除导致故障。

图4 PROM 异常数据输出波形Fig.4 PROM Wrong Data Output Waveform

图5 PROM 正常数据输出波形Fig.5 PROM Correct Data Output Waveform

2.2 控制状态机因素

JTAG 接口控制电路主要包括:上电初始化电路、读存储单元电路及写存储单元电路3 部分。与PROM内部分数据被异常由“1”改写为“0”有关的部分为前两种电路。

写存储单元电路工作流程为:通过JTAG 接口将配置文件以数据位流依次按照地址顺序和数据映射关系写入到PROM 存储单元组成的阵列空间。故障出现过程没有此操作流程,可以排除,重点针对“上电初始化”电路异常进行排查。

上电复位电路工作原理为:上电复位电压阈值应高于器件最低工作电压。在上电过程中,电压在抵达最低工作电压和复位阈值电压前保持器件复位状态,直至到达复位阈值电压后复位解除,以此保证上电过程中器件初始状态受控。如果上电复位阈值低于最低工作电压,将导致器件复位解除后还未到达最低工作电压,器件状态不受控,存在错误进入“写数据状态机”或“擦数据状态机”过程的可能。

状态机被异常触发后,可能不处于正常的复位或空闲的状态,出现错误跳转,导致误写入等异常情况。“写数据状态机”单次进入写状态,根据JTAG 接口指令设计最多可向PROM编程并写入32Byte数据;“擦数据状态机”单次进入擦状态,根据JTAG 接口指令设计单次擦除256Byte 的整数倍数据。目前PROM 错误数据表现为“1”变“0”,是错误进入“写数据状态机”现象。

此款FLASH 型PROM 为国内某厂家参考Xilinx XCFxxP 系列同款产品设计,上电复位电压阈值设计值为2.0 V。上电复位电路在工艺制造上存在上电复位电压阈值过低的可能。同时,上电复位阈值电压在工艺特性上随温度上升会进一步下降,对于与故障产品同批次的一只库存合格产品实测在不同温度下上电复位电压如表1 所示。

表1 不同温度下上电复位阈值实测值Tab.1 Power-on Reset Threshold Measured Value

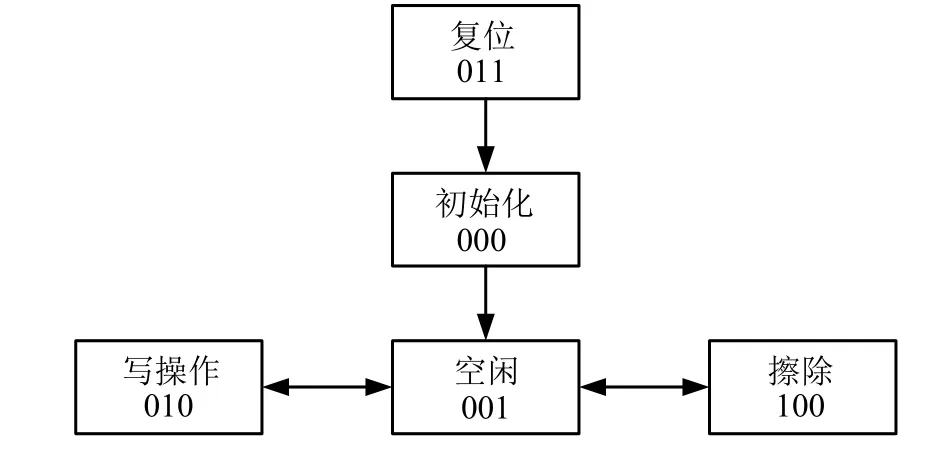

对于上电复位电压阈值远低于设计值2.0 V 的个例,当其随温度上升使得上电复位阈值低于寄存器锁存数据的最低工作电压1.5 V 时,将使得初始化电路中PROM 控制状态机在上电过程中存在一段时间的不确定状态。PROM 控制状态机以40 MHz OSC 时钟作为工作时钟,在RTL 代码中为独热码编码,经综合工具综合时自动进行状态机重构优化后,在网表中被优化为二进制编码,如图6 所示。

图6 PROM 控制状态机Fig.6 PROM Control State Machin Diagram

由图6 可知,PROM 控制状态机在网表中使用三比特寄存器表示当前状态。当处于上电复位时,状态机处于复位状态011;当上电复位结束时,状态机正常跳转至初始化状态000,开始进行OSC 修调等初始化操作。当初始化状态执行完成后,状态机进一步跳转至空闲状态001,等待响应来自JTAG 接口的擦除或写操作指令,其中单次擦除时擦除区域大小为256 Byte扇区的倍数;单次写操作时编程区域大小可为1~32 Byte,与JTAG 指令定义保持一致。

此款国产PROM 芯片控制状态机复位的来源包括上电复位(POR)、VCCO 掉电复位和VCCJ 掉电复位。这3 种复位均为模拟模块,不需要时钟即可工作,其作用是保证在施加电源后,模拟和数字模块初始化至已知状态[6]。由于系统复位源与PROM 状态机的40 MHz 与OSC 时钟为异步关系,芯片电路设计采用异步复位、同步撤销设计,对系统复位进行同步处理后,接入PROM 状态机异步复位端,如图7 所示。

图7 PROM 控制状态机复位电路Fig.7 PROM Control State Machine Reset Circuit

3 失效机理分析

在正常情况下,当复位同步2 寄存器复位撤离后,状态寄存器1 和状态寄存器0 均由“1”跳转至“0”。当状态寄存器1 和状态寄存器0 工作在寄存器锁存数据的最低工作电压1.5 V 以下时可能跳转至“0”,也可能保持在复位值“1”,其状态不能稳定输出。当状态寄存器[1:0]跳转至“00”时,PROM 控制器仍为正常功能;当状态寄存器[1:0]跳转至“01”时,PROM 控制器跳过初始化进入空闲状态;当状态寄存器[1:0]跳转至“10”时,PROM 控制器跳过初始化进入写操作状态,如图8 虚线所示。而在断电时VCCO 和VCCJ分别有掉电复位保护,正常空闲状态的状态机不会误翻转到写操作状态。

图8 PROM 控制状态机异常跳转图Fig.8 PROM Control State Machine Error Diagram

电路中编程地址寄存器的复位值为全“0”,该寄存器值会送往PROM 芯片地址端,因此PROM 地址在复位后始终为全“0”开始。编程字节计数寄存器和编程数据寄存器作为外部输入的缓冲寄存器采用不带异步复位端口的寄存器,在系统复位期间它们不会被复位。寄存器是双稳态电路,未被复位的寄存器在上电后的状态不能确定为高电平或低电平,因此可理解为随机值。在正常JTAG 编程指令中,JTAG 会对编程地址、字节计数、数据寄存器进行写操作,因此编程字节计数和数据寄存器上电复位期间是随机值不影响正常流程的操作。

PROM 状态机单次写操作状态可写入1~32 Byte数据,当编程字节计数寄存器为随机值时,PROM 单次编程状态最多写入32 Byte 数据。由于工作电压异常,导致PROM 控制状态机从复位状态011 误跳转为编程状态010 时,PROM 控制状态机会对PROM 的复位地址即0 地址发起1~32 Byte 随机大小的随机数据写入,导致PROM 前32 Byte 数据被改写。进而导致后续FPGA 上电配置时发现比特流同步头数据出错,自动停止配置,导致FPGA 配置失败。

由于低于上电复位阈值时状态机有过复位过程,因此在不受控的电源电压范围内状态机大概率是保持复位状态,从而正常翻转到初始状态。不受控的电源电压范围内状态机跳转到写操作状态或空闲状态的机会均等,其中空闲状态也不会改写数据,因此状态机异常改写数据的概率极低,但有发生的可能性。

4 防护措施

4.1 技术措施

在使用软件烧写工具(如Xilinx iMACT)时勾选写保护功能,可防止数据改写。进口及国产FLASH 型PROM 都带有写保护功能,当状态机进入编程010 状态后,首先会读取保存在FLASH PROM NVR 区的写保护位,并将此位的数据与待编程数据进行“或”操作后送往PROM。由于PROM 编程只能写“0”,当数据均被写保护电路箝位为“1”时,编程动作不会改写FLASH PROM 内部数据。此时即便发生上电状态机误跳转,也不会产生PROM 数据被改写致使配置数据失效,可规避初始化异常对存储体配置数据的改写。

在开启写保护后在仿真时进行错误注入,可以看到当PROM 状态机从复位状态错误地跳转至编程状态时,PROM 的DIN 被箝位至高电平,未出现数据误改写故障,如图9 所示。同时,为验证措施有效性,对故障产品进行故障复现及措施有效性试验验证情况。对同一台故障产品进行60 ℃,48 h 高温老练试验补充试验,分别开展更改措施实施前后的试验比对验证,每次验证24 h,验证过程中使用自动设备每间隔5 min为整机上、断电,并检测FPGA 配置成功与否,如配置失败,则重新通过人工烧写PROM 配置程序后继续试验。试验验证结果为:未加措施前,24 h 内故障复现4 次。增加措施后24 h 内故障未出现,高温老练试验通过,可以证明该措施有效。

图9 写保护仿真图Fig.9 Write Protection Simulation

4.2 管理措施

在采购芯片时要求芯片供应商增加系统板级上电复位阈值测试筛选,并提供筛选测试报告。经过对此款芯片设计及工艺复查后,芯片供应商提出的筛选办法为:通过在电源电压2.0 V时进行写操作并且在3.3 V正常电压时读取上一步写的地址数据,数据有改写则为失效品,以此避免缺陷芯片出厂。筛选过程中写操作使用2.0 V 电源电压由芯片供应商确定,并保证筛选的有效性。同时,在系统层要求烧写PROM 数据时勾选写保护选项。

5 结束语

经分析认为,FPGA 配置用FLASH 型PROM 数据失效原因是国产PROM 器件上电复位阈值低于最低工作电压,在高温老炼过程中偶发写状态机错误跳转至编程状态,使FPGA 配置文件被改写。针对此问题提出了行之有效的技术及管理防护措施。