基于5G 通信的差分运算放大器的研究与设计

2021-08-18罗骏

罗骏

(中国电子科技集团公司第三十四研究所,广西桂林,541004)

0 引言

基于5G 通信技术的差分运算放大器的研究与设计,分析 5G 通信技术与差分运算放大器之间的关联。5G 通信传输的是毫米波,之前的频率带宽完全满足不了,也由此对毫米波技术研究逐年深入。

设计的参数目标是,在0.35umCMOS 工艺上,使用Cadence软件设计的一个基于5G 通信技术的差分运算放大器,电路能到达预期指标:开环直流增益:80dB,单位增益带宽:200MHZ,相位裕度:70°,转换速率:200V/ns,输出摆幅:-1.6V~1.6V。

1 运算放大器的原理与结构比较分析

1.1 运算放大器的原理介绍

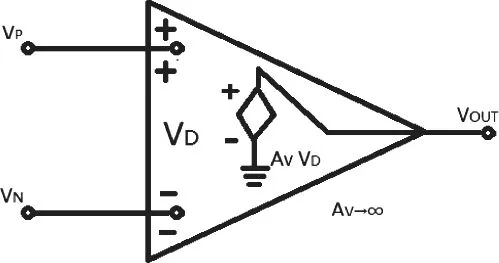

运算放大器,英文全称是Operational Amplifier,缩写为OPA,简称运放。其符号如下:

在上述图2 中,是基本运算放大器的等效电路。在图中,Vd 是差分输入电压,是Vp 和Vn 两个输入端电压的差值

图1 运算放大器的表述符号

图2 理想运算放大器等效电路

Av 为运算放大器的增益,也叫无载增益。

我们可以通过选择电路的结构,或者增加缓冲级等诸多方法,使得实际运放电路的增益和输入输出电阻接近一个理想的情况。

1.2 设计选型比较分析

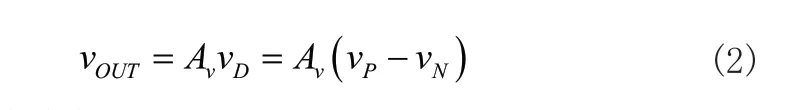

1.2.1 简单的全差分结构

在图3 所示给出的是运放电路中的全差分结构,Vdd 表示电源电压,Iss 代表了一个恒流源,NMOS 单管M1 和M2 构成了一个输入差分对,其他两个PMOS 管M3 和M4 构成两个负载,从图中可以得到最终输出摆幅公式为:

图3 简单全差分结构

简单全差分结构增益并不高,通常为20dB~30dB。

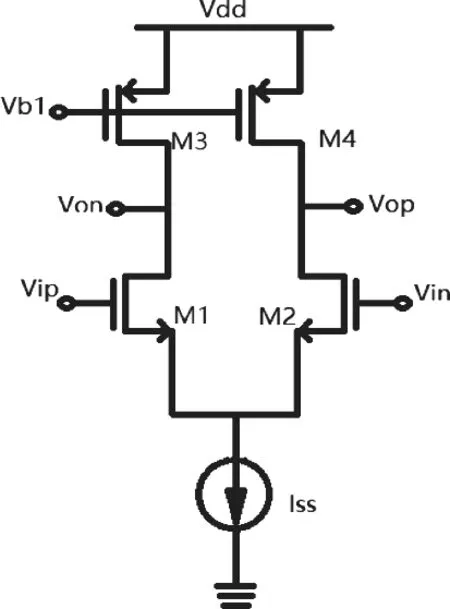

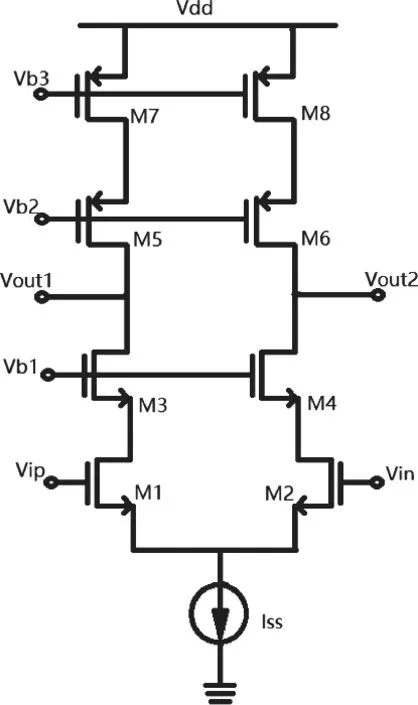

1.2.2 套筒式共源-共栅结构分析

为了具有更快的响应频率,便引出了套筒式共源-共栅结构。其思路是提高运放的输出电阻以增大运放电路的增益。具体结构如图所示4。它的低频小信号增益公式为:

套筒式结构的增益大约在60dB~70dB,但它的缺点是以减小输入摆幅和输出摆幅为代价去得到高增益的。如图4 给出的套筒式全差分结构,它的输出摆幅为:

图4 套筒式运算放大器电路结构

其中,V ODj表示Mj 管的过驱动电压,Vss 代表Iss 两端的电压。为了使M1 正常工作,让它工作在饱和区,那么它的输入电压则必须满足(7)的式子:

1.2.3 折叠式共源-共栅运算放大器

以上讨论结构都存在着很大的缺点,由此引出了折叠式共源-共栅结构,增益和摆幅这两参数上都有不错的性能,具体电路结构如图5 所示,这种结构分离了输入管,使管减少了在同一支路上层叠的现象。输入电压的范围也比套筒式结构增大了两个过驱动电压,它的输入电压范围用公式可表示为:

图5 折叠式共源-共栅运算放大器基础结构

而其低频小信号增益要比套筒式共源-共栅结构要小一点,具体公式为:

设计这种电路思路是把输入管给分离出来,从而使得在单独的一条支路上尽可能减少管的叠加。这种接法的管优点是输出摆幅相较其他两种结构大,也可以实现输入和输出短接,还可以作为单位缓冲器等。但它的缺点也很明显,多了两条支路,功耗相对增加,同时噪声也比其他两种结构大。

根据以上分析选择以折叠式共源-共栅结构作为设计基于5G 应用的基础结构。

2 基于5G 通信的差分运算放大器的电路设计与仿真

2.1 两级运放设计与仿真

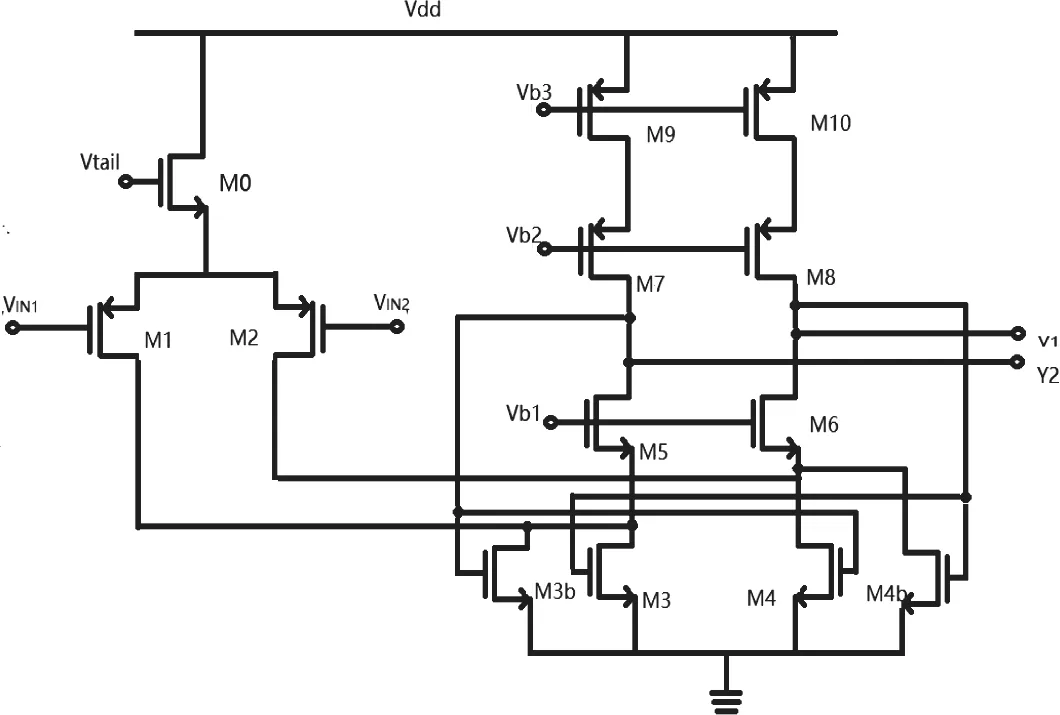

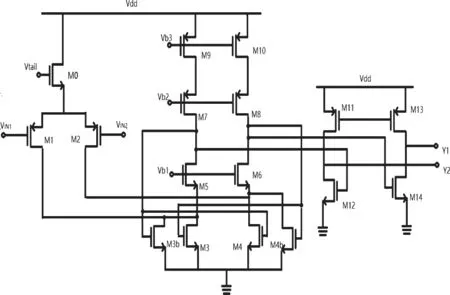

目前最广泛的应用差分运放结构就是两级运放,这种电路结构的优点是比一级更容易得到高的增益,同时还能得到较高的输出摆幅。为了同时发挥两级运放的两大优势,设计时第一级由管M0~M10 组成,使用的是折叠式共源共栅结构,用来尽可能大的提高增益,第二级由管M11~M14 组成,使用的是以电流镜为负载的共源放大器,可以得到较大的输出摆幅。

在设计的电路中,如图6 所示为输入级,对它的开环直流增益进行仿真,得到如图如图7 所示的结果,求得其增益为44.42dB。

图6 输入级输出级

设计两级运放的输出级为一个以电流镜为负载的共源放大器,如图8 所示,输出级主要提供一个低的输出阻抗以此来实现较大的输出摆幅,其仿真结果如图9 所示,在图中横坐标代表频率值,纵坐标代表开环增益值,由此可得增益为89.43dB,单位带宽为256.8MHz。

图8 输入输出级

2.2 开环增益与单位增益带宽仿真

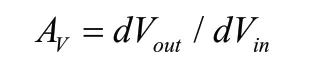

运算放大器的增益是一个重要的性能指标。增益表达式为:

差模增益仿真:由于信号差分输入,因此两个小信号应设置为大小相同,方向相反的两个变量。为方便计算,将差分量设置为1V,两个小信号就各分0.5V。测量双端的增益大小,得到测量结果。

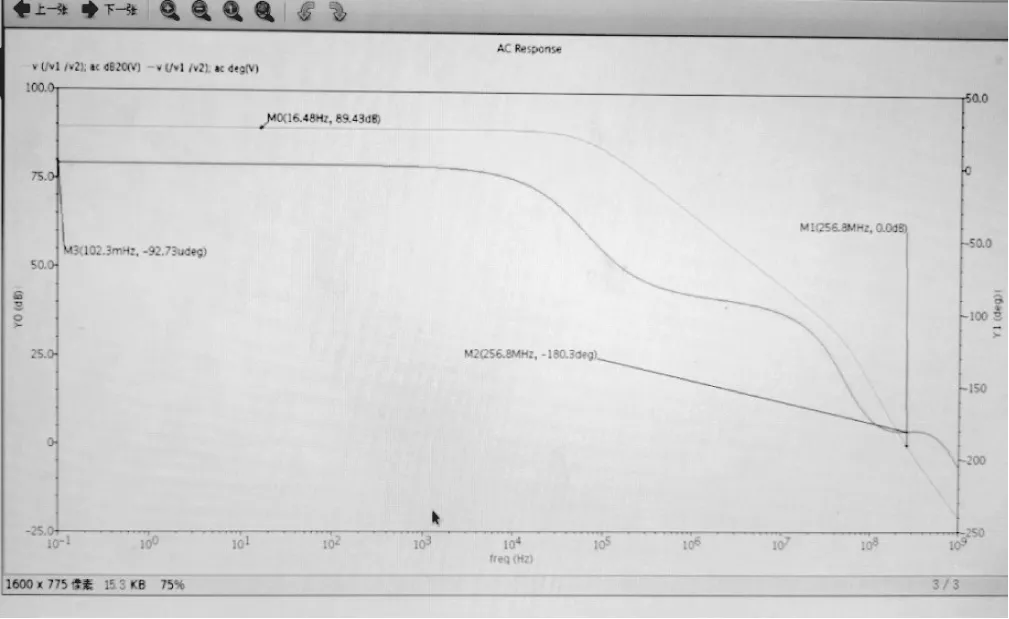

如图9 是二级运放电路的开环增益与单位带宽的仿真,在图中横坐标代表频率值,单位为Hz。纵坐标代表开环增益值,单位为分贝,开环增益在频率较小时是不随频率的变化而变化的,但当频率大到一定程度时,开环增益将随频率值的增大而减小。得到开环增益值为89.43dB,满足初期预设指标,单位增益带宽达到256.8MHz,满足预期指标200 MHz。

图9 开环增益与单位增益带宽的仿真截图

2.3 相位裕度仿真

相位裕度(Phase Margin, PM)是衡量系统稳定程度的的重要性能指标。用仿真得到的增益波形图和相位波形图来计算。

为了运放电路的稳定性与运放的响应速度有一个相对完满的折中,一般认为相位裕度至少要45。对所设计的电路用Candence 工具进行相位裕度仿真,如图10 所示,横坐标代表频率值,单位为Hz,纵坐标代表开环增益值,单位为分贝,再由M2、M3 可求得到相位裕度为92°,完全满足本次论文的预期指标70°。

图10 相位裕度仿真

2.4 建立时间

建立时间是衡量运算放大器速度的重要指标,它表示(阶跃)从输出开始到输出稳定的时间。测量时可以将输入小信号设置为阶跃信号。通过瞬态仿真和计算器求得。

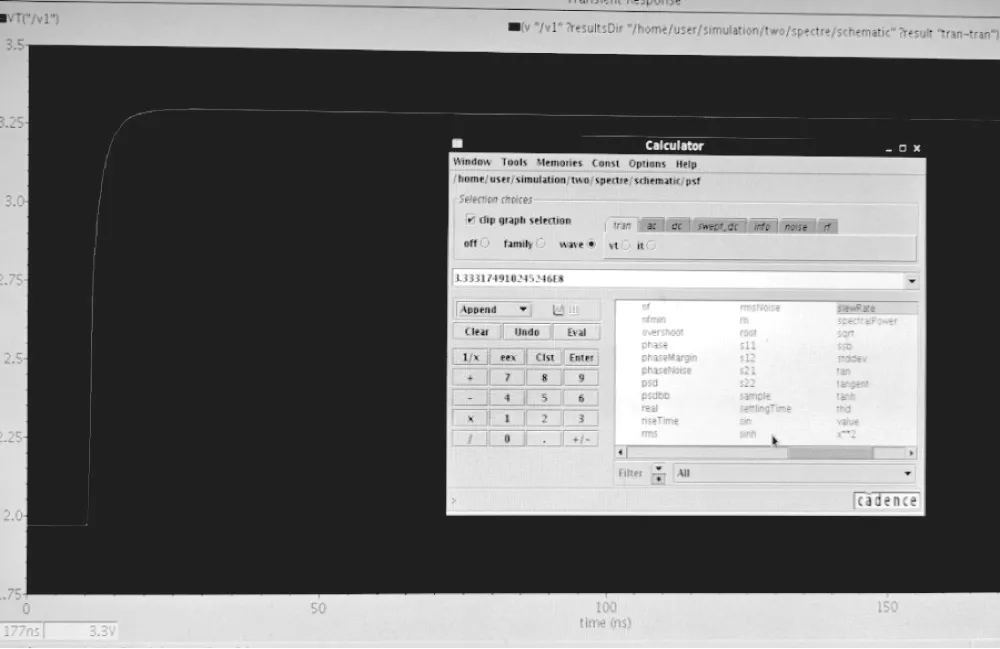

如图11 所示,横坐标代表时间,单位为纳秒,纵坐标代表电压值,单位为伏特,得出建立时间仿真结果,用"Calculator"计算的时间值为15.31ns,完全满足本预期设计需求。

图11 建立时间仿真结果

2.5 转换速率

转换速率表征运放对大信号的处理能力,其值越大表示其对信号的细节成分还原能力越强。

转换速率其仿真截图如图12 所示,其中横坐标代表时间,单位为纳秒,纵坐标代表电压值,单位为伏特,仿真图值可用软件自带的计算器算出结果,其值为333.31V/us>200 V/us,满足预期需求。

图12 转换速率仿真仿真结果

2.6 输出电压摆幅

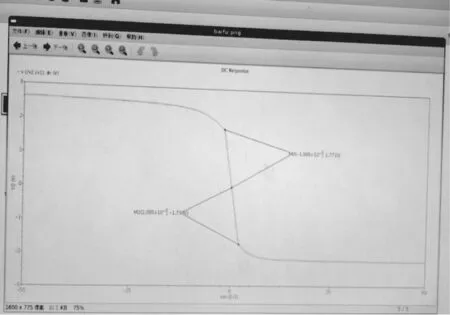

摆幅:在正常情况下输出的最大动态范围。由设计目标要求摆幅大于3.2V,故需单边摆幅大于1.6V。已知电源电压为3.3V,则输入管跟尾电流源可以分配最大为1.7V。为得到运放输出摆幅,仿真时需要对信号进行直流扫描。将输入小信号信号设置为变量,在DC 扫描设置时,应将扫描范围设置为一个负值到一个正值,从而获得双边摆幅。得到输入输出曲线后,将输入在0 值附近的那段呈线性关系的范围对应的输出作为放大器的摆副。其仿真结果如图13 所示,可得到结果上摆为1.77V,下摆为-1.73V,满足预期指标。

图13 输出摆幅仿真截图

3 总结

根据5G 传播信号的特性设计出其传播电路,从运算放大器基础电路结构出发,比较了这几种电路的优缺点,确定设计电路结构。

对所设计的结构加以改进,改进MOS 管的宽长比,改进偏置电压所设值,所有MOS 管都处饱和区,设计出符合预期参数要求的电路。设计出一款在3.3V 的电源电压下,增益为89.43dB、单位增益带宽为256.8MHz、相位裕度为92°、输出摆幅为3.4V、建立时间为15.31ns、转换速率为333.31V/us完全满足预期指标。