基于国产FPGA的星载Nor Flash控制器设计与验证

2021-08-11白云飞安军社

祝 倩,白云飞,安军社

(1.中国科学院 复杂航天系统电子信息技术国防科技创新重点实验室,北京 100190;2.中国科学院 国家空间科学中心,北京 100190;3.中国科学院大学,北京 100190)

0 引 言

随着电子通信技术的飞速发展以及国防要求的进一步提高,航天工程中卫星所承载的任务日益繁杂且难度各异。因此,设计一款用于集中处理中低端卫星任务的星载存储控制器尤为重要。Nand Flash虽然具有价格低廉,存储容量大等特点[1-2],但却因存在出厂坏块[3]等不可避免的因素而无法保证航天通信工程中必需的高可靠性与稳定性。而Nor Flash凭借其高传输效率,操作简单且性能稳定等优势在航天工程的星载存储系统中被广泛应用。

目前,Nor Flash控制器一般与静态存储控制器整合在一起,其控制逻辑复杂,读写速度慢[4],难以满足航空航天领域系统芯片低功耗要求。文献[5]在常规嵌入式Nor Flash控制器设计的基础上增加了Nor Flash测试电路的设计,实现了对Nor Flash存储器的读写控制和片外可测试功能。但在常规的Nor Flash控制器设计算法中始终存在编程和擦除操作速度远低于Nand Flash等问题。文献[6]设计的Nor Flash控制器IP中采用了硬件解锁、简化擦除模块等方法有效提高了总线利用率从而实现了快速读写,该硬件解锁的方法与软件解锁相比虽然解锁速度更快,但设计的灵活性却大大降低。文献[7]为满足不同型号Nor Flash芯片的兼容性,提出一种软硬件结合的方法实现接口控制器,但依然需要以牺牲部分时间性能为代价来换取对不同型号芯片的支持。为进一步优化Nor Flash的擦除和编程操作速度,提高整个星载存储系统的工作效率,本文设计了一款改进型的Nor Flash控制器,并且通过modelsim仿真和FPGA开发平台分别对设计结果进行了验证。

1 设计方案

Flash存储器选用SPANSION(飞索半导体)的S29GL256P型号产品[8],属于Nor Flash芯片。该芯片主要特点有:3V单电源供电,内部产生高电压进行读取、编程、擦除等工作;芯片存储容量为64 Mbit,可配置为字模式或字节模式;内部分为256个扇区,每个扇区是独立的,可单独进行读写或擦除等操作。该芯片操作简单,只需按照芯片手册中的规定时序将指令序列写入控制器中的命令寄存器,即可完成相应操作。

针对该芯片特点,Nor Flash控制器的优化设计方案如下。

1)在芯片擦除操作中引入解锁省略功能,以提高芯片擦除速度。解锁省略功能允许主机系统向闪存设备发送编程命令,而无需预先在命令序列内写入解锁循环,从而缩短芯片擦除操作时间。

2)在芯片编程模块中增加设计写入缓冲器编程算法,写入缓冲器编程允许系统在一次编程操作中写入最多32个字。与标准的单字编程算法相比,这一优化有效提高了字编程速度。

Flash控制器设计架构如图1,整个控制器将FPGA作为核心器件[9],由以下几部分组成:URAT接口模块,用于和外部主设备通信,实现主设备和主控系统之间的数据交换;数据寄存器和地址寄存器分别用于存储目标数据和地址;配置寄存器主要用于存储或修改Flash芯片的配置信息;状态寄存器主要用于存储记录各个操作的运行状态并返回给接口模块。

图1 星载Nor Flash控制器结构框图Fig.1 Block diagram of spaceborne Nor Flash controller

主控结构主要包含2个有限状态机(FSM)的设计:①是主状态机,负责根据输入的用户命令将其转为相应的Flash控制顺序;②是时序参数控制状态机,根据读出或擦洗的时序参数来控制输出的物理控制信号的时序,可调时序参数如表1。

表1 可调参数表Tab.1 Comparison table of adjustable parameters

控制系统的信号流程为:①UART接口模块通过读写LocalBus总线寄存器对主状态机进行配置,主状态机根据接收到的命令将其转化为相应的Flash读写控制顺序;②将控制信号发送到时序参数控制状态机,时序控制状态机根据读写的时序参数确定进入读或写时序,与此同时状态机的运行状态被存入状态寄存器;③将最终的控制信号与地址数据信号被发送给Nor Flash芯片以执行相应操作[10]。

本存储控制器的设计采用LocalBus总线作为系统内部总线标准(LocalBus总线是IBM公司提出的CoreConnect总线中面向Core+ASIC开发或SoC设计的总线规范,用于连接高速外设,现已在嵌入式系统开发中得到广泛应用)。

2 编程算法优化

根据系统设计框图及Flash芯片数据手册中对时序的具体要求,采用Verilog HDL语言编写有限状态机,实现对Flash芯片的擦除、读、写等操作。操作通过向命令寄存器中写入特定命令或包含特定地址和数据组合的序列来启动。

2.1 操作优化

Flash芯片的写操作包括擦除和编程操作,且在执行写操作之前需先执行擦除操作。标准的芯片擦除是一个6总线循环操作,每个循环的具体含义如表2。

表2 芯片擦除操作命令Tab.2 Command of chip erasing operation

在改进的擦除操作中,引入解锁省略功能,即将总线循环中的解锁循环操作进行屏蔽。解锁省略功能允许主机系统向闪存设备发送编程命令,而无需预先在命令序列内写入解锁循环,从而缩短芯片擦除操作时间。

标准的单字节编程模式使用4个闪存命令写入循环对各个闪存地址进行编程,每个循环具体含义如表3。

表3 单字节编程操作命令Tab.3 Command of single byte programming operation

为进一步提高芯片编程速度,本文增设了写入缓冲器编程算法,写入缓冲器编程允许系统在一次编程操作中写入最多32个字。

写入缓冲器编程操作的每个循环含义如表4。该操作命令序列由前2个写入解锁循环来启动。第3个写入循环包含在编程的扇区地址写入的写入缓冲器加载命令。此时,系统写入数值“写入字数减1”,写入字位置加载到编程的扇区地址的页面缓冲器中,从而告知设备有多少写入缓冲器地址加载了数据以及何时会发出“编程缓冲器到闪存”确认命令。待编程的位置数不能超出写入缓冲器的容量(加载的数值等于待编程的位置数减1,例如,假设系统编程6个地址位置,则应向设备写入05h),否则操作中止,系统随后写入起始地址/数据组合。起始地址是待编程的第1组地址/数据对,使用地址Amax-A5选择“写入缓冲器页面”地址,所有后续地址/数据对必须位于所选的写入缓冲器页面内。一旦已加载指定数量的写入缓冲器地址,系统必须随后在扇区地址写入“编程缓冲器到闪存”命令,并使用最后一个数据加载地址位置作为检测编程操作状态时的地址。

表4 写入缓冲器编程操作命令Tab.4 Command of writing the buffer programming operation

2.2 操作编程

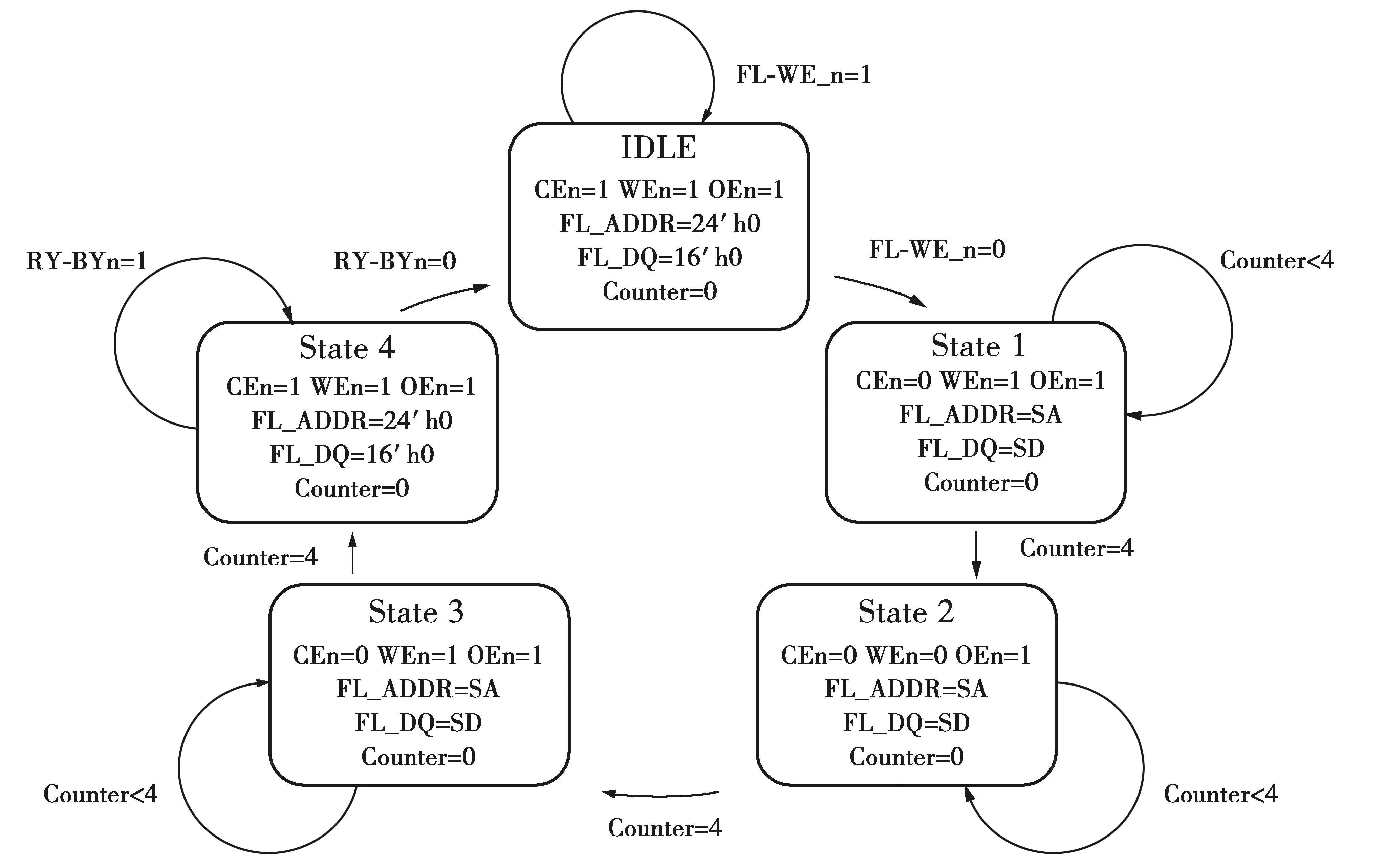

由Flash芯片数据手册中各操作的操作指令序列和时序波形图可分析出芯片各个状态间的转化过程。以执行写入缓冲器编程操作为例,实现向芯片中写入1个字/2个字节的具体过程,其状态转移逻辑如图2。

图2 Flash写入缓冲器编程操作状态转移图Fig.2 State transition diagram of Flash writing buffer programming operation

在写操作的状态转化过程中,共有包含IDLE在内的5个状态。每个状态由CEn和WEn的值来决定。CEn和WEn的电平高低随着每个状态的跳变而发生相应转化,且其转化的时序控制取决于计数器Counter,计数器Counter的具体值由系统时钟和操作过程中的地址和数据的建立及保持时间来决定。每通过一次图2的状态循环,完成向指定地址SA写入相应数据SD的字节编程操作,根据写入缓冲器编程操作中具体设置的编程字数N重复操作相应次数,最后根据状态位引脚的值判断写数据操作是否完成以及操作是否正确[11]。

3 系统测试验证

3.1 仿真测试

通过编写相应的顶层测试模块[12],利用Modelsim软件进行Flash芯片读写操作仿真[13],所得结果如图3—图5。

图3 芯片擦除命令执行和时序图Fig.3 Sequence diagrams of chip erasing command working

图4 芯片单字编程命令执行和时序图Fig.4 Sequence diagrams of chip single word programming command working

图5 芯片写入缓冲器编程命令执行和时序图Fig.5 Sequence diagrams of chip writing the buffer programming command working

由图3和图4可以看出,在有限状态机的算法控制下,Flash控制器可以将擦除或写指令序列正确写入Flash,并完成相应的擦除和写数据操作。从图4可看出,该Flash控制器实现了向地址880016h写入数据1234h的单字编程操作,符合标准读写算法预期设计目标。

图5中,Flash控制器分别向地址880007h,880008h,880009h和88000ah均写入16位数据efefh,即实现了在一次编程操作中连续写入4个字的功能,符合写入缓冲器编程命令算法的设计目标。

3.2 功能验证

为进一步验证该星载存储控制器的实际性能参数,选用ER2C3000-G系列FPGA开发板作为验证平台(实物图如图6),这是首次利用该开发板作为Flash控制器性能验证平台。ER2C3000-G型FPGA芯片为中科亿海微电子科技有限公司和中国科学院电子学研究所自行研制,是主要面向低成本、低端应用领域、中等规模的FPGA产品。该型号FPGA可与XILINX公司的XQR2V3000型号的FPGA兼容,整体性能二者相当,部分指标ER2C3000-G优于XQR2V3000。该国产FPGA开发平台已多次成功完成航天在轨验证任务,应用该开发平台不仅可大大降低航天工程星载存储系统的成本,也是对国产FPGA芯片发展的大力支持。

图6 ER2C3000-G系列FPGA开发板Fig.6 ER2C3000-G FPGA development board

利用与该开发板配套的电子所自主开发的编译环境软件Passkey3.0对控制器代码进行综合实现,整个星载存储控制器所占用的FPGA的逻辑资源不足1%(253/79040),占用引脚比例为11%(130/1212),证明了该存储系统的架构精简,可进一步用于嵌入式SoC系统开发工程中。

基于以上所研究的星载Flash存储控制器,设计了一款基于该国产FPGA开发板的星上SoC系统,架构框图如图7。系统采用龙芯开源软核处理器LS132作为主控CPU,AXI总线作为连接CPU和外设控制器的总线[14],AXI总线接口的片内BRAM作为SoC系统的数据存储器,本文所设计的Flash控制器通过连接开发板上的Nor Flash芯片作为该SoC系统的程序存储器。通过设计编写若干外设控制器,验证CPU能否通过执行程序访问外设控制器,进而控制外设进行相应操作。验证过程所用到的开发板上的资源主要有FPGA(片内含SRAM)和Nor Flash芯片等,已在图5中标出。

图7 SoC验证系统架构框图Fig.7 Illustration of SoC verification system framework

设置工程的系统时钟为10 MHz时,分别利用标准单字编程操作、硬件解锁单字编程操作[3]和写入缓冲器编程操作等3种方式向Flash一次性写入16个字/32字节,三者所用时间对比结果如表5,可知与标准单字编程算法相比,硬件解锁单字编程算法的编程速度约为其1.8倍;写入缓冲器编程操作优势更加明显,写入速度提高约3.5倍,符合预期设计目标。

表5 标准单字编程、硬件解锁单字编程和写入缓冲器编程操作执行时间对比Tab.5 Comparison of standard single word programming, hardware unlocking single word programming and writingthe buffer programming operations in execution time

4 结束语

本文介绍了一种基于国产FPGA的星载Nor Flash控制器设计方案,为满足航空航天工程需求,对方案进行了优化改进。结果显示,该方案有效地控制了FPGA资源占用率,实现了芯片快速读写,且该方案只需更改代码中的芯片配置信息即可适用于其他型号的Nor Flash芯片,具有良好的复用性。另外,本文所用的国产FPGA验证平台为实现国产芯片自主可控奠定了良好基础,对推动国产FPGA芯片进一步崛起与发展具有重大意义。