基于国产化平台的多路千兆以太网接口设计与实现*

2021-08-06戴玲琳罗劼夫

戴玲琳,罗劼夫

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

在目前通信设备中,千兆以太网通信接口已成为最常见和通用的数据传输通道。本文采用较低成本的国产化处理器、国产化FPGA和国产化PHY芯片搭建多路千兆以太网接口交互处理平台,可满足多路以太网数据内外交互需求,也可根据自身需求,基于FPGA设计实现自定义功能。

1 国产化交互平台设计

为了确保平台的应用推广性,国产化平台设计以实现数据交互性能达到1 000 Mb/s为硬性指标,采用较低成本和较低规格的国产化器件。本文采用CPU(龙芯2K1000)、FPGA(国微SMQ2V6000)和PHY芯片(JEM88E111)等国产化器件。它的平台架构如图1所示。

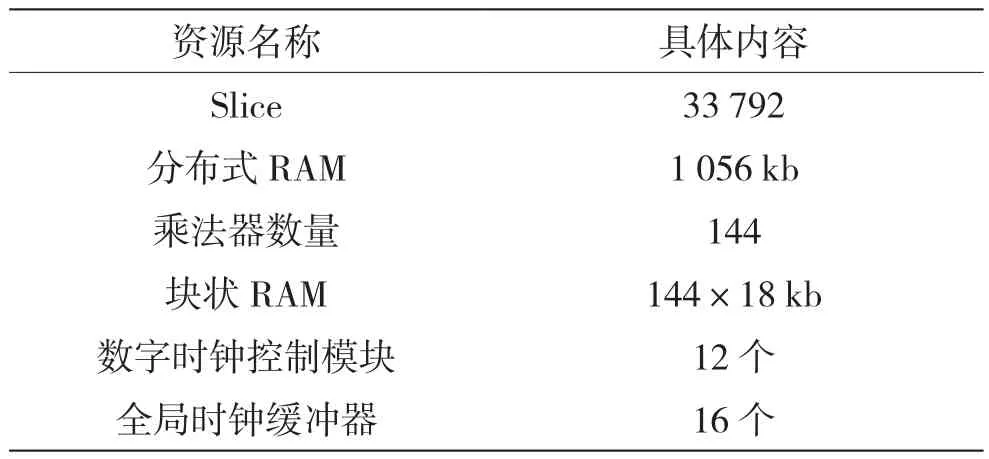

多路千兆以太网接口国产化交互平台对外提供2个通信网口,与背板采用Serdes总线进行交互,可实现自定义协议数据高速传输。FPGA与CPU连接接口为RGMII,与以太网芯片连接接口为GMII,可在FPGA内部实现自定义多路千兆数据交互。SMQ2V6000资源情况,如表1所示[1]。

表1 SMQ2V6000资源情况

2 FPGA设计与实现

2.1 FPGA总体设计

FPGA设计主要包括GMII接口模块、RGMII接口、时钟模块和自定义交互处理模块,总体设计框图如图2所示。

GMII和RGMII接口模块主要使用厂家提供的IP core,经过剪裁实现数据收发,对内统一将GMII接口和RGMII接口数据转化为SPI-3(System Packet Interface)总线,便于平台内部进行自定义交互处理[2]。时钟模块对FPGA全局时钟进行管理规划,分别为各个功能模块提供处理时钟;自定义交互模块用户可根据自身需求进行代码开发。

2.2 时钟资源优化

根据厂家提供的IP Core用户手册,GMII和RGMII接口数据接收、发送均需独立处理时钟。单路GMII接口时钟方案较为简单,其时钟逻辑框图如图3所示。接收时钟通过1个BUFG驱动作为IP Core的gmii_rx_clk时钟源,发送时钟经过1个BUFG作为gtx_clk时钟源和GMII接口线路发送时钟[3]。

由于RGMII接口是用时钟上下沿处理数据,其时钟处理较复杂。发送方向,时钟通过1个DCM和4个BUFG驱动相位为0、90、180、270的4种时钟。接收方向,线路时钟通过1个DCM和2个BUFG恢复相位为0°和180°的2种时钟。它的时钟逻辑框图如图4所示。

通过以上分析可得,FPGA实现2路GMII接口和2路RGMII接口所需全局时钟缓冲器为16个,已将SMQ2V6000全局时钟缓冲器资源全部占用,导致FPGA其他逻辑模块无法使用时钟资源。所以,必须优化时钟资源。时钟缓冲器使用数量对比,如表2所示。

表2 时钟缓冲器使用数量对比

时钟资源可通过以下方案进行优化:

(1)2路GMII接口和2路RGMII线路发送时钟可共用1个,时钟源为FPGA内部全局输入时钟,可减少使用3个时钟缓冲器;

(2)RGMII发送时钟模块只产生0°相位和90°相位的时钟,其180°相位和270°相位的时钟采用0°相位和90°相位的时钟直接取反得到,2路RGMII接口则可减少使用6个时钟缓冲器;

(3)RGMII接收时钟180°相位也可使用取反方式代替,可节约2个时钟缓冲器资源[4]。

通过时钟优化后,2路GMII和2路RGMII仅使用7个时钟缓冲器,因此SMQ2V6000资源完全满足设计需求。

2.3 多路RGMII接口时序优化

RGMII接口所有数据以及指示信号是时钟上下沿采样,时钟频率为125 MHz高频。在FPGA设计中必须对RGMII接口时钟、线路IOB、电平/驱动、上下沿采样以及时钟相位和位置进行约束,否则会引起线路数据恢复错误或不稳定现象[5]。本文将对国产化FPGA的多路RGMII接口调试常遇到的问题进行排查和分析。

2.3.1 单路RGMII接口调试

单路RGMII接口接收方向无数据,一般是由硬件问题和接收时钟与数据时序问题引起的。因此,需从这两方面入手进行问题排查。排查流程如图5所示。

硬件问题主要包括线路时钟频率稳定问题、PCB布线等长以及接口电平是否符合IPCore要求。若硬件设计均满足要求,RGMII接口接收方向依然无数据,则可能是由于接收时钟与数据时序问题引起的。RGMII接口采用接收时钟上升沿恢复低4 bit,下降沿恢复高4 bit。若时钟不稳定或者出现相位差,则导致恢复数据不正确,下一个模块采不到正确的帧头则会丢弃数据。该问题可在约束文件中对接收时钟进行频率和相位调整解决。

2.3.2 多路RGMII接口调试

由于国产化FPGA时钟资源限制,本文采用多路RGMII接口共用发送时钟解决该问题。但是,各路时钟FPGA内部不同的布局则会引起一路RGMII接口收发正常、另一路收发不正常的现象,需对多路RGMII多个接收、发送时钟时序同时进行约束和优化,具体步骤如下文所述。

(1)先调A路,记录各个时钟BUFG、DCM的位置,约束A路所有收方向时钟的BUFG位置。

(2)再调B路,记录各个时钟BUFG、DCM的位置,约束B路所有收方向时钟的BUFG位置。

(3)对比两次BUFG的位置,将相同的BUFG位置写入UCF文件。一般来说,RGMII数据收发不正常是由于发送方向时钟和数据存在相位差,所以在FPGA尽量将两路共用的发送BUFG设置在相近的位置。

(4)约束好时钟位置后,每路采用偏移相位的方法进行调试,根据数据恢复情况将时钟相位调整到最佳位置。

3 验证结果

本文在多路千兆以太网接口国产化交互平台上进行结果验证。FPGA内部对RGMII0接口与GMII0接口、RGMII1接口与GMII1接口客户侧数据进行交换,外部在背板上对两路Serdes进行环回处理。它的验证平台如图6所示。

验证过程主要在CPU网口0和网口1之间进行数据收发。FPGA内部对各个接口客户侧信号采集,其时序图如图7、图8所示,可得多路GMII和RGMII接口数据收发均正常。网口0和网口1数据收发均正常,证明该国产化平台多路千兆以太网接口数据交互正确稳定。目前,该硬件平台已成功应用于隔离交换项目。

4 结 语

本文搭建了一种低成本的国产化CPU+FPGA硬件平台,针对多路GMII和RGMII接口时钟资源冲突和时序不稳定问题,采用时钟共享、时序优化、相位调整等措施进行解决。大量数据的传输验证了其稳定性和可靠性,实现了多路千兆以太网接口交互。目前,该平台已成功应用于相关项目,同时可以广泛应用于需要多路以太网接口交互和数据处理的平台。