磁控溅射制备大面积原子级平滑超低电阻率TiN薄膜电极*

2021-08-04田忠杰史淑艳陈琦磊芮祥新黄新宇孙纳纳周大雨

田忠杰,史淑艳,陈琦磊,芮祥新,黄新宇,孙纳纳,周大雨

(1. 大连理工大学 材料科学与工程学院,三束材料改性教育部重点实验室,辽宁 大连 116024;2. 合肥安德科铭半导体科技有限公司, 合肥 230088)

0 引 言

金属-绝缘体-金属(MIM)电容器广泛应用于动态随机存取存储器(DRAM)和射频及模拟集成电路等微电子产品中[1-2]。当前高电容密度MIM电容器主要使用HfO2、ZrO2和TiO2等高介电常数(high-k)氧化物作为电介质绝缘层[3-6],且电介质层的物理膜厚普遍在纳米量级,DRAM产品中电介质层的膜厚甚至小于~10 nm。电介质层膜厚的降低使更大深宽比的3D纳米结构化成为可能,从而极大地提升了电容面密度,集成密度的瓶颈被不断突破,器件的性能获得大幅度提升。

MIM电容器的性能和可靠性不仅取决于电介质层的介电常数、禁带宽度和耐击穿电场强度等性质,也与电极薄膜材料的性质密切相关。电极薄膜要求具有高的导电性和大的功函数,同时表面粗糙度尽可能低。特别是随着电介质层厚度的减小,电极薄膜的表面粗糙度会严重影响电容器的可靠性。底电极粗糙度的增大会导致后续生长的电介质层厚度产生较大波动,同时在电极的微区突起出现电场集中,这使得电容器的漏电流密度急剧增加,击穿电压下降[7]。因此,为提升MIM电容器的性能和可靠性,一方面要选择导电性高、功函数大的合适电极材料,另一方面要尽可能降低电极薄膜的表面粗糙度。TiN薄膜因具有优异的导电性(文献报道最低电阻率为18 μΩ·cm)、较大的功函数(4.7 eV)、较高的熔点、较好的化学稳定性,并且制备工艺与微电子工艺兼容,现普遍应用于微电子器件中,是MIM电容器中与HfO2, ZrO2等介电材料理想搭配使用的电极材料[8]。在高介电常数MIM电容器越来越普遍应用的背景下,对TiN电极薄膜的电阻率、表面粗糙度等性能提出了更高的要求,因此薄膜制备技术的发展和优化十分关键。

面向微电子器件应用的TiN电极的制备方法主要有磁控溅射法、等离子体辅助化学气相沉积法、原子层沉积法等[9-12]。其中,采用磁控溅射技术制备的薄膜均匀性及致密性好且易于实现低成本大规模工业化生产,因而该技术受到了广泛关注。使用磁控溅射法制备纳米级厚度TiN电极薄膜时,在沉积过程中改变工艺参数,如衬底偏压,对薄膜的电阻率、表面粗糙度等性能产生较大影响[13],因此优化溅射工艺参数是提升TiN电极性能的重要手段。

本文以HfO2基薄膜电容器为研究背景,利用射频反应磁控溅射法制备TiN电极薄膜,并详细探讨了衬底偏压对TiN电极电阻率、化学成分、择优取向和表面粗糙度的影响规律及其内在的机制。通过优化工艺参数,最终在4英寸单晶硅衬底上成功制备出原子级表面平滑且具有超低电阻率的TiN薄膜,可满足多种微电子器件对电极材料的性能需求。本课题组目前已实现了4英寸TiN电极的小批量生产,并将该电极实际应用于微电子企业HfO2基薄膜MIM电容器的研发中。

1 实 验

1.1 射频反应磁控溅射法制备氮化钛纳米薄膜

以p-型(100)单晶硅为基底,基片经标准的RCA清洗流程后置于双室高真空磁控溅射设备中,本底真空抽至5×10-4Pa,采用纯度为99.995%的钛靶作为溅射源,靶基距为93 mm。以纯度为99.99%的氩气和氮气分别作为工作气体和反应气体,流量比为30∶2.5(单位sccm),工作气压0.3 Pa,射频电源功率200 W,衬底温度350 ℃,衬底偏压分别设置为0、-100、-150和-200 V,溅射时间统一为30 min。

1.2 材料表征

采用X射线反射仪(X-ray Reflectivity,XRR)获得样品厚度。采用RTS-9型双电测四探针测试仪测量TiN薄膜样品的方块电阻,通过计算得到TiN薄膜电阻率,同时通过对大面积电极进行多点测试反映薄膜均匀性。采用ESCALAB250型X射线光电子能谱仪(XPS)对薄膜进行化学成分分析。采用德国Bruker D8 Discover型X射线衍射仪(GIXRD)对TiN薄膜的晶体结构及择优取向进行分析,设定掠入射角为0.5°,2θ角为30°~70°。采用Bruker科技公司Dimension ICON型原子力显微镜(Atomic Force Microscope)对薄膜的表面形貌和粗糙度进行分析。

2 结果与讨论

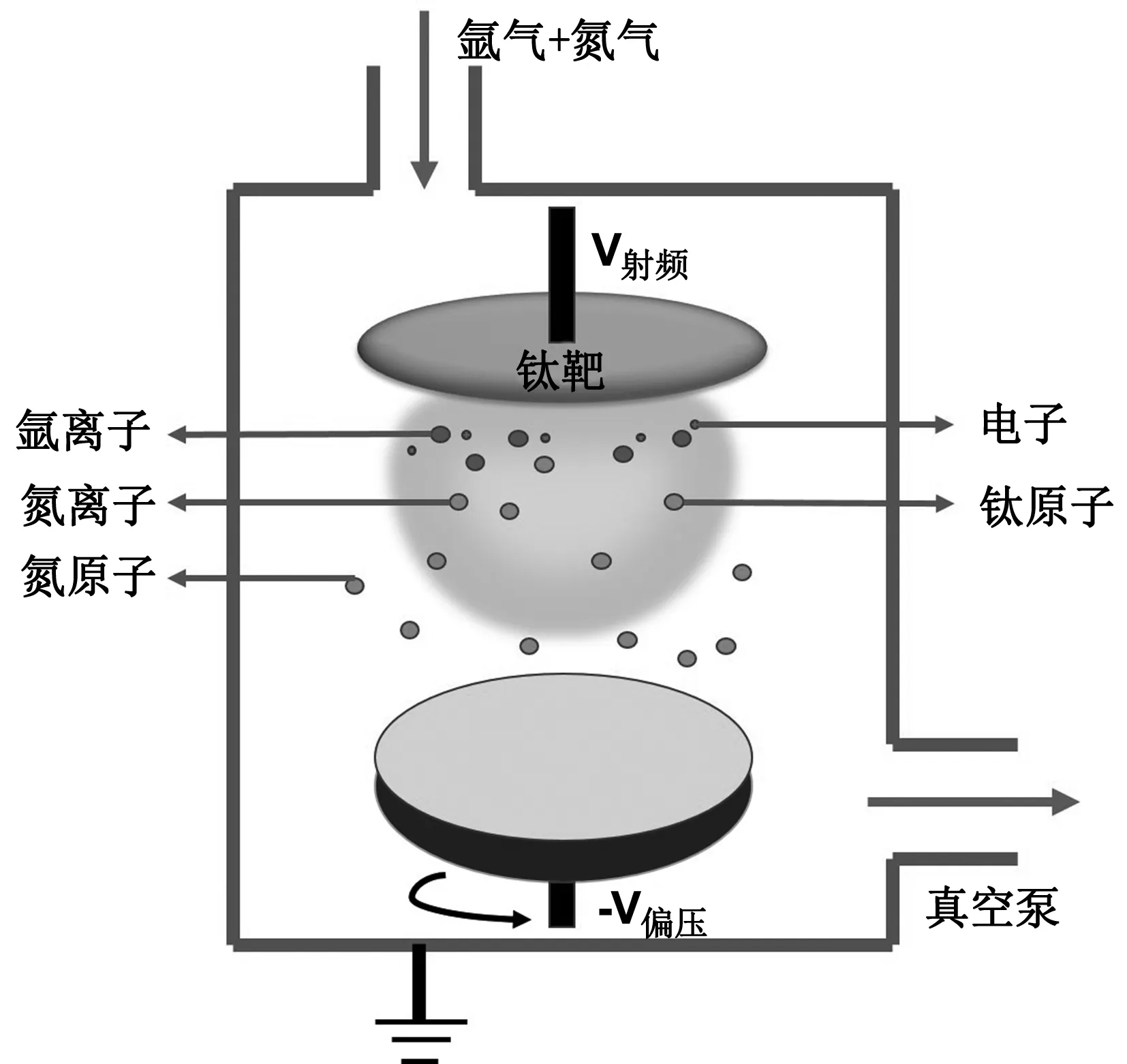

TiN纳米薄膜制备工艺如图1所示,腔室内通入氩气,靶材接入频率为13.56 MHz的射频电压致使在基片与靶材之间的区域产生异常辉光放电,建立稳定的等离子体区,Ar+在电场的作用下加速轰击靶材,溅射出来的Ti原子与激活的N原子在基片反应生成TiNx原子团,并通过形核扩散形成TiN纳米薄膜[14]。该过程与钛/氮原子的动能相关,其能量取决于衬底偏压、工作气压和基底温度等,因此本文重点研究了衬底偏压对TiN薄膜的性能的影响。

图1 射频磁控溅射法制备TiN薄膜工艺示意图Fig 1 A schematic of the TiN thin film deposition using radio-frequency magnetron sputtering

2.1 性能分析

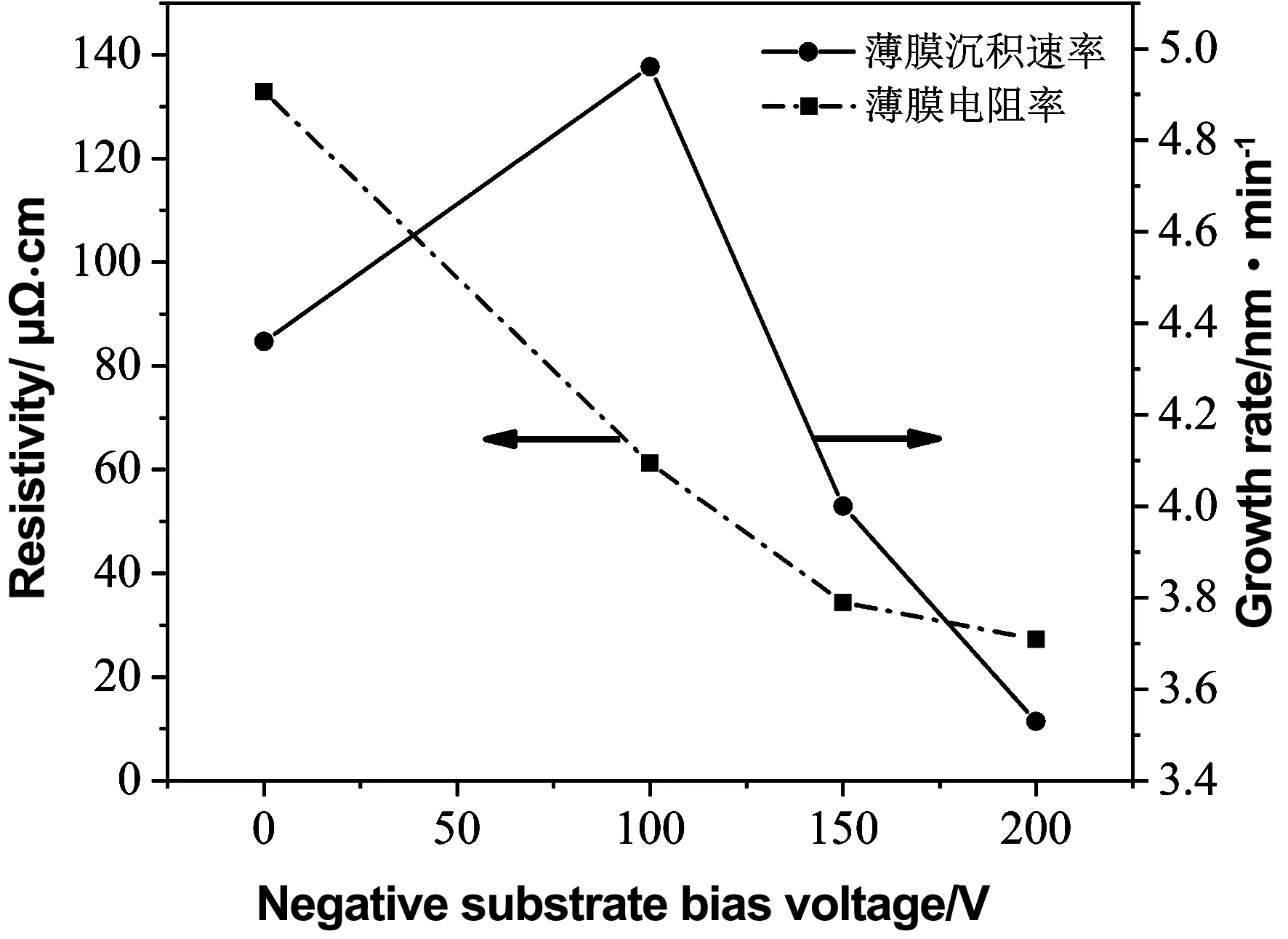

图2为在0 、-100 、-150 和-200 V衬底偏压下沉积的TiN薄膜的溅射速率和电阻率的变化曲线。在不施加衬底偏压时,TiN薄膜的沉积速率为4.37 nm/min;当施加-100 V衬底偏压后,其沉积速率略增加至4.97 nm/min。继续增加负偏压,TiN薄膜的沉积速率降低,当衬底偏压增大至-200 V时,沉积速率减小至3.53 nm/min。衬底偏压影响沉积速率的主要机制是当样品台上施加较低的负偏压后,吸引一部分带正电荷离子,如Ar+和Ti3+/4+等,加速飞向基片,碰撞携带更多的Ti原子到达基片并参与反应生成TiN薄膜,因此薄膜的沉积速率增加。当负偏压进一步增加时,带正电荷的离子在强电场作用下获得很高的动能对基片产生反溅射轰击效果。这一过程能够提高基片表面原子迁移率,同时也会导致弱键合的原子被溅射出去,从而使薄膜的沉积速率降低[15]。

图2 TiN薄膜的沉积速率和电阻率随衬底偏压的变化曲线Fig 2 TiN film growth rate and resistivity vs. substrate bias voltage

由图2可知,当未加载衬底偏压时,薄膜电阻率为132.9 μΩ·cm,随着负偏压的增加,薄膜电阻率逐渐降低。衬底偏压影响薄膜电阻率的机制主要是带电粒子在偏压电场的作用下获得加速,碰撞携带大量的Ti和N原子以较高的动能到达基片,这些表面原子具有更高的迁移能力,可以在基片表面更多的位点发生形核及扩散生长,因此薄膜内的孔隙体积分数降低,密度增大,内部缺陷减少;另一方面,在强衬底负偏压电场的生长条件下,聚集在晶界等处的N原子尚未与Ti原子结合,带电粒子的轰击导致过量的N原子被反溅射出来,致使薄膜内部Ti元素与N元素的原子比更趋近于1∶1,化学计量比接近1∶1的TiN薄膜电阻率最小[15],2.2节中的XPS化学成分分析结果将验证这一结论。此外,衬底负偏压增大使薄膜倾向于沿(200)晶面择优生长(见2.3节)也是电阻率下降的原因之一。当施加-200 V衬底偏压时,薄膜电阻率达到27.3 μΩ·cm,这一数值为所制备的样品中电阻率最低值,且接近文献中报道的单晶TiN薄膜的18 μΩ·cm电阻率[16]。

2.2 薄膜成分分析

本文采用XPS对薄膜进行化学成分分析。为避免薄膜表面吸附的氧、碳等污染物对成分含量的影响,在XPS分析前使用Ar+离子束对薄膜表面刻蚀处理10 min。图3(a)所示为未加载和加载-200 V衬底偏压下TiN薄膜的Ti 2p高分辨图谱,其中455.0、456.9和458.2 eV 3个峰位对应Ti 2p3/2的结合能,460.9、462.0和463.5 eV 3个峰位对应Ti 2p1/2的结合能,图3(b)所示为未加载和加载-200 V衬底偏压下TiN薄膜的N 1s高分辨分峰图谱,其中396.1和396.8 eV两个峰位对应N 1s的结合能。据Greczynski报道,位于455.03 eV附近的Ti 2p3/2峰和位于460.97 eV附近2p1/2eV峰的代表Ti-N键,位于457.0 eV 附近的Ti 2p3/2峰和位于462.0 eV 附近的Ti 2p1/2峰对应Ti-Ox键,位于458.2 eV附近的Ti 2p3/2峰和位于463.5 eV 附近的Ti 2p1/2峰为TiN的卫星峰(TiN-sat)[17,18]。图3(b)为薄膜样品的N 1s图谱,根据文献报道,位于396.3 eV附近的主峰对应TiN,位于398.3 eV附近的峰位对应TiN-sat[19]。XPS高分辨图谱结果表明薄膜中的主体成分为TiN,此外含有少部分TiOx化合物。XPS全谱分析结果表明,未施加衬底偏压的TiN薄膜样品中N、Ti、O元素的含量分别为46.8%、45.8%、7.4%,其中Ti原子和N原子的化学计量比为0.978。施加-200 V衬底偏压的薄膜样品中N、Ti、O元素的含量分别为45.8%、45.7%、8.5%,其中Ti原子和N原子的化学计量比为0.998。可以看出加载-200 V衬底偏压后,薄膜中N元素含量降低,Ti/N原子比更趋近于1∶1,实验结果与文献报道一致[15]。同时薄膜中存在少量的O,这是由腔室中的残余气体、工作气体及反应气体夹杂的少量氧气和水汽所致。

图3 衬底在无偏压或偏压-200 V下生长的TiN薄膜的XPS成分分析结果Fig 3 XPS analyses of TiN thin films deposited with and without -200 V substrate bias

2.3 薄膜物相分析

图4所示为在不同衬底偏压下制备的TiN薄膜GIXRD图谱。与TiN标准图谱比对可知,当衬底偏压分别为0和-100 V时,TiN薄膜同时存在(111)、(200)、(220)3个衍射峰。当衬底偏压设置为-150 V时,位于42.6°的(200)衍射峰显著增强。当衬底偏压设置为-200 V时,薄膜沿(200)晶面择优生长。很明显薄膜的择优取向受到衬底偏压的影响。薄膜的体系自由能是应变能和表面能的总和,TiN薄膜的择优取向是表面能与应变能的相互竞争以降低体系自由能的结果,其中(111)晶面具有最低的应变能,(200)晶面具有最低的表面能[20]。引入衬底偏压使带电粒子加速轰击薄膜表面,增加原子表面迁移率,致使薄膜的微观结构致密化,从而降低薄膜孔隙率;同时还增加了薄膜的应变能,从而影响薄膜生长的择优取向[21]。因此在反溅射作用下,薄膜易沿降低体系表面能的(200)晶面生长。TiN薄膜的电阻率与择优取向有较大关联,其中(200)择优取向相比于(111)择优取向使具有更低的电阻率,这是因为(200)晶面较低的原子密度减少了电子散射。当施加-200 V衬底偏压时,薄膜沿(200)晶面择优生长并具有最低电阻率,该实验结果与文献报道一致[9]。

图4 不同衬底偏压下制备的TiN薄膜GIXRD图谱Fig 4 GIXRD patterns of TiN films deposited at different substrate bias voltages

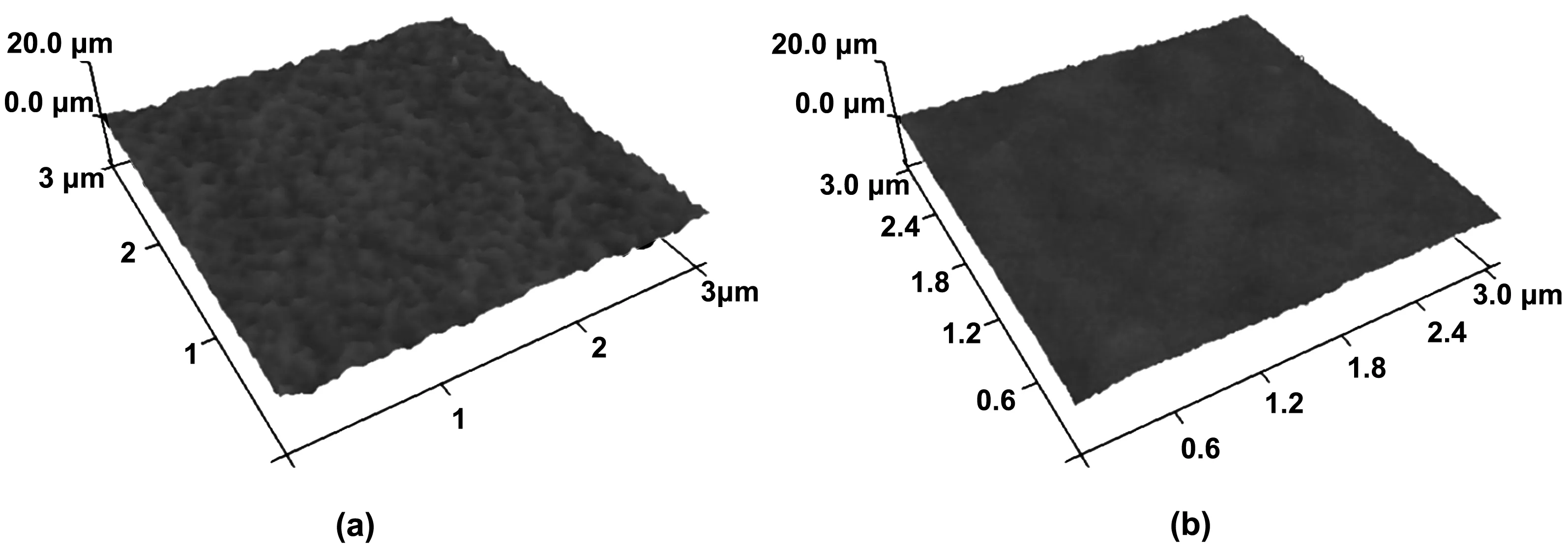

2.4 表面粗糙度表征

图5给出分别在0和-200 V衬底偏压下制备的TiN薄膜表面AFM形貌图,测试区域面积为3 μm × 3 μm。从图中TiN薄膜表面形貌可以直观地看出引入衬底偏压使得TiN薄膜表面趋于平滑,粗糙度降低,未加载偏压时薄膜的均方根粗糙度(RMS)为1.053 nm,-200 V衬底偏压时薄膜的均方根粗糙度为0.747 nm。表面粗糙度的变化反映了衬底负偏压对薄膜生长过程的影响。在衬底施加负偏压后,Ar+和Ti3+/4+等带电粒子对基片的轰击作用提高了薄膜表面原子的迁移率,导致原子在薄膜表面扩散速度提高,填补薄膜内间隙,使薄膜结构更加致密,表面趋于平滑,粗糙度降低[18]。该均匀致密的结构致使薄膜电阻率显著降低(电阻率结果见图2)。

图5 分别在0V(a)和-200 V(b)衬底偏压下沉积的TiN薄膜表面AFM图Fig 5 AFM surface morphology of TiN films deposited with 0V and -200 V substrate bias

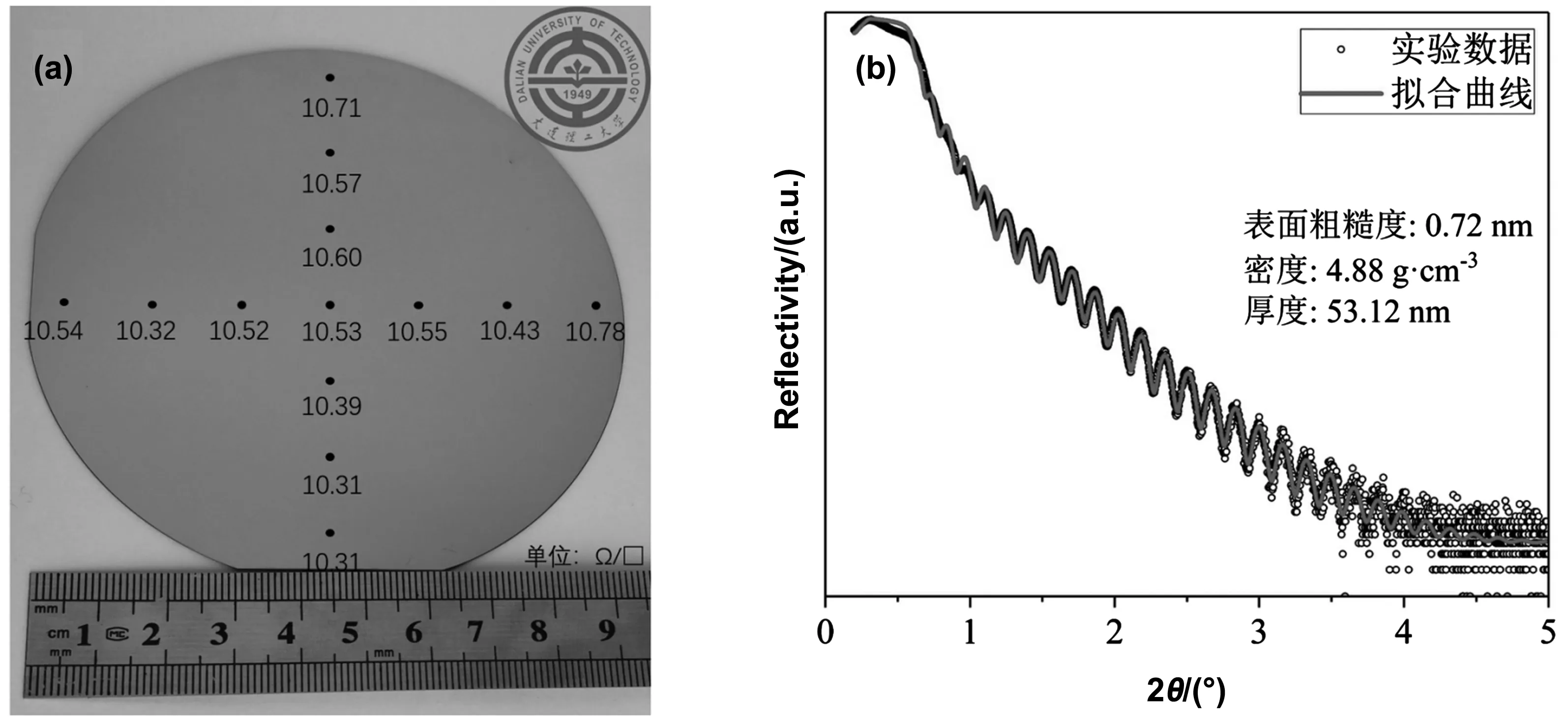

2.5 大面积TiN电极薄膜的制备

在工作气压0.3 Pa、射频电源功率200 W、衬底温度350 ℃、衬底偏压-200 V的工艺条件下采用4英寸单晶Si衬底制备TiN电极薄膜,沉积时间为15 min。由图6(a)可见,样品表面呈金黄色,没有宏观缺陷。对样品表面多点位进行四探针方阻测试,得到平均方阻值为10.504 Ω/□,均方差仅为0.143 Ω/□。图6(b)为样品XRR实测曲线和使用RCRefSimW软件得到的拟合曲线,经该软件拟合后得到薄膜表面粗糙度约为0.72 nm,密度约为TiN块体材料密度(5.43 g·cm-3)的90%,薄膜的平均厚度为53.12 nm,计算可知薄膜的平均电阻率为55.8 μΩ·cm。

图6 (a)TiN电极实物图,标示为各点位方块电阻值 (b)TiN薄膜X射线反射曲线和拟合曲线Fig 6 Picture of TiN wafer,the numbers are the sheet resistances at each location and experimental and simulated XRR curves of the TiN thin film

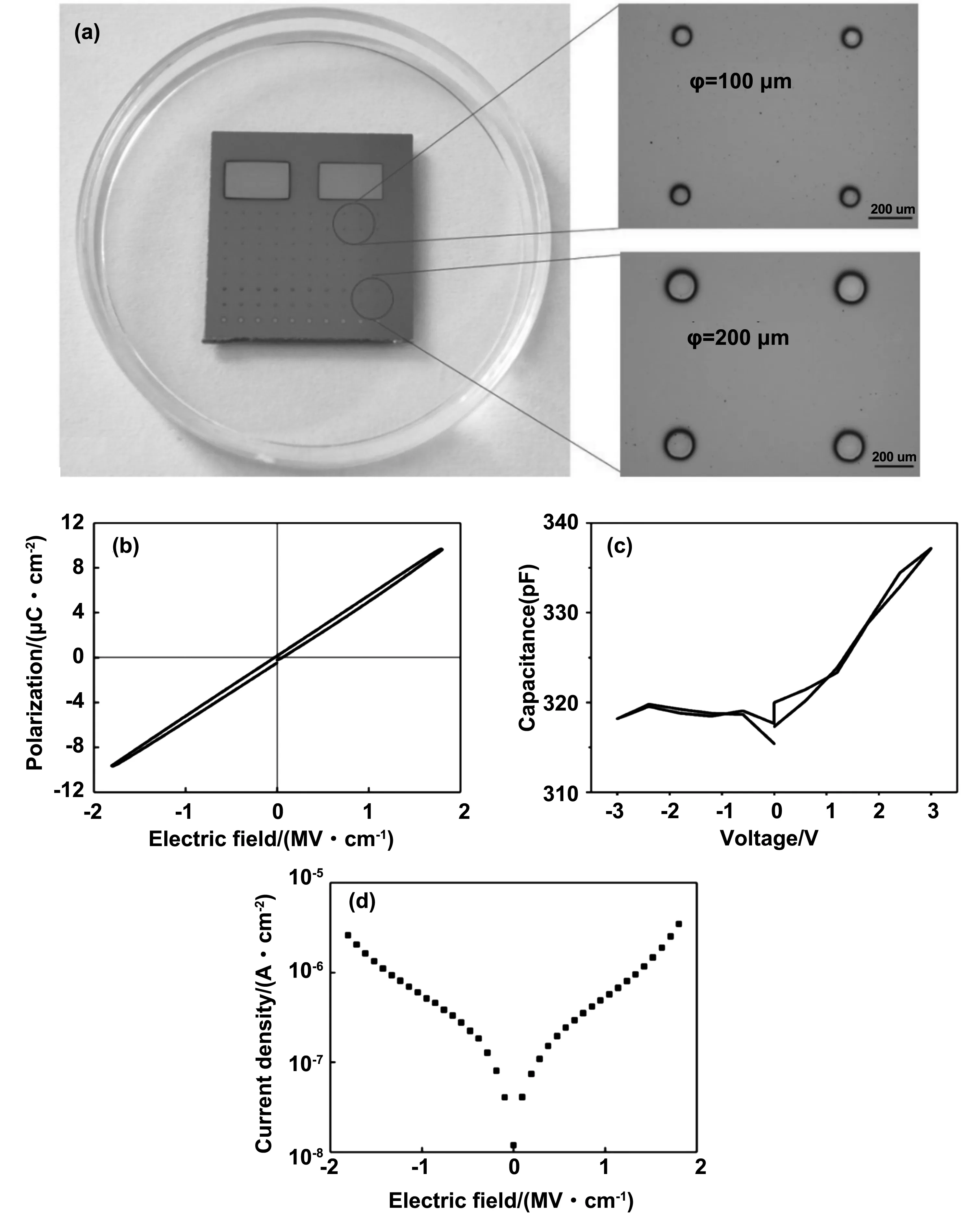

实验表明采用射频反应磁控溅射法可以进行超高导电性TiN薄膜电极的大面积制备,且薄膜的厚度及电阻率具有较好的均匀一致性,以该TiN薄膜作为底电极,采用原子层沉积工艺在其上生长厚度约为16.6 nm的HfO2薄膜,在氮气氛保护下650 ℃保温40 s使HfO2薄膜晶化,随后利用硬掩模版在HfO2薄膜上沉积TiN薄膜(膜厚约100 nm)上电极点阵。图7(a)展示的是切割为2 cm× 2 cm的HfO2薄膜电容器阵列照片。采用铁电分析仪(Radiant Multiferroic 100 V)测试薄膜电容器的极化强度-电场(P-E)曲线、电容-电压特性(C-V)曲线和漏导电流密度-电场(J-E)曲线,结果如图7(b)、(c)、(d)所示。P-E曲线显示出顺电材料典型的线性极化行为特性。根据C-V曲线在0 V下计算得到HfO2薄膜的相对介电系数为42。J-E曲线显示出薄膜电容器具有极好的电绝缘特性,在1 MV/cm的高场强下漏导电流仅为7.84×10-7A/cm2。结果表明采用本文工艺可制备超高导电性(ρ<60 μΩ·cm)、表面原子级平滑(RMS<1 nm)TiN薄膜,适合于作为纳米薄膜电容器的上下电极。

图7 (a)2 cm×2 cm的HfO2薄膜电容器阵列照片 (b)HfO2薄膜电容器的P-E曲线 (c)C-V曲线(d)J-E曲线Fig 7 (a) Picture of 2 cm× 2 cm HfO2 MIM capacitor array; (b) P-E curve of HfO2 MIM capacitor; (c) C-V curve of HfO2 MIM capacitor; (d) J-E curve of HfO2 MIM capacitor

3 结 论

利用射频反应磁控溅射在4英寸Si衬底上制备了大面积原子级平滑的高导电TiN电极并系统探讨了衬底偏压对TiN薄膜微观结构和电学性能的影响规律。结果表明:(1)当衬底偏压从0 V增加至-200 V时,沉积速率呈现先增加后降低的趋势,薄膜电阻率从132.9 μΩ·cm下降至27.3 μΩ·cm,化学计量比趋近于1∶1,择优取向从(111)转变为(200),同时表面粗糙度显著降低。(2)在施加-200 V衬底偏压时,以4英寸单晶Si为衬底制备的TiN电极薄膜的厚度及电阻率具有较好的均匀一致性。以该TiN薄膜作为电极制备的HfO2薄膜电容器具有良好的顺电性能和低漏电特性。该结果证明采用本文工艺制备的超高导电性(ρ<60 μΩ·cm)、表面原子级平滑(RMS<1 nm)的TiN薄膜适合作为纳米薄膜电容器的上下电极。