采用平面分栅结构的高增益宽带射频VDMOS 研制

2021-08-02宋李梅丛密芳李永强任建伟

于 淼 ,宋李梅 ,李 科 ,丛密芳 ,李永强 ,任建伟

(1.中国科学院大学,北京 100049;2.中国科学院微电子研究所,北京 100029;3.中国科学院硅器件技术重点实验室,北京 100029)

0 引言

硅基射频场效应晶体管作为固态功率器件,与双极型晶体管相比,具有线性度好、驱动电路简单、开关速度快、热稳定性好、没有二次击穿和可以多胞并联输出大功率等一系列优点[1-2],在高频(HF)、甚高频(VHF)和特高频(UHF)波段(如移动通信、广播、超视距雷达、磁共振成像、射频加热和无线电接收器等领域)得到广泛应用[3-4]。近几年来,虽然氮化镓(GaN)器件市场发展迅速,但是由于GaN 材料加工工艺复杂,成本较高,主要适用于3.5 GHz 或更高频段的高频大功率应用场合,而在较低频段,硅基射频垂直双扩散金属氧化物半导体场效应晶体管(Vertical Double-diffused Metal Oxide Semiconductor field effect transistor,VDMOS)由于成熟度和性价比更高而更具优势,因此,硅基射频VDMOS 主要应用在低频宽带大功率和对可靠性要求较高的领域[5-7]。

目前,国外的硅基VDMOS 技术比较成熟,主要公司有MA-COM、Polyfet、ST 等。Polyfet 公司有最高频率达1.5 GHz、输出功率范围为4~400 W 的硅基射频VDMOS产品;ST 公司的硅基VDMOS 产品频率范围为1~250 MHz,最高峰值功率达到1 200 W;MA-COM 公司的硅基VDMOS产品频率范围为DC~1 GHz,输出功率最高达600 W。国内的硅基VDMOS 技术相对比较落后,但也有一定进展,如国内文献报导过的1 GHz、10 W、8 dB 的硅基VDMOS器件[8],以及530~650 MHz、连续波输出功率20 W、增益7.5 dB、效率49%的硅基VDMOS[9]等。

随着通信技术不断朝着超宽带、小型化、低功耗的趋势发展[9],在包括电台应用在内的许多应用领域都需要器件能在较低工作电压下(28 V、12 V 甚至更小)实现宽带、大功率、高增益、高效率的射频输出。本文基于电台应用对宽带、高增益、高效率射频场效应晶体管的应用需求,对标MA-COM 公司某款同指标产品,设计一款工作频率在30~90 MHz 范围内、输出功率大于80 W、功率增益大于13 dB、效率大于60%的高性能宽带射频场效应晶体管。

1 器件设计

1.1 基本原理

功率增益Gp和截止频率fT是描述器件频率特性的两个关键参数[9]:

其中,gm=μnCOXZ(VGS-VT)/L;k 为与寄生参量有关的比例系 数;f0为工作频率;RG为栅电阻;Cgd为栅漏电容;Cgs为栅源电容;Z 为总栅宽;L 为沟道长度。根据以上公式可知,可以通过优化结构和工艺参数提高器件的频率特性,如降低栅电容、缩短沟道长度和减小栅极电阻。

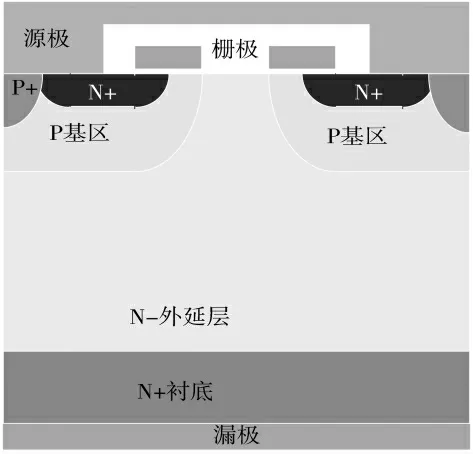

栅电容大小与器件结构密切相关,分栅(split gate)结构可以通过最小化栅漏重叠区域面积有效降低栅氧化层电容COX来减小Cgd[10-11]。图1 所示为分栅VDMOS 剖面结构图,与常规的低频VDMOS 结构相比,分栅结构仅保留了两沟道上方的栅电极,大大减小了栅电极面积,从而得到较小的栅电容。因此,本文采用平面分栅结构降低栅电容,提高器件频率特性。

图1 分栅VDMOS

在缩短沟道长度方面,本文通过采用硼、砷离子注入双扩散自对准技术配合适当的沟道注入剂量和退火时间,可以实现对沟道长度的精确控制;为了减小栅极电阻,通过提高多晶硅栅电极的掺杂浓度和杂质激活率以及采用电阻率较低的栅极材料可以得到较低的栅电阻[12]。

器件的射频输出功率Pout可表示如下[13]:

其中,ID∝μn·Z/L;η为效率,主要与导通电阻Ron有关。根据式(3)可知,在效率一定的前提下,提高工作电压VDS和工作电流ID可以增大器件的输出功率。具体地,可以通过适当增大总栅宽来提高工作电流,增大射频输出功率。

1.2 器件仿真

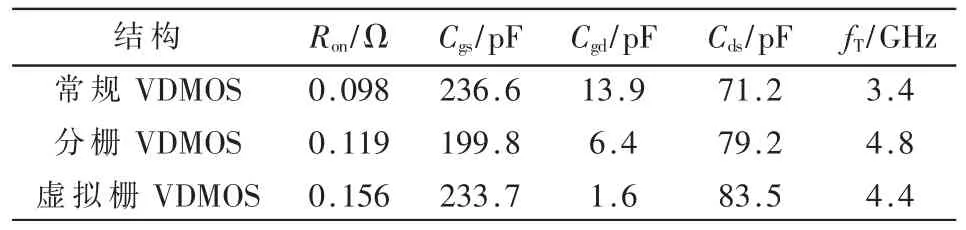

除分栅结构之外,虚拟栅(dummy gate)[14-15]结构也可以有效降低栅电容,但与分栅结构不同的是,虚拟栅结构在两个栅极之间引入和源极短接的虚拟栅电极,在正向漏偏压时,虚拟栅电极会辅助耗尽半导体中的载流子,使得Cgd进一步减小。图2 所示为常规VDMOS、分栅VDMOS 和虚拟栅VDMOS 的电容随漏压变化仿真曲线,表1 为3 种不同结构VDMOS 的仿真参数及仿真值,表中Cgs、Cgd、Cds分别为栅源电容、栅漏电容和漏源电容。

表1 不同结构VDMOS 仿真参数

图2 3 种不同结构电容随漏压变化仿真曲线

通过仿真结果可以看出,虽然虚拟栅结构的Cgd最小,在28 V 工作电压下仅为1.6 pF,但是这种结构的Cgs和Cds均大于分栅结构,在VDS=28 V 时,虚拟栅VDMOS 中的Cgs为233.7 pF,Cds为83.5 pF,fT为4.4 GHz,而分栅VDMOS中的Cgs为199 pF,Cds为79.2pF,fT为4.8GHz,这是因为虚拟栅电极的存在会不可避免地引入额外寄生电容Cgs和Cds,导致fT降低。此外,与常规低频结构相比,由于半导体表面两沟道间积累层的缺失,导致这两种结构的Ron略微增大,常规VDMOS、分栅VDMOS 和虚拟栅VDMOS中Ron分别 为0.098 Ω、0.119 Ω 和0.156 Ω,与常 规 结构相比,虚拟栅结构的导通电阻增大59 %,而分栅结构导通电阻仅增大21%。

缩短栅电极长度LG可以减小栅电容,从图3 中可以直观地看出:减小LG可以有效降低电容Cgs和Cgd,但需要注意的是,栅极长度太短会造成部分导电沟道表面没有栅极覆盖,无法形成反型层,导致晶体管阈值电压VTH迅速增大。因此,需要综合考虑栅电容与阈值电压之间的矛盾关系,折中优化,最终选定LG为1.25 μm,仿真得到器件的转移特性曲线如图4 所示,VTH在3.09 V 左右。

图3 栅电容和阈值电压与栅极长度关系仿真曲线

图4 转移特性仿真曲线

分栅VDMOS 的击穿电压BV 不仅受到外延层浓度和厚度的影响,还受到两个栅极间距离的影响,结合Sentaurus TCAD 仿真优化,选择合适的外延层参数和栅极间距,仿真得到该器件的BV 为96.8 V,可以满足28 V 工作电压的要求,图5 为该器件的击穿特性仿真曲线。

图5 击穿特性仿真曲线

2 射频性能评估

2.1 电性能测试

表2 给出了器件电性能测试结果。测试结果显示,该器件实测击穿电压BV 达到95.5 V,阈值电压VTH为3.2V,导通电阻Ron为0.16 Ω,最大跨导gm为8.9 S,输入电容Ciss、输出电容Coss、反馈电容Crss分别为191 pF、128 pF、10.5 pF,其中Ciss=Cgs+Cgd,Coss=Cds+Cgd,Crss=Cgd,各电性能参数均满足设计要求。

表2 电性能测试结果

图6 为该器件的实测击穿特性曲线,图7 是实测的输出特性曲线。从实测的击穿曲线可以看出,击穿电压的实测值与仿真值拟合良好,说明本文对该器件的电性能分析和设计比较合理,实际的工艺过程控制良好。

图6 击穿特性曲线

图7 输出特性曲线

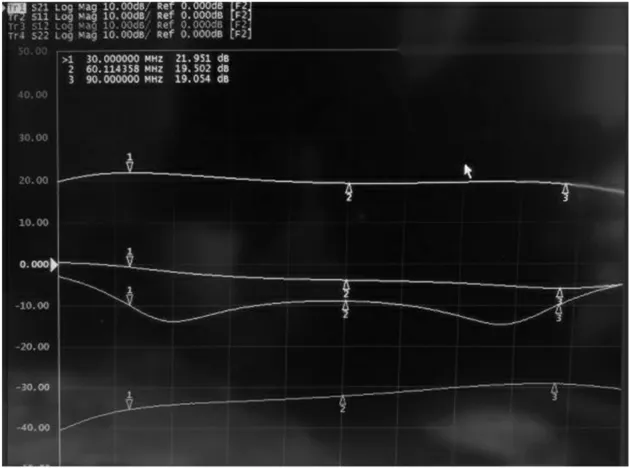

2.2 射频小信号测试

通过小信号模拟可以对器件的射频性能进行初步估计,图8 是该器件及其匹配电路的PCB 测试板。图9为矢量网络分析仪上各频点的S 参数测量曲线,其中,从上至下依次为S21、S11、S22和S12参数曲线。测试结果显示,该器件在VDS=28 V、IDQ=0.2 A 的测试条件下,在30~90 MHz 频段范围内,小信号增益S21大于19 dB,增益平坦度为±0.5 dB,小信号增益满足设计要求,平坦度较好。

图8 PCB 测试板

图9 S 参数测量曲线

2.3 窄带射频性能测试

图10 给出了该器件在f=60 MHz、VDS=28 V、IDQ=0.2 A的测试条件下,其输出功率Pout和功率增益GP与输入功率Pin的关系曲线,图11 为该器件功率附加效率PAE与输出功率Pout的关系曲线。测试结果显示,该器件在60MHz的频点下可以实现Pout=87 W、GP=18.4 dB、PAE=72.4%的优异射频性能。

图10 输出功率和增益与输入功率关系曲线

图11 功率附加效率与输出功率关系曲线

2.4 宽带射频性能测试

宽带射频性能是在VDS=28 V、IDQ=0.4 A 的测试条件下,由两路器件经过功分器合成测得的。图12 为在Pin=1 W时,测试得到的MA-COM 样品晶体管和本文自行研制晶体管的输出功率与频率关系曲线。经过对比可以看出,在30~90 MHz 频段范围内,本文自制晶体管的射频输出功率均大于该样品晶体管,实测输出功率大于60 W。

图12 输出功率与频率关系曲线

3 结论

本文基于标准平面MOS 工艺,采用平面分栅结构,通过优化结构和工艺参数研制出一款工作电压为28 V 的宽带、高增益、高效率硅基射频场效应晶体管。该器件的直流参数符合设计要求,射频性能方面,该器件在60 MHz频点下连续波输出功率可以达到87 W,增益达18.4 dB,功率附加效率达72.4%;在30~90 MHz 频段范围内,小信号增益均大于19 dB,实测输出功率均大于样品晶体管,具有优异的射频性能。