一种双环串联频率综合器的设计

2021-07-28李洪涛

李洪涛

(中国电子科技集团公司第五十四研究所,河北石家庄 050081)

0 引言

频率综合器作为现代电子设备和电子系统的基础,被广泛应用于通信、雷达、干扰、遥控遥测等领域。随着电磁环境越来越复杂,测量精确的要求也日益提高,这就要求频率综合器具有宽频带和小步进的同时具有更低的相位噪声[1]。但是上述各个指标之间会互相影响,因此需要在设计时选择合适的方案来满足系统对各个指标的要求。

1 频率合成技术原理

频率合成技术是将一个基准频率信号变换为所需要的频率信号的技术。目前频率合成的方法可以分为直接频率合成、锁相频率合成和直接数字频率合成三种基本的方式[2]。但是在高指标频率综合器的设计中,一般是通过结合两种或三种频率合成方式的混合频率合成方式来得到高指标频率综合器。

2 方案设计

2.1 方案总体设计

常规的宽带小步进频率综合器一般是通过多环混频方案实现。多环混频方案至少包括一个大步进环与一个小步进环,其中大步进环实现宽带信号输出,小步进环实现小步进输出,通过多环混频可以在保证信号输出相噪极低的同时实现宽带和小步进。但是随着频率的提高,多环混频方案的设计变得越来越复杂,并且受鉴相器指标限制,难以实现极低的相位噪声。

多环混频方案相当于多个环路相加实现宽带,随着输出频带变宽,方案变得极为复杂。在此基础上。本文提出了一种双环串联方案,首先通过锁相环产生一个窄带信号,然后通过倍频及分频,通过锁相环电路将这个窄带信号搬移到全频带上。方案总体框图如图1所示,压控振荡器与窄带信号的倍频信号及分频信号多次混频后产生低频信号作为反馈信号,通过鉴相器与参考信号鉴相后控制压控振荡器锁定。

图1 总体方案框图Fig.1 Block diagram of the overall scheme

首先产生一个窄带信号FIN进入功分器1分为三路,分别产生一次混频信号Fmul1、二次混频信号Fmul2及参考信号FREF。压控振荡器输出信号FVCO经过功分器2后分为三路,其中一路作为输出信号,第二路经过分频器2分频后入鉴相器2,与参考信号进行鉴相,控制压控振荡器预置在需要频率上[3],第三路先与Fmul1进行混频,然后根据输出频率选择与Fmul2进行混频后入滤波器2或者直接入滤波器2,经滤波器2滤波后的信号Fm2入鉴相器1,与参考信号进行鉴相,控制压控振荡器锁定。开关可以根据需要切换为预置电路或锁定环路。

2.2 分支电路设计

Fmul1产生如图2所示。窄带信号经过梳状谱发生器后产生高次谐波信号[4],通过开关选择及滤波器滤波后分别选择出窄带信号的三、四、五、六次谐波,即为Fmul1。

图2 一次混频信号产生电路Fig.2 Primary mixing signal generation circ uit

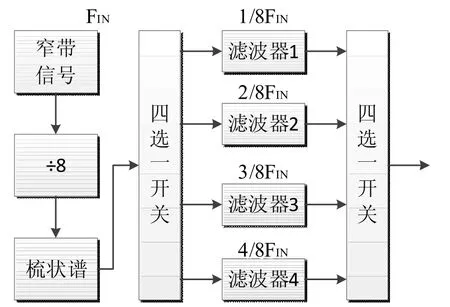

Fmul2产生如图3所示,窄带信号经过八分频后入梳状谱,产生的高次谐波信号,通过开关选择及四路滤波器分别滤波后选择出1/8FIN、2/8FIN、3/8FIN、4/8FIN信号,即为Fmul2。

图3 二次混频信号产生电路Fig.3 Secondary mixing signal generation circuit

窄带信号产生如图4所示,100MHz晶振输出信号经过梳状谱电路后产生100MHz高次谐波信号,通过功分器分为两路。其中一路通过滤波器2将信号中的1400MHz信号滤出,另一路通过滤波器1将3000MHz信号滤出,信号经过DDS分频后输出125±15MHz信号入鉴相器。压控振荡器输出信号与1400MHz信号混频后经过低通滤波器滤波,中频信号入鉴相器与DDS输出信号进行鉴相,鉴相器根据两个信号的相位及频率差值输出相应电压,经过环路滤波器滤波后,控制压控振荡器锁定需要的输出频率上。

图4 窄带信号产生电路Fig.4 Narrow band signal generation circuit

2.3 变频方案设计

由方案易知:

当一中频信号Fm1直接入滤波器2时,可以将Fmul2视为零频率,即:

本方案中一中频及二中频信号均选择差频信号输出[5],则:

通过推导可得:

将N=3、4、5、6及M=0、1、2、3、4代入公式,则可得:

将FIN=1525±15MHz代入公式,可知当k=52、53、54…104时,FVCO输出频率可以覆盖5GHz~10GHz全频段。

3 指标分析

3.1 相位噪声分析

本方案中总相位噪声是由晶振、倍频器、D D S、鉴相器、VCO等引入相位噪声的叠加。

其中,晶振选择超低相噪恒温晶振,其相位噪声可以达到-165dBc/Hz@10kHz。

设PNIN为倍频前信号在频偏10kHz处的相位噪声,则N倍频后输出信号在频偏10kHz处的相位噪声PNOUT为:

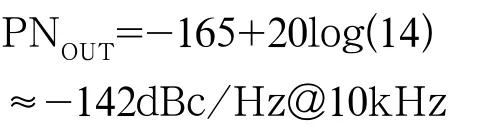

因此1400MHz倍频输出信号相噪为:

由于DDS输入3000MHz参考信号为梳状谱产生,相噪较低,不会对DDS输出信号相噪产生影响,因此仅需要考虑DDS器件产生相噪即可。目前较好的DDS芯片输出频率125±15MHz时相噪可以优于150dBc/Hz@10kHz。

由于窄带信号FIN为1400MHz信号与FDDS信号混频得到,将1400MHz信号与FDDS信号相噪相加,可以得到窄带信号FIN相噪约为-141dBc/Hz@10kHz。

随着信号输出频率增高,信号相噪会恶化,易知当Fmul1及Fmul2输出频率最高时相噪最差。

Fmul1的最差相位噪声为:

PN1=-141+20log(6)≈-125dBc/Hz@10kHz

Fmul2的最差相位噪声为:

PN2=-141+20log(0.5)≈-147dBc/Hz@10kHz

FREF相位噪声为:

-141+20log(1/32)≈-171dBc/Hz@10kHz

考虑到常用的分频器单边带相位噪声一般优于-150dBc/Hz@10kHz,即最终FREF相噪PN3优于-150dBc/Hz@10kHz。

目前常用的鉴相器归一化带内相位本底噪声一般优于-220dBc/Hz@10kHz,则鉴相器2引入的相位噪声为:

PN4=PNfloor+10log(FREF)

=-220+10log(1.54×109/32)

≈-143dBc/Hz@10kHz

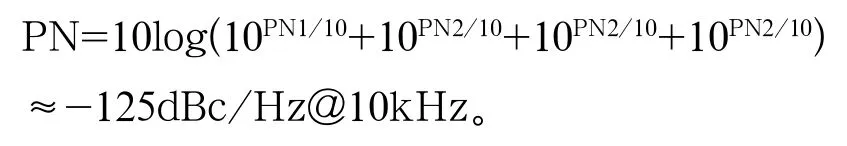

压控振荡器输出信号FVCO的带内相噪为Fmul1、Fmul2、FREF及鉴相器引入的相噪之和,最终输出信号的理论相位噪声为:

3.2 杂散分析

频率综合器中的杂散一般分为近端杂散与远端杂散。

本方案中VCO输出信号经过二次混频后产生的中频信号入鉴相器进行鉴相,经过环路滤波器进行滤波可以有效滤除远端杂散,结合空间屏蔽、开关隔离、电源滤波和滤波器过滤来抑制,产生的杂散非常低,杂散抑制可以达到75dBc以上。

近端杂散主要是鉴相泄露杂散[6]和DDS产生杂散。其中鉴相泄露杂散可以通过设计合适的环路滤波器来抑制,可以保证75dB以上。由于DDS输入频率为3000MHz,输出频率为110MHz~140MHz,此时DDS分频比N>21,因此产生的杂散非常低,不会造成影响。

综上所述,本方案的最终杂散抑制可以达到75dBc。满足系统要求。

3.3 步进分析

本方案中的步进通过更改D D S的频率来实现。目前DDS已经可以实现64位分频。

由于DDS的参考信号频率为3000MHz,假设DDS调谐控制字64位,则方案中FIN最小步进为:

3000×106Hz/264≈1.6×10-10Hz。

由于VCO输出信号频率FVCO=FIN/32×(2k+1) (k=39、40…104),则VCO输出信号最小频率步进为:

1.6×10-10Hz/32×(2k+1)≈1×10-9Hz

4 指标分析

通过理论计算可以知道本方案输出信号频率10GHz时可以实现-125dBc/Hz@10kHz的相位噪声。而通过直接倍频方式产生10GHz信号的理论相位噪声为:

-165+20log(100)=-125dBc/Hz@10kHz。本方案输出信号的相位噪声在理论上已经与直接倍频方式相等。

继续继续分析可知,本方案的相位噪声为Fmul1、Fmul2、FREF及PNPD之和。其中,

Fmul1相噪优于-125dBc/Hz@10kHz;

Fmul2相噪优于-147dBc/Hz@10kHz;

FREF相噪优于-150dBc/Hz@10kHz;

PNPD相噪优于-143dBc/Hz@10kHz。

通过比较可知本方案主要相噪为Fmul1产生,而Fmul1相噪由1400MHz梳状谱信号相噪决定,即主要受晶振相噪影响。如果更换指标更好的晶振,则本方案的相位噪声指标还可以进一步提高。

5 结语

本文提出了一种双环串联的宽带小步进低相噪频率综合器的设计方案,并在方案的基础上进行了理论分析。可以看到该方案结构简单,实现难度小,在保证宽频带和小步进的同时其相噪已经可以与直接频率合成方案的指标相当,具有良好的应用前景。