一种基于MLVDS的SPI通信链路设计

2021-07-28钱小东宣浩葛鹏

钱小东 宣浩 葛鹏

(1.中国电子科技集团公司第三十八研究所,安徽合肥 230088;2.孔径阵列与空间探测安徽省重点实验室,安徽合肥 230088)

0 引言

串行外围设备接口SPI(Serial Peripheral Interface)作为一种成本低、应用简单的全双工同步通信总线,主要应用于中等距离中等速度条件下的通信,其具有严格的时序逻辑,分为主设备和从设备,常用于板内嵌入式处理器与外围设备芯片之间的通信,且由于其硬件结构简单、协议灵活以及可靠性高的特性,具有良好的可扩展性[1]。MLVDS作为多点LVDS,可以驱动多个收发器实现总线的互联应用,其具有高传输速率、低功耗和低噪声的特点。

在某星载控制链路中,基于MLVDS技术使用FPGA设备作为SPI通信主机节点向多个ARM或FPGA实现的从机节点设备发送控制命令,主机发送的时序与标准SPI严格的时序逻辑唯一的区别就是时钟连续,因而对于某内置ARM Cortex-M3内核的MCU作为从机节点来说,无法直接应用内置的SPI硬核接收总线数据,本文提出了一种软件方法处理连续时钟下SPI从机可靠通信的问题。

1 接口设计

本文设计的通信接口组件应用基于MLVDS链路层标准的SPI通信接收上级主机发送过来的频率控制码,通信主机使用 FPGA工作于主机方式,总线中挂载多个从机,存在混合使用FPGA和ARM作为从机接收主机发送控制数据的情况,由于只发不收单向通信,所以占用主机FPGA板2+N个通用管脚,其中N为从机数量,如图1所示为基于SPI总线的一主多从通信的示意图,参与数据传输的引脚包括时钟引脚SCK,主出从入引脚MOSI,以及片选有效引脚CS。MOSI为从机节点接收的数据输入,SCK为从机节点的串行时钟输入,CS选择MCU一个普通的GPIO与主器件相应的唯一片选信号相连,而标准SPI通信接口的片选管理引脚NSS释放为GPIO另用。

图1 FPGA SPI引脚配置为master与多个SPI slave节点通信模式图Fig.1 FPGA SPI pin configuration as master communication mode diagram with multiple SPI slave nodes

根据系统用元器件统型需要,所使用的处理器芯片采用系统级封装(System in Package,SIP)技术以MCU及其外设为核心构成的一款集数据采集、处理、传输的信号处理系统,电路内部集成电源管理芯片和振动器电路。其中MCU采用ARM3内核的STM32F4系列芯片完成高密度,小体积化集成,具有丰富的通讯接口以及I/O口[2]。MLVDS接收器选用国产中电科58所的宇航等级产品JRMLVD201,兼容TI公司工业级SN65MLVD201产品。

2 软件处理

通信主机使用FPGA作为主机产生如图1所示时序,时钟连续,在时钟的下降沿发送片选逻辑以及数据,所发送数据高位在前低位在后,数据字节间无间隔,数据帧长无限制。作为通信总线节点之一的通信接口组件只接收主机发送给本节点的串行控制命令并执行相应操作。根据通信接口设计,借助于MCU内置的SPI硬核资源实现SPI通信。

标准的SPI总线时序可以通过设置SPI_CR1寄存器中串行同步时钟极性(CPOL)和相位(CPHA)两位形成四种组合[3],串行同步时钟极性决定了串行同步时钟空闲状态时候的电平状态,CPOL设为0,则串行同步时钟的空闲状态为低电平,否则为高电平;相位则决定有效数据的采样时机,CPHA设为0,则在串行同步时钟有效的第一个跳边沿采样数据,否则在串行同步时钟的第二个跳变沿采样数据,SPI通信的主机和从机时钟相位和极性应该设为一致。

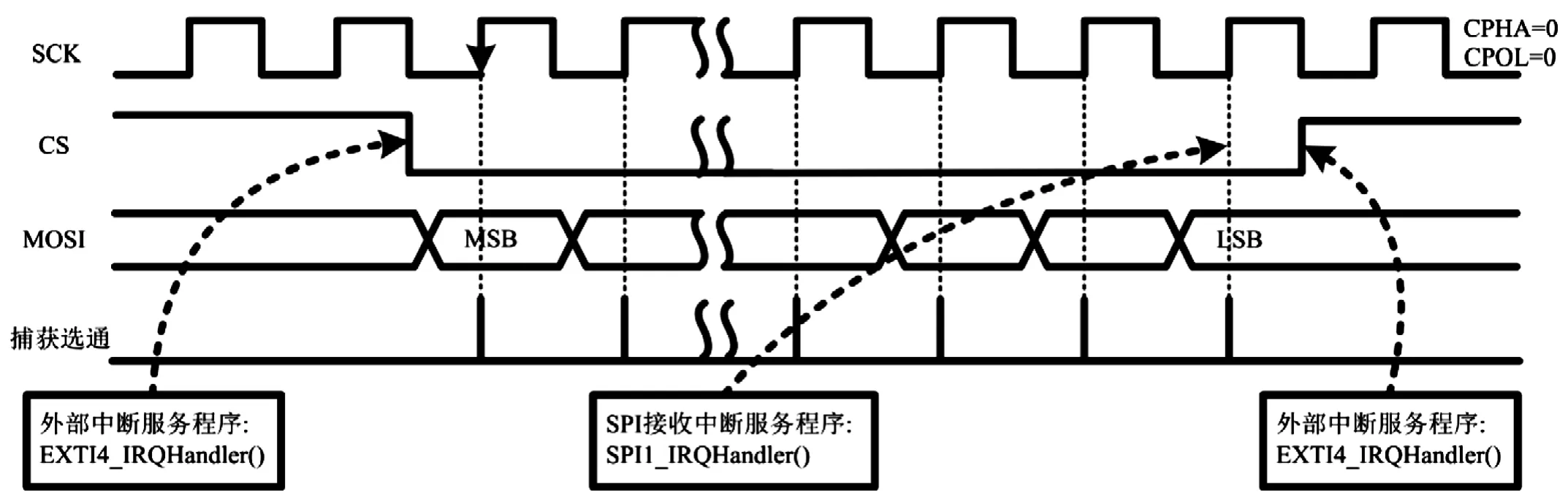

在传统的SPI通信从机模式配置中,从SCK引脚上接收主机节点的串行时钟,在主机节点发送时钟前需要使能SPI从机节点,且在主时钟的第一个边沿来之前或者正在进行的通信结束之前,从机节点的数据寄存器需要准备就绪。在使能从机节点和主机节点之前,必须将通信时钟的极性设置为空闲时的时钟电平。然而由图1可见,SPI通信主机节点发送的时钟信号在空闲状态下并非处于恒高或者恒低电平,所以本文设计如下处理方法来实现非连续时钟条件下SPI从机节点的接收通信功能,如图2所示为SPI1通信部分软件设计流程图:

图2 SPI总线通信时序Fig.2 SPI bus communication timing

图3 SPI通信从机节点配置及软件处理流程Fig.3 SPI communication slave node configuration and software processing flow

2.1 初始化流程

(1)使能所使用的GPIO引脚时钟功能,并设置SPI1相关引脚为复用功能;

(2)通过配置SPI1_CR1寄存器初始化SPI1,分别设置为半双工串行收方式,从机模式,8位数据格式,同步串行时钟在空闲状态设为低电平,并在串行同步时钟有效的第一个跳变沿采样数据,从机节点选择(NSS)引脚设置为软件控制,SPI波特率预分频值选择2,数据传输顺序高字节在前且MSB位在前,CRC校验多项式设为7。初始化操作之后禁用SPI1并不使能SPI1接收中断;

(3)根据硬件设计,使用PE4作为SPI通信片选信号,使能PE4引脚时钟并配置为输入模式,随后开启SYSCFG时钟,并设置PE4口与EXIT4中断线映射,然后设置中断线4上的中断模式为任意电平(上升沿或下降沿)触发,并使能中断线。最后,设置中断分组并使能中断。

2.2 外部中断服务程序

外部中断服务处理过程主要是判断中断线4发生中断的跳边沿类型,如果是下降沿中断,则说明SPI主机节点片选本从机节点并开始发送控制命令,所以立即使能SPI1时钟,启动SPI1并使能SPI1接收中断RXNE;如果是上升沿中断,则说明SPI通信结束,此时执行上述步骤(2)中的SPI1初始化流程,将内置的SPI1硬核资源恢复初始态。

2.3 SPI1接收中断服务程序

根据SPI初始化配置,在片选信号低电平有效期间,每8个时钟的最后一个采样时钟边沿出现时,RXNE位将置1,产生中断,移位寄存器中接收的数据字节被拷贝到接收缓冲区中,读取SPI_DR寄存器将SPI接收中断标志位(RXNE)清零。SPI接收中断服务程序中读取接收缓冲区中一个字节寄存器并退出中断服务程序。

传统的SPI通信设计时,SPI从器件的移位寄存器受时钟驱动将采样到的数据传输到接收缓冲区,而连续时钟条件下由于时钟抖动和传输线路的影响,SPI主机FPGA产生的时序中片选信号CS的跳变沿与时钟SCK存在相位的不确定性会导致数据传输不正常,因此上述SPI通信的软件设计方法的关键就是仅在片选信号为低电平有效期间使能SPI从器件,使用SPI从器件硬核接收控制命令,并且在片选信号上升沿触发复位SPI以消除最后一个时钟沿引入的移位偏差。

3 结语

SPI作为一种常用的串行通信标准,众多的MCU中均内置SPI接口,在层出不穷的嵌入式系统中不可避免地面临与其他通信系统兼容的应用需求,因此通过软件方法拓展SPI接口的应用具有重要的意义。本文基于MLVDS链路层标准的SPI总线接口提出的软件处理方法可以很好地解决连续时钟时序下的SPI半双工通信,灵活、稳定和实时性要求满足设计需要,而且在硬件实现上简单可靠,并且兼容传统非连续时钟应用场合,可应用于后续类SPI通信总线的工业或者航天嵌入式系统中。