一种新型SPI NAND控制器设计∗

2021-07-16蔡声镇

陈 亮,蔡声镇

(1.福州理工学院计算与信息科学学院,福建 福州 350506;2.福建师范大学数学与信息学院,福建 福州 350117)

闪存介质(NAND Flash)因其低延时、高并行、低能耗、体积小等特点受到了广泛关注,基于闪存介质构建的闪存存储系统是当前的研究热点,构建形式多样[1]。存储系统主要由主机、存储设备构成;闪存设备主要由闪存介质、闪存控制器两部分构成。Open-Channel SSDs,Denali 等为新型的闪存控制器架构[2],根据应用需求,将闪存转换层(flash translation layer,FTL)、垃圾回收等功能从存储设备移植到主控端实现,从而提升存储系统整体性能。

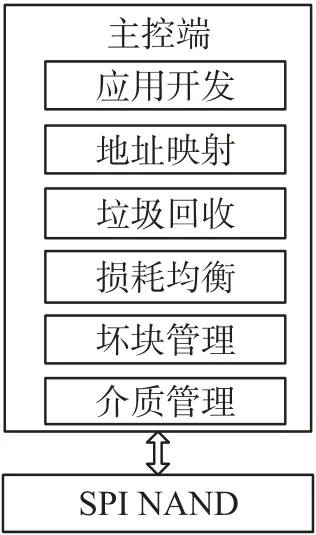

SPI NAND Flash 为嵌入式领域的闪存设备,主要用于嵌入式系统的代码存储和数据存储,其主流的存储容量为1 Gbit/2 Gbit/4 Gbit,典型的传输速率为30 Mbit/s,50 Mbit/s,80 Mbit/s 等[3]。图1 所示为传统的SPI NAND 存储系统,闪存介质相关的介质管理,坏块管理,地址映射等功能均放在主控端实现。该架构的优点是简化SPI NAND Flash 内部控制器,不足是存储容量小、传输速率低、不同厂商协议命令复杂繁多不统一。随着物联网技术的迅猛发展和人工智能等复杂计算或边缘计算的引入,嵌入式设备对性能和存储容量的需求呈现大幅增长。如何实现大容量、高速率和简化及统一协议命令,已成为SPI NAND Flash 需要急迫解决的问题。

图1 传统SPI NAND 存储系统

本文借鉴Open-Channel SSDs 的设计思想,提出了一种新型SPI NAND 控制器的设计方法,针对SPI NAND 存储系统架构和控制器软件进行优化设计[4],可实现较大幅度提升上述主流SPI NAND Flash 在存储容量、传输速率和主控命令复杂度等方面的性能指标。

1 系统架构设计

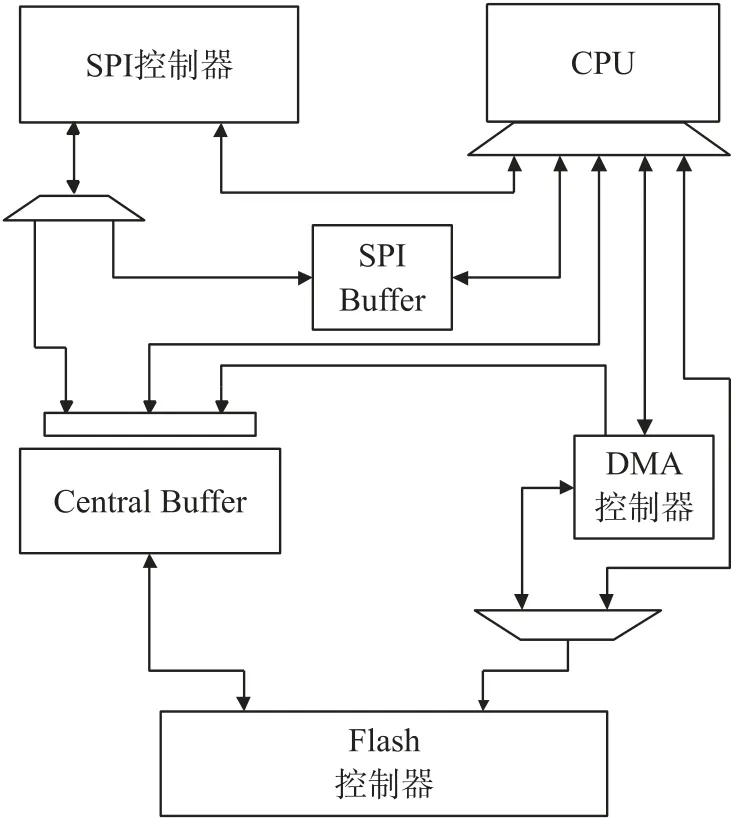

主控端处理器性能和内存资源都优于SPI NAND 控制器,为了高效实现主控端的闪存介质相关功能,在系统架构设计上,需要对SPI 接口和Flash 闪存接口进行硬件加速设计。同时主控端不再考虑闪存介质的特性,可以简化并统一SPI 接口传输指令。对控制器的功能和性能进行合理分布,使用模块化设计理念,整个架构分为前端、FTL、后端三个模块,模块之间通过32 位AXI 总线连接,每个模块处理各自任务,流水作业,形成高效紧凑的SOC 系统,见图2。

图2 SPI NAND 控制器顶层架构

前端模块主要负责与主机的接口指令协议处理和数据在Central Buffer 和主机之间高效传输。FTL 模块主要由CPU 实现主控端的闪存介质相关功能,比如地址映射、垃圾回收、损耗均衡等。后端模块主要根据FTL 模块的地址映射算法,实现Flash 颗粒管理和数据在Central Buffer 和Flash 颗粒之间高效传输。

2 功能模块设计

2.1 SPI 控制器设计

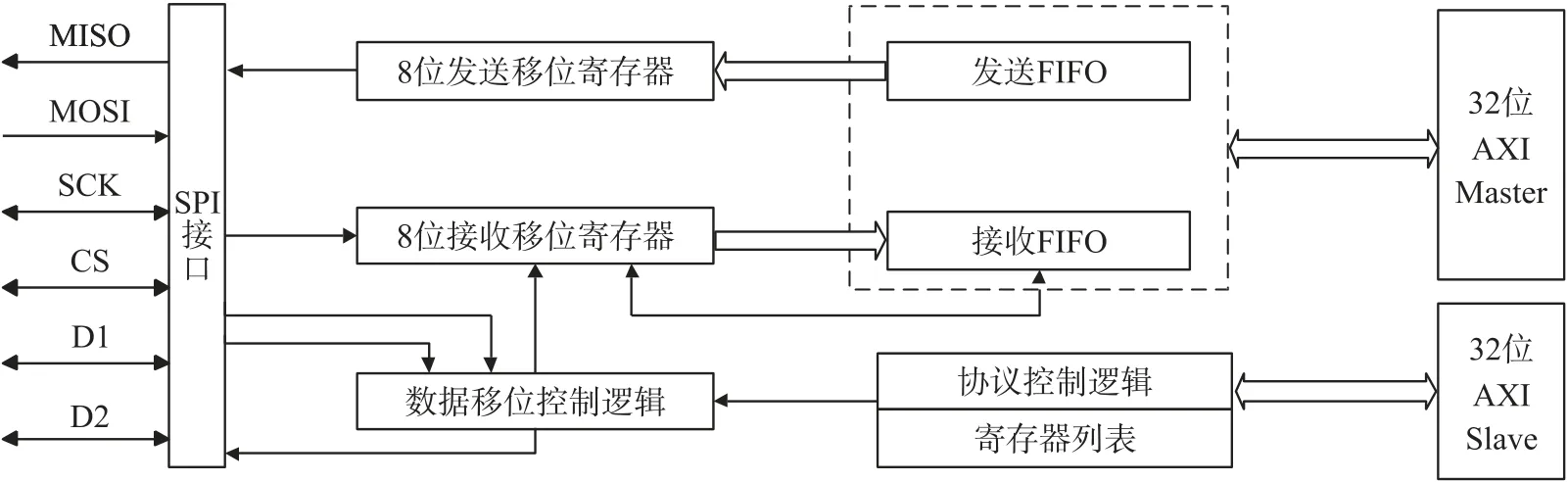

SPI 接口指令简化为数据传输和控制指令,在传统SPI 控制器基础上[5-6],实现了协议控制逻辑,将命令解析软件功能通过硬件来实现,加速SPI 接口指令处理能力。协议控制逻辑格式化硬件解析SPI 接口命令,区分指令类型,提取指令中地址和数据长度等信息,并按照自定义格式传递给处理器。

图3 所示SPI 控制器框图,SPI 控制器通过32位AXI Master 总线与SOC 系统连接,采取DMA 方式进行数据的高效传输;通过32 位的AXI Slave 总线和SOC 系统连接,支持软件配置SPI 控制器。灵活配置SPI 接口工作在标准模式(1 bit 传输),双线模式(2 bit 传输),四线模式(4 bit 传输);工作模式可在主设备/从设备模式切换。

图3 SPI 控制器

2.2 Flash 控制器设计

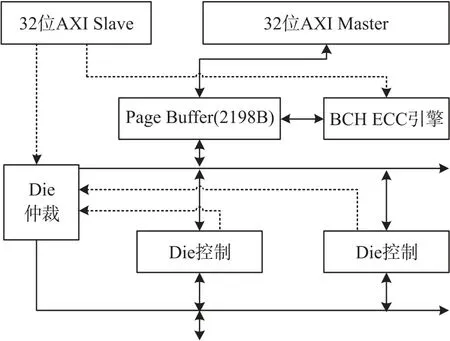

传统的SPI NAND 存储系统,对Flash 颗粒的介质管理通过主机软件来实现。通过硬件方式实现Flash 管理,可降低对处理器性能要求,提高Flash 颗粒读写链路的吞吐量。尤其将BCH 纠错算法,采用硬件引擎实现,降低纠错运算延迟,提升Flash 读操作效率。

Flash 控制器的主要功能是管理Flash 颗粒,完成对颗粒的reset、erase、read、write 操作。图4 为Flash 控制器框图,主要由Page Buffer,BCH ECC 引擎,die 控制逻辑,die 仲裁逻辑,以及两组32 位的AXI 总线接口构成。BCH ECC 引擎为Flash 控制器的核心部分,设计为8 bit/512 byte 的纠错能力,支持SLC 和部分MLC 颗粒[7],为了提升Flash 控制器的性能,采用两个die 控制逻辑,将读写Flash 颗粒的命令进行并行化设计,每一个die 控制逻辑对应映射到颗粒中的一个die,并通过die 仲裁逻辑进行调度操作[8]。

图4 Flash 控制器

2.3 Central Buffer 的设计

Central Buffer 模块作为数据缓存,用于SPI 控制器和Flash 控制器之间大批量数据交互,并为控制器软件实现地址映射,均衡算法,垃圾回收等功能提供硬件基础。灵活的Central Buffer 设计,对控制器整体性能起到关键作用。其采用双口RAM 结构设计,分别拥有A 和B 两组独立读写接口,A 端口与SPI 控制器同频,由SPI 控制器、CPU、系统DMA共享;B 端口与Flash 控制器同频,由Flash 控制器使用(见图2)。

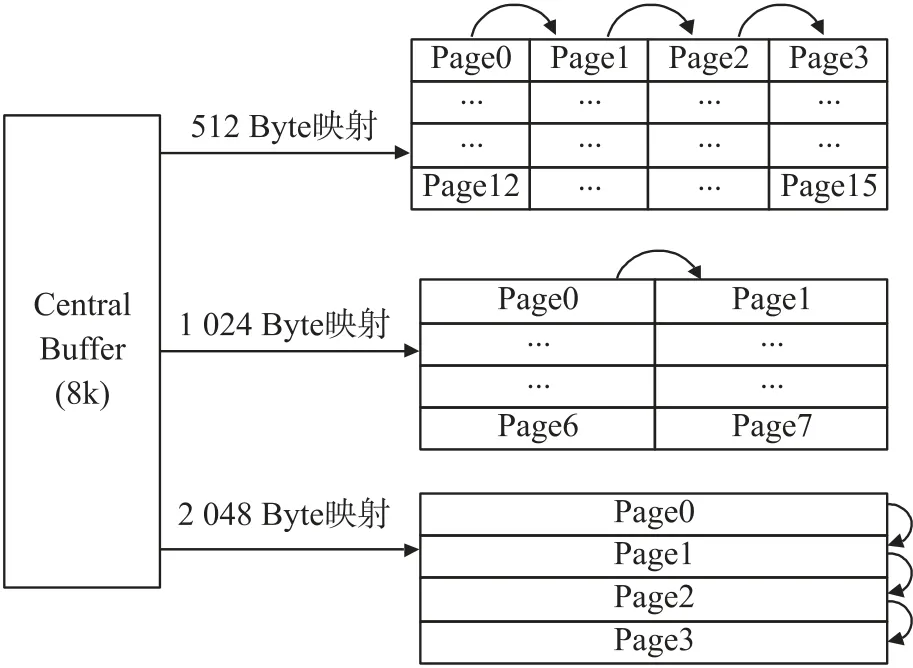

考虑SLC 和MLC 颗粒的特性,其Page 一般为512/1 024/2 048 字节。嵌入式设备的文件系统一般以sector(512 字节)为最小的单元。根据颗粒和文件系统的需求,Central Buffer 的容量设计为8 kB,将Central Buffer 按照512/1 024/2 048 字节的页进行灵活划分,采用链表的数据结构进行调度管理[9],如图5 所示。

图5 Central Buffer 映射

2.4 系统带宽设计

SPI 协议的端口时钟SCK 范围为10 MHz~104 MHz,支持标准模式和双线、四线、八线模式,端口传输速率从10 Mbit/s 到最高832 Mbit/s[10]。MLC 和SLC 颗粒采用ASYNC 和ONFI1.2 协议,支持异步模式和同步模式,同时支持NV-DDR 技术,即允许颗粒采用双沿触发采样数据的技术,端口传输速率从10 Mbit/s 最高可达100 Mbit/s[8]。

考虑对未来高性能的需求,将SPI 端口的最高传输速率定义为8 线模式,驱动时钟为104 MHz,则其传输速率为104 Mbit/s。Flash 端口的最高传输速率定义为NV-DDR 的模式2[8],其传输速率为100 Mbit/s。SPI 端口和Flash 端口的速率是匹配的。对于控制器内部系统互联的AXI 总线,采用32 bit 位宽和50 MHz 时钟,则AXI 总线的传输速率为200 Mbit/s,可满足线速的设计要求。

2.5 软件设计

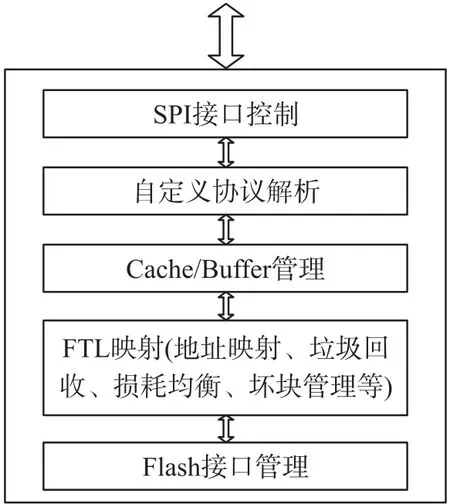

通过SPI 控制器和Flash 控制器的硬件加速功能,架构上的CPU(32 位RISC 处理器),在不降低性能条件下,实现对Flash 颗粒相关的复杂管理移植,把SPI NAND 抽象为类似RAM 的访问模式,屏蔽颗粒底层的复杂信息;同时给嵌入式设备主控提供统一的指令协议,从而达到简化嵌入式主控的驱动设计。SPI NAND 控制器的软件架构如图6所示。

图6 软件功能

控制器内的CPU,实现SPI NAND 存储系统的核心功能,包括对SPI 接口的控制,自定义协议的解析处理,Cache/Buffer 的管理,算法的映射,NAND Flash 的管理等功能。尤其是FTL 的算法映射功能[11],包含地址映射[12],垃圾回收[13],损耗均衡[14]和坏块管理。

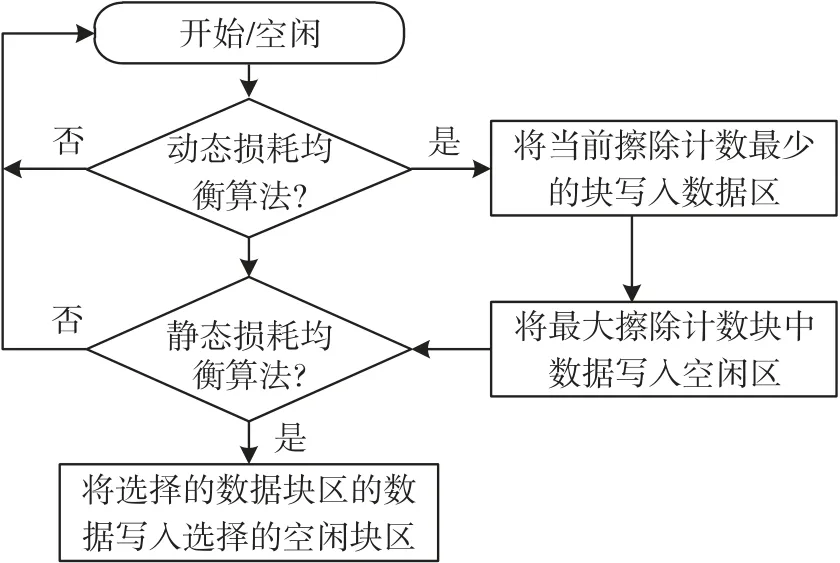

以损耗均衡为例,在SPI NAND 使用过程中,存在用户数据及其访问行为冷热不均,导致颗粒一些物理块长期不被使用,而另一些物理块被频繁使用的情况,长此以往将导致某些块提前坏掉,严重影响SPI NAND 的寿命。损耗均衡通过软件监控颗粒上每个块的擦除次数以及块上数据的存入时间,然后控制所有的擦除次数在平均擦除次数附近偏移,一旦超过设定的最大偏移值,则该块闲置不用。损耗均衡按照算法执行的系统空间分布情况,可以分为动态损耗均衡[15]和静态损耗均衡[16],通过两种均衡算法的结合,SPI NAND 中的物理块均衡使用,提高使用寿命。算法流程如图7 所示。

图7 损耗均衡流程

3 性能测试与分析

3.1 测试环境搭建

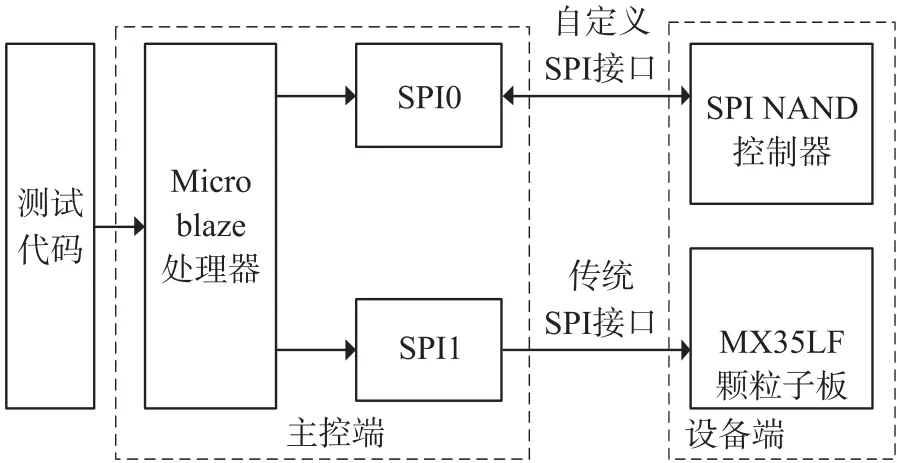

为了验证本文SPI NAND 控制器的性能,采用工业界最主流和具有代表性的旺宏公司的SPI NAND 颗粒MX35LF[10],在FPGA 开发板搭建了性能测试平台,如图8 所示,由主控端、设备端构成。主控端由一块Xilinx 公司的Artix-7 开发板实现,为了尽量消除主控端软硬件对测试的影响,采用两组完全一样的SPI 接口,接口SCK 时钟均工作在50 MHz,Microblaze 处理器工作在200 MHz。设备端由另外一块Artix-7 开发板和MX35LF 颗粒子板构成,SPI NAND 控制器通过Verilog 代码设计和验证,烧写到另外一块Artix-7 开发板。SPI0 支持主/从设备兼容模式,通过软件实现自定义协议,通过改进型SPI 接口和实现了SPI NAND 控制器的FPGA 开发板相连接。SPI1 支持主设备模式,通过传统SPI接口和MX35LF 颗粒子板相连。根据MX35LF 的数据手册,在读取数据时,MX35LF 颗粒Trd 为25 μs,在写入数据时,MX35LF 颗粒Tprog 设置为320 μs。整个测试平台的测试代码均运行在Microblaze 处理器上。

图8 测试平台

3.2 控制指令

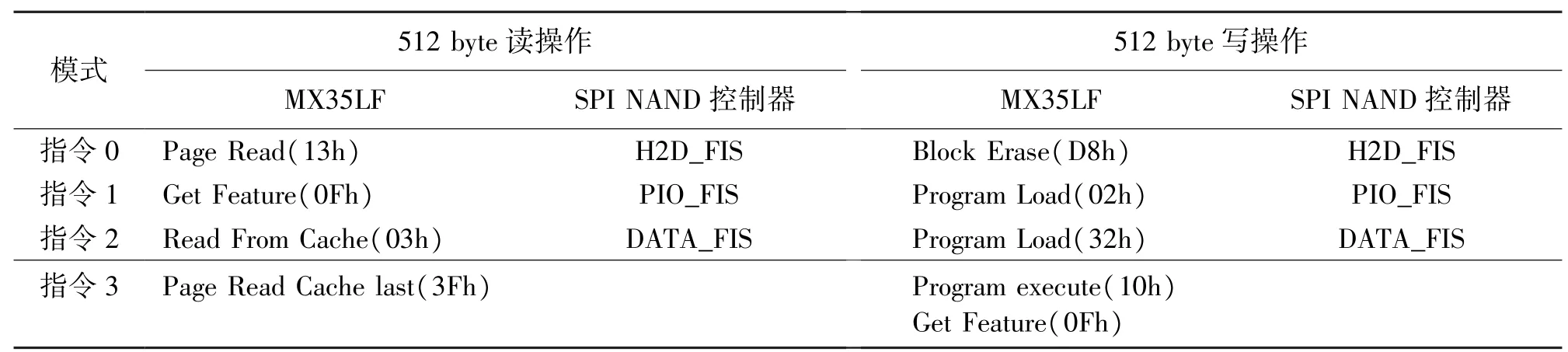

在SPI NAND 控制器和MX35LF 进行读写的对比测试过程中,同样的读操作,MX35LF 需要4 条指令完成,不同的读方式,还需要额外6 条指令;同样的写操作,MX35LF 需要4 条指令完成,不同的写方式,还需要额外2 条指令,而SPI NAND 控制器的读写操作是一致的,只需要支持2~3 条指令,明显简化并统一了主控端的驱动。相关的指令比较如表1所列。

表1 指令系统比较

3.3 存储容量

Flash 控制器的寻址范围是决定Flash 存储器存储容量的关键指标。MX35LF 的寻址位宽为24 bit,同时最小粒度为1 字节;本文的SPI NAND 控制器寻址位宽为28 bit,最小粒度为512 字节,支持的存储容量是MX35LF 的213倍,通过Flash 控制器并行连接多个die 的方式,可以支持高达128 GB 的存储容量。

3.4 传输速率

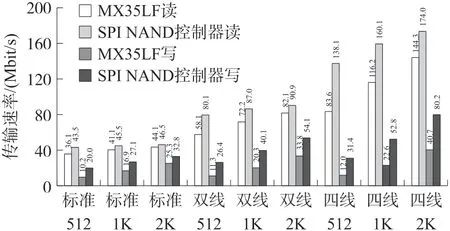

设置SPI0 和SPI1 的SCK 为50 MHz,对SPI NAND 控制器和MX35LF 分别进行读写数据测试,数据的粒度分为512 byte、1K、2K 三个档次,SPI 分别配置为标准(50 Mbit/s)、双线(100 Mbit/s)和四线(200 Mbit/s)模式,图9 所示为读数据和写数据的性能比较,显然存在如下规律:

图9 性能比较

(1)由于读写数据时,每次传输的命令长度是固定的,随着传输数据长度变长、传输线数变多,命令所占传输时间比例降低,因此有效数据传输速率随数据长度提升。

(2)MX35LF 部分命令不能通过改变线数实现并行传输,随着传输数据长度变长,自定义存储设备传输速率的优势越明显。

(3)对于写操作,由于NAND Flash 颗粒特性决定了Tprog 时间比较长,而且无法进行并行写操作。SPI NAND 控制器采用了Central Buffer 的设计方法,以及Flash 控制器支持双die 引擎,支持对NAND Flash 颗粒的并行操作,整体性能比MX35LF 提升一倍左右。

4 结论

本文介绍了一种新型的SPI NAND 控制器的设计和实现,重点描述了SPI NAND 控制器的架构设计以及SPI 控制器、Flash 控制器、Central Buffer 的设计和软件设计。通过测试验证,与当前主流Flash存储设备进行性能比对,在读写数据方面效率获得显著提升。证明了架构的合理性和高效性。