多工作模式的刷新成像系统

2021-07-14刘金国孔德柱陈佳豫

李 波,余 达,刘金国,孔德柱,梅 贵,陈佳豫,赵 莹

(中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033)

1 引 言

大容量SRAM型现场可编程逻辑器件(Field Programmable Gate Array,FPGA)功能强大,在空间成像领域如空间监视、遥感成像中有广泛的应用[1-3]。由于复杂的空间辐照环境和SRAM型FPGA自身的结构工艺,该类器件在轨易受单粒子翻转效应(Single Event Upset,SEU)影响,导致成像功能异常,在成像探测器上电配置期间出现翻转有损坏器件的风险,需要进行辐射加固。常见的SEU加固措施包含三模冗余、纠错编码、局部重配置和配置刷新等[4-6]。其中三模冗余资源占用率高,长时间工作可能导致故障累积而失效,适用于逻辑关系故障;纠错编码占用资源更少,编码简单时检测和纠错有限,编码复杂时会降低数据传输速率,适用于BRAM翻转故障;动态重配置主要针对器件发生的永久物理故障,而配置区受SEU的影响能通过刷新方式解决,配置期间不能工作[7-10];刷新技术[11-14]通过将正确的配置帧信息写入FPGA可以较好地修复SEU。刷新方法常使用对辐照不敏感的反熔丝FPGA对刷新过程进行控制,但软硬件设计复杂。另一种刷新方法是使用专用的定时刷新芯片,设计难度和复杂度可大幅降低[15]。

上海复旦微公司的刷新芯片JFMRS01RH,采用SMIC 0.18 μm CMOS工艺和DICE设计加固方法,具有自身可靠性高、抗辐射能力强,可以定时检测FPGA的SEFI状态并刷新FPGA,削减单粒子的累积效应。该芯片支持可编程只读存储器(PROM)、SPI FLASH、异步NOR FLASH存储器件,提供对异步NOR FLASH、SPI FLASH的编程、全芯片擦除、扇区擦除、数据校验、数据回读功能,同时提供对PROM的数据回读功能。JFMRS01RH支持复旦微电子公司研制的JFM4V系列和JFM7V系列FPGA器件,以及Xilinx公司主流FPGA[16]。该器件通过串口即可实现复杂的操作,但其串口不支持菊花链工作方式,而且波特率为固定的115.2 bit/s,不可调整。若刷新成像系统中每片FPGA和刷新芯片都各配置一组串行总线,则整个刷新成像系统的电缆数量庞大;若使用FPGA对刷新芯片串口控制,则可能由于二者的相互控制陷入工作不正常的死循环。该刷新芯片应用不方便的另一方面,是在器件加电后就立即启动FPGA配置操作,而FPGA由于配置过程电流大通常采用分步上电方式,从而容易出现刷新芯片控制下的FPGA加载失败。若完全依靠刷新芯片进行成像系统控制,当刷新芯片出现损坏或者工作异常,则整个成像系统失败;在调试过程中出现异常,也难进行问题定位,因此需要进行多工作模式的设计。最后,刷新成像系统需要在轨软件重注功能,可根据在轨的应用需求,实现刷新成像系统的功能重构。

2 多工作模式的刷新成像系统设计

刷新成像系统包含多组刷新成像单元和主控。刷新成像单元包含刷新芯片、FPGA、flash、PROM组、总线驱动器和成像探测器。flash直接与刷新芯片相连,受刷新芯片控制,用于接收待更新的配置数据。PROM与FPGA之间、FPGA与刷新芯片之间采用总线驱动器实现通路的切换。FPGA产生成像探测器工作所需的相关工作时序,并接收成像探测器输出的图像数据。主控通过逻辑控制信号和菊花链结构的串行422总线对各成像单元刷新配置过程进行控制。然而,串行422总线直接与FPGA相连,FPGA通过解析主控的422命令,产生响应的控制命令并将接收到的配置数据通过刷新芯片的串口写入与刷新芯片相连的flash中。

2.1 刷新芯片JFMRS01RH电路

在轨刷新成像系统如图1所示,刷新芯片JFMRS01RH内部结构如图2所示。可通过外部的控制信号或者串行通信接口进行刷新芯片内部配置寄存器的状态控制,刷新芯片的内核可外部供电,而与可选择使用内部的LDO供电;刷新芯片可通过读取FPGA内部的配置信号,与指定的配置数据源进行对比,进行位流解析,产生相应的控制;也通过串行接口,接收重注程序,编程写入外部flash中。

图1 在轨刷新成像系统Fig.1 On-orbit refresh imaging system

图2 刷新芯片JFMRS01RH内部结构Fig.2 Internal structure of refresh chip JFMRS01RH

2.2 成像处理电路

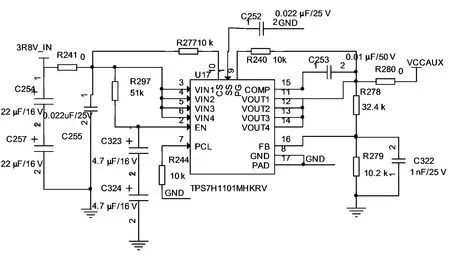

成像处理电路中FPGA采用Xilinx公司的V5系列FPGA XQ5VFX100tff1136M,最大可用680个管脚,内部包含8 208 kbit的块RAM资源和256个DSP48E资源[17]。成像处理需要多种供电电源,为尽量降低成像电箱的总功耗,成像处理拟采用3种供电电源。此部分主要采用TI公司的TPS7H1101MHKRV进行供电(图3),其中由于FPGA内核电流大,采用VPT公司的点负载DS-DVPL0510S-5.0供电;外部接口电路和刷新成像部分采用LS883进行供电。

图3 TPS7H1101MHKRV供电电路Fig.3 Power supply circuit based on TPS7H1101MHKRV

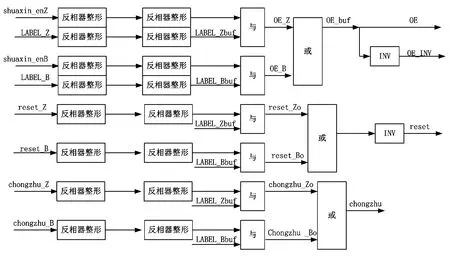

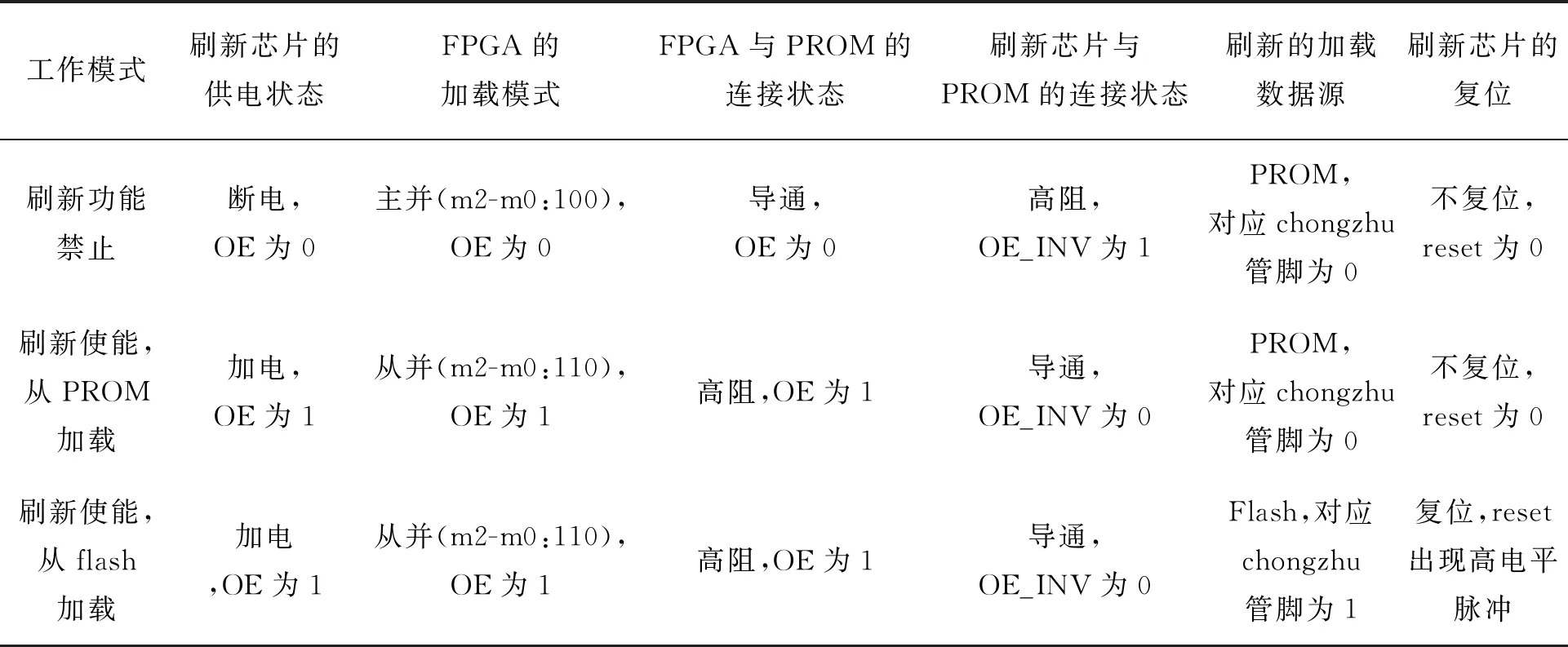

刷新成像成像系统具有3种成像工作模式,如图4和表1所示:

图4 刷新成像控制逻辑流程图Fig.4 Refresh imaging control logic flow chart

表1 3种工作模式下的电流及状态Tab.1 Current and status in three working mode

(1)刷新功能禁止模式。主控发出的控制信号使刷新使能处于无效的低电平。FPGA为主并工作模式,直接从PROM加载数据,刷新芯片的供电处于禁止状态。

(2)从PROM加载的在轨刷新模式。刷新芯片的供电输出使能,主控发出的控制信号刷新使能处于有效的高电平,重注使能处于无效的低电平。FPGA为从并工作模式,加载过程受刷新芯片控制,刷新芯片的串口是受FPGA控制,通过外部复位,刷新芯片的加载配置信号取决于外部的管脚电平信息,刷新芯片的管脚电平为默认从PROM加载。

(3)从flash加载的在轨刷新模式。刷新芯片的供电输出使能,主控发出的控制信号刷新使能处于有效的高电平,重注使能处于无效的低电平。FPGA为从并工作模式,加载过程受刷新芯片控制,刷新芯片的串口是受FPGA控制,通过外部复位,刷新芯片的加载配置信号取决于外部的管脚电平信息,刷新芯片的管脚电平为从修改了程序的flash加载。

3 测试结果

3.1 多工作模式加载结果

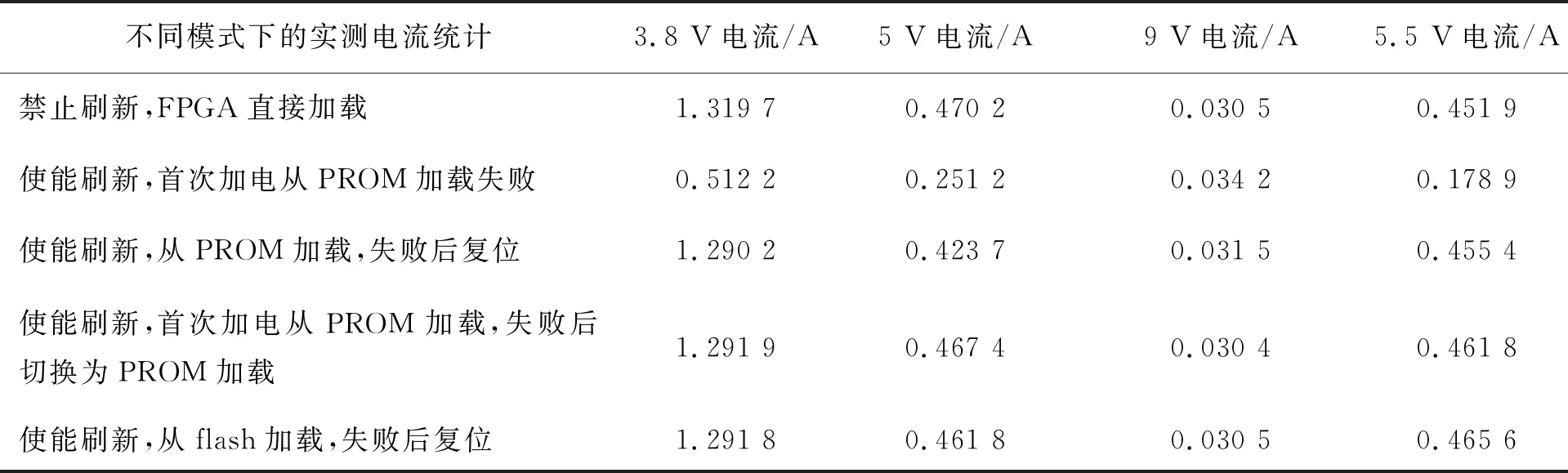

表2为不同工作模式下的加载结果,具体表现为工作电流的变化,如图5所示。

图5 未刷新使能的工作电流Fig.5 Operating current without refresh enable

表2 不同加载模式下的供电电流Tab.2 Supply current in different loading modes

3.2 刷新验证结果

(1)不刷新使能,烧入新的bit文件

刷新成像系统运行正常,输出正常的感光图像。

(2)刷新使能,烧入新的bit文件

刷新成像系统在正常摄像的状态下,通过JTAG口烧入新的bit流,烧入成功,结果输出图像的摄像状态停止了,重新发送摄像命令,然后才开始继续输出图像。说明刷新功能仅能实现恢复回原始的bit,并不能恢复回发生SEU前的状态,除非对配置相关外的数据进行三模冗余。

3.3 重注验证

(1)每包编程数据返回遥测值:编程成功。

(2)位流CRC校验结果:位流CRC校验成果。

(3)回读数据与编程数据的对比结果:回读数据与编程数据相同。

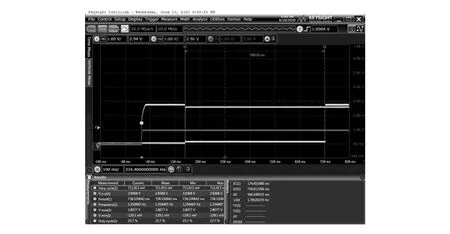

3.4 加载重注

刷新成像系统中FPGA芯片XQ5VFX100T的配置数据在刷新芯片的控制下,0.6 s内可完成上电加载配置(图6)。直接使用复旦微公司的上位机软件,刷新芯片串口波特率为固定的115.2 kbit/s,单包204 byte有效数据外还需要添加27 byte的帧头、帧长等数据,传输效率为88.3%,传输时间为2.01 ms。采用422串口助手,串行控制信号的波特率为625 kbit/s,单包204 byte有效数据外还需要添加32 byte的帧头、帧长、同步码、地址码等数据,传输效率为86.4%,传输时间为0.377 6 ms。

图6 FPGA加载配置时间长度测量结果Fig.6 Measurement length of FPGA load configuration time

4 结 论

本刷新成像系统可以实现FPGA配置数据源为PROM的主并工作方式加载,在刷新芯片控制下的配置数据源为PROM从并工作方式,也可以实现配置数据源为flash的从并工作方式,因此该系统具有很高的可靠性。可通过外部串行总线进行各组刷新程序的分时更新,因此具备设计灵活性和在轨可维护性。通过JTAG口烧入与加载数据不同位流,在刷新使能状态下会恢复为原数据流,证明刷新芯片能把改写的位流恢复,具备防单粒子的功能。要保证寄存器等数据不因单粒子事件而改写,还需要结合三模冗余等措施对关键信号和数据进行保护。