一种时域-频域并行处理的干扰检测方法

2021-07-13赵大恒王海龙黄彦勃张娅楠冀云成

赵大恒,王海龙,黄彦勃,张娅楠,冀云成

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.中国人民解放军63751部队,陕西 西安 710038;3.中国人民解放军61768部队,海南 三亚 572099)

0 引言

航天测控链路通常面临多种干扰源和多种干扰方式组成的复杂干扰环境,很大一部分电磁频谱都将受到严重污染。为保障航天测控链路的通畅,必须提高其抗干扰能力。

目前,国内外大多航天测控系统一般都采取直接序列扩频技术,也有系统采用扩跳频混合技术来增强链路抗干扰能力。但这些技术基本上都是属于“盲抗干扰”方式,其抗干扰能力有一定限度,一般都是在系统设计之初确定,不能轻易改变或仅能做有限改变。一旦对方干扰机采取的针对性干扰超出其干扰容限难免导致通信中断。在未来的战场上要保证测控链路可靠性,必须发展新的智能化的抗干扰测控技术来应对对方的各种干扰手段,要求测控系统的干扰检测与抗干扰一体化设计,才能保证测控链路抗干扰具有针对性和实时性。因此,研究测控链路干扰检测技术对提升测控链路的生存能力有着重要意义。

1 时域-频域并行处理的干扰检测方法概述

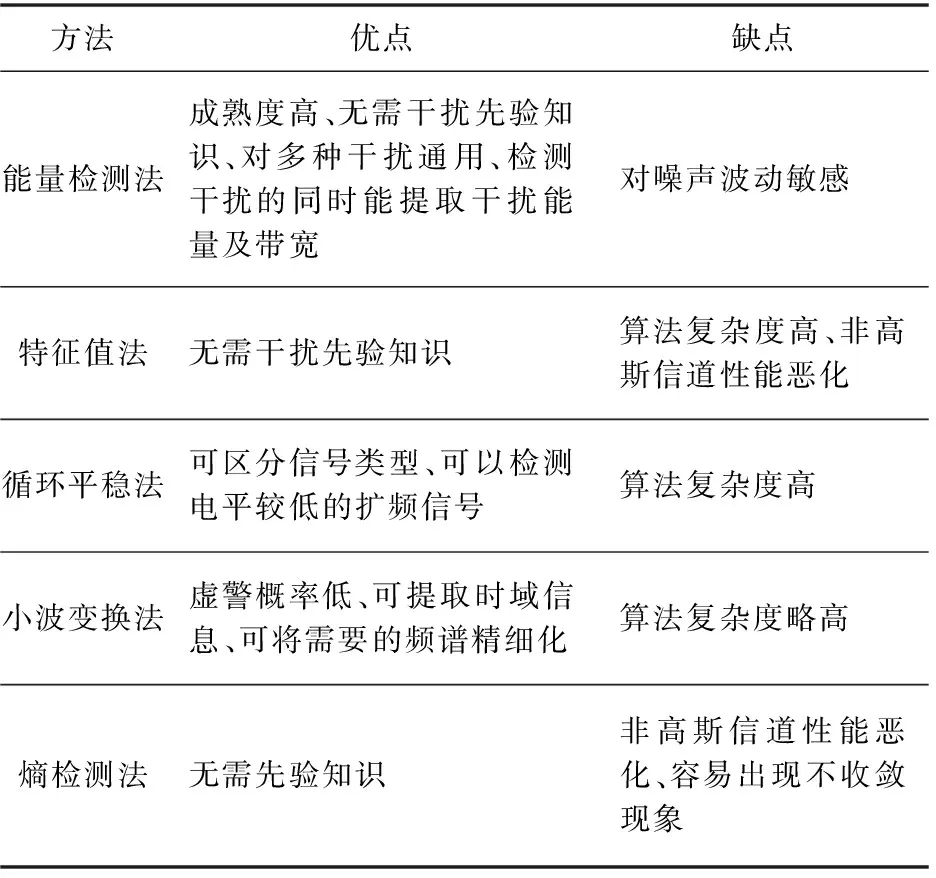

经典的干扰检测算法有能量检测法 (包括时域能量检测法[1-2]、频域能量检测法[3-4])、特征值法[5-6]、循环平稳法[6-8]、小波变换法[9]以及熵检测法[10]等,经典的干扰检测算法优缺点如表1所示。

表1 经典干扰检测算法优缺点

航天测控链路工作频率范围覆盖1~40 GHz,主要面临脉冲、单音、梳状、阻塞窄带、噪声调制以及其他设备的调制体制(如BPSK、QPSK、MFSK)等多种干扰类型的干扰,针对航天测控链路所需检测的干扰类型多、检测频段宽、实时性高及检测门限低等特点,将在能量检测算法、基于多相FFT滤波处理的频谱信道化方法基础上优化进行,形成基于多相FFT滤波信道化-能量检测相结合的、时域频域并行处理的宽频段干扰信号快速检测算法。

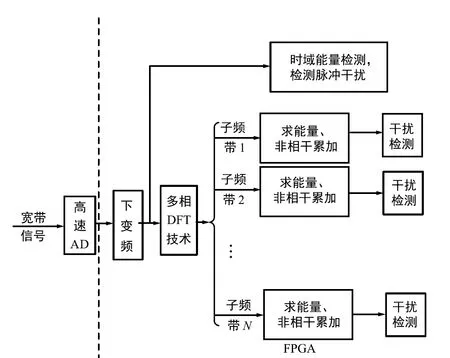

时域-频域并行处理干扰检测算法流程如图1所示。针对脉冲干扰瞬时功率大、平均功率低的特点,在时域对脉冲干扰进行检测;连续波干扰、突发干扰在频域进行检测。时域-频域并行处理干扰检测算法流程如图1所示。

宽带信号经过高速AD采样后,送入FPGA,经过下变频后在时域进行脉冲干扰存在性检测;同时将采样信号进行多相FFT处理,将宽带信号分成多个子频带,在频域同时对多个子频带进行干扰存在性检测。

图1 时域-频域并行处理干扰检测算法流程图Fig.1 Interference detection parallel processing algorithm in time domain and frequence domin

2 基于动态门限的时域脉冲干扰检测方法

工程应用时,脉冲干扰功率变化迅速,为防止干扰功率过大对系统造成损坏,需要实时对信道增益进行控制(AGC),这样导致采样信号的噪底实时变化,需要对噪底进行实时估计,生成动态参考门限进行脉冲干扰检测。脉冲干扰检测步骤如下:

步骤1:采样信号送入FPGA后,先下变频至零中频;

步骤2:对下变频的信号在时域求能量P=I2+Q2;

步骤3:将T1长度的时域信号能量累加在一起,连续求取N段Psum1,Psum2,...,PsumN,其中最小值为噪底,用于求检测参考门限;

步骤4:将时域采样点信号能量与参考门限进行比较,大于门限判为有干扰信号;

步骤5:重复步骤2~4。

脉冲干扰检测流程如图2所示。

图2 脉冲干扰时域检测法流程图Fig.2 Time domain detection method for pulse interference

3 基于多相FFT与区域能量检测的干扰信号检测方法

3.1 多相FFT技术

航天测控链路需要对宽广的频带进行干扰检测,从检测频谱分辨率、FPGA资源利用及程序稳定性等角度出发,将大点数FFT用多个小点数FFT实现。多相FFT技术是采用多相FFT算法的新型数字信道化接收机,将大点数的FFT分解为多个小点数的FFT的并行运算,可有效提高FFT算法的并行度,具有高效率、低资源消耗的特点。

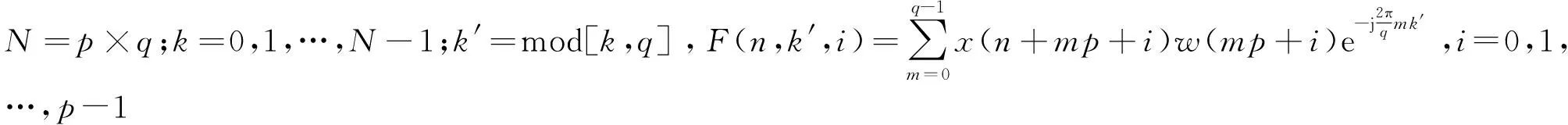

图3为多相FFT结构的算法模块,它也可以实现较理想的数字信道化接收机系统。式(1)为实现图3法结构的数学推导。

(1)

图3 多相FFT算法结构Fig.3 Algorithm structure of multiphase FFT

图3中,一帧数据(长度为N)被抽取为p路,每路q个点,加窗后通过q点的FFT模块后再进行q点串行p路并行的合成滤波,其中第i路的合成滤波器结构如图4所示。合成滤波器以先进先出方式,q点串行p路并行输入输出。

图4 合成滤波器结构Fig.4 Algorithm structure of synthetic filter

3.2 宽频段上的干扰信号快速检测方法

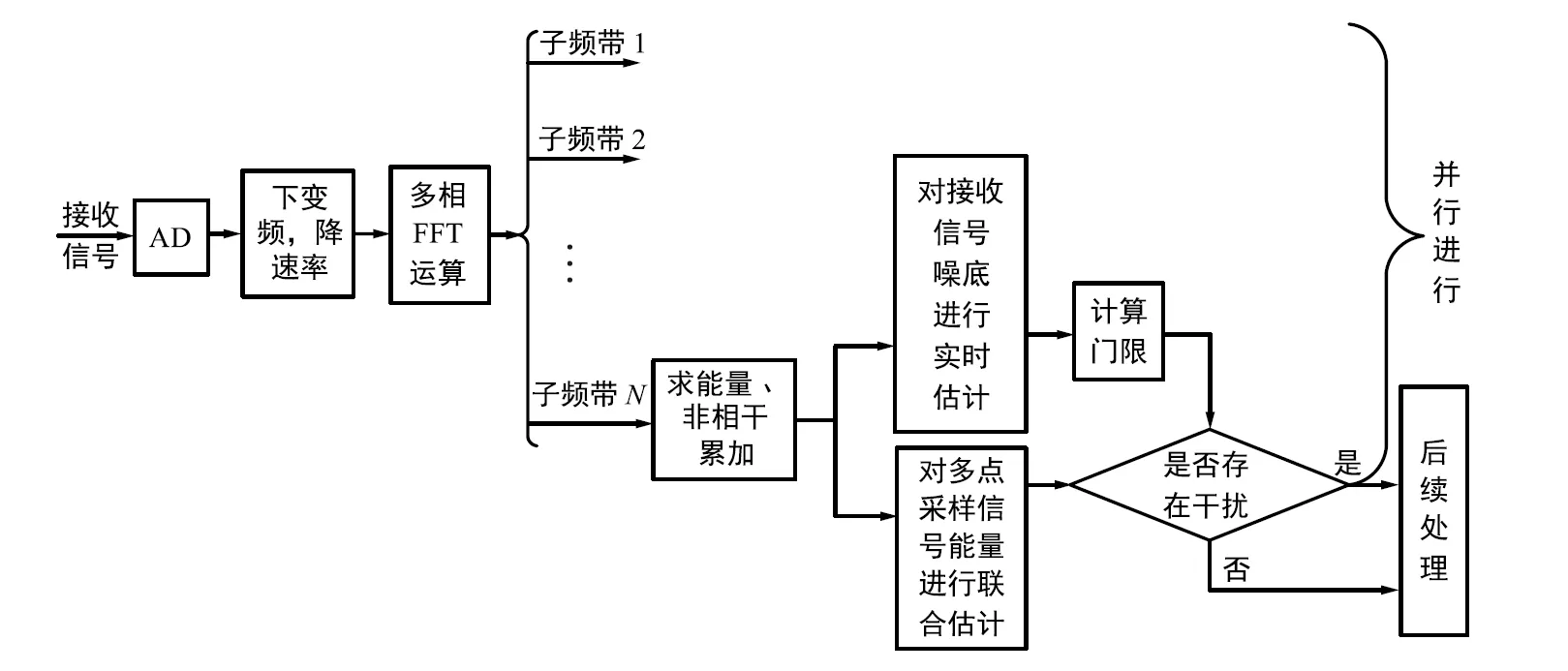

工程上单次检测的带宽为2 GHz,可将该频带分成多个子频带,并行在多个子频带上进行干扰信号快速检测。基于多相FFT技术与能量检测相结合的干扰信号快速检测算法的流程如图5所示。具体步骤如下。

步骤1:2 GHz带宽的信号经高速AD采样后,在FPGA中对中频信号下变频,将采样的信号变为I、Q两路;

步骤2:经过低通滤波器后进行抽取,采样率将变为原采样率的一半;

步骤3:采用多相FFT技术,进行262 144点FFT变换,将宽频带变为N个子频带;

步骤4:在子频带上对FFT结果求能量,进行多次非相干累加;

步骤5:将累加后的频谱每3个频点加到一起,进行谱对消;

步骤6:对非相干累加的结果及谱对消后的结果进行联合检测,完成干扰信号存在性检测。

通过多相FFT技术,将大点数FFT用多个小点数FFT实现(如将262 444点FFT用16个16 384点的FFT实现),同时2 GHz带宽(采样率5 GHz)的频谱将被分解成32个156.25 MHz的子频带,频域求每个频点的能量,将多次FFT的结果进行非相干累加,然后通过能量检测法在32个子频带上并行进行能量检测,2 GHz的频段需要100 ms的检测时间,从而完成超宽频段上的干扰快速检测。

图5 宽频段干扰信号快速检测算法的流程图Fig.5 Flow chart of fast detection algorithm for wideband interference signal

4 干扰检测能力试验、检测结果分析

针对所提的时域频域并行处理干扰检测方法,通过搭建试验环境的方式验证其性能。试验设备包括干扰源、信号源、衰减器、低噪声放大器、滤波器、频谱仪及干扰检测终端等。

干扰信号类型包括BPSK、噪声调频、单音、脉冲及梳状干扰等。干扰信号频率在0.2~2.2 GHz,干扰检测终端采样率5 GHz。在不同的干噪比下进行干扰检测试验,对待检测的各种干扰情况采用图6所示的试验测试框图进行连接,进行1 000次测试试验。

图6 试验测试框图Fig.6 Test block diagram

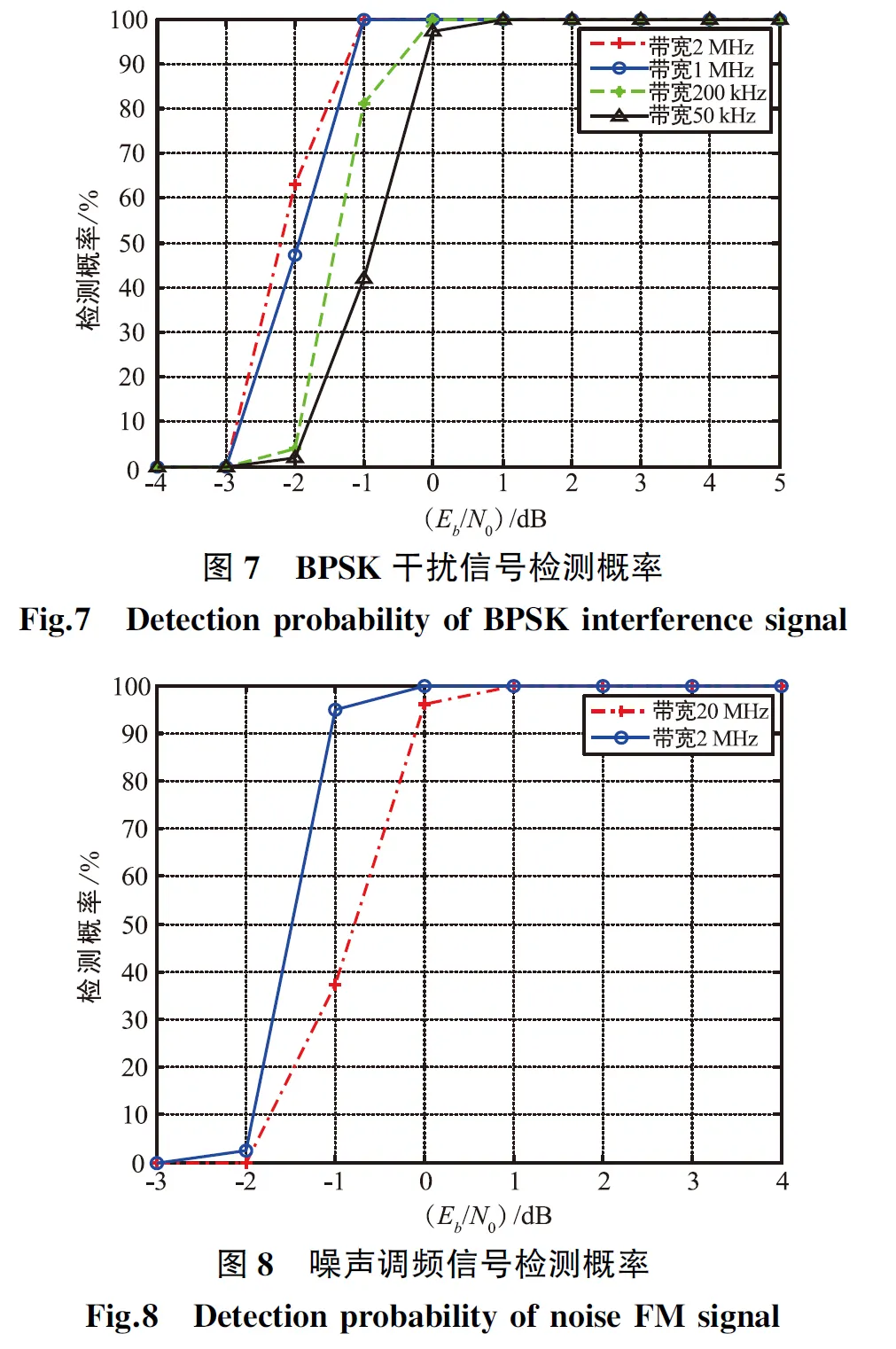

测试1:干扰信号形式为BPSK信号,信号中心频率在1 268.6 MHz。带宽分别为2 MHz、1 MHz、200 kHz、50 kHz的BPSK信号在不同的Eb/N0下的检测概率如图7所示。由图7可以看出,对于带宽大于50 kHz的BPSK干扰信号,在Eb/N0>0 dB时,检测概率大于90%;Eb/N0>1 dB时,检测概率大于95%。

测试2:干扰信号形式为噪声调频信号,信号中心频率在1 268.6 MHz。带宽分别为20 MHz、2 MHz的噪声调频信号在不同的干噪比下的检测概率如图8所示。由图8可以看出,在Eb/N0=0 dB时,对于2 MHz、20 MHz的噪声调频信号,检测概率达到90%以上。

图7 BPSK干扰信号检测概率Fig.7 Detection probability of BPSK interference signal

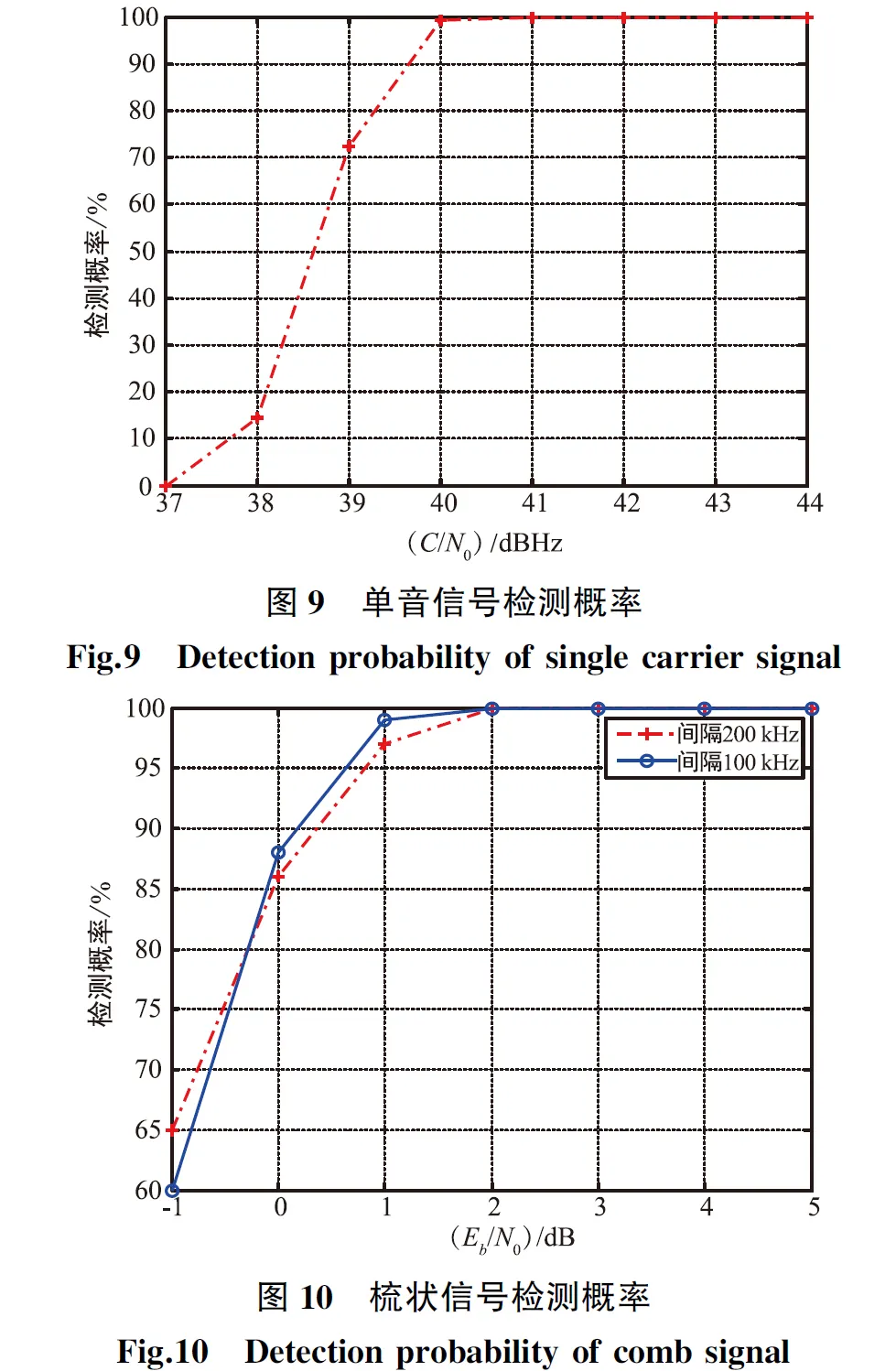

测试3:干扰信号形式为单音信号,信号中心频率在1 268.6 MHz,单音信号在不同的载噪比下的检测概率如图9所示。由图9可以看出,在C/N0为40 dBHz时,检测概率达到95%以上。

测试4:干扰信号形式为梳状干扰,信号中心频率在1 268.6 MHz,谱间隔分别为200 kHz、100 kHz的梳状信号在不同的干噪比下的检测概率如图10所示。由图10可以看出,在Eb/N0=1 dB时,检测概率达到95%以上。

测试5:信号中心频率在1 268.6 MHz,占空比分别为1:1000、1:500、1:200的、周期为1 s的脉冲信号在不同的载噪比下的检测概率如图11所示。由图11可以看出,在C/N0为49 dBHz时,检测概率达到95%以上。

图11 脉冲干扰信号检测概率Fig.11 Detection probability of pulse signal

5 FPGA资源消耗

Xilinx公司自带的FFT核采用串行结构,若信号带宽为2 GHz,经过下变频,数据速率变为I、Q两路后,信号带宽变为1 GHz,根据采样定理,则FFT数据处理时钟需要达到2 GHz以上,如此高速的时钟,FPGA芯片无法实现。此外FPGA芯片的FFT核运算时没有动态截位算法,造成中间过程数据位宽大、资源消耗大,导致内部DSP、BlockRAM资源占用消耗均大于文中设计的并行FFT核算法。

时域-频域并行处理干扰检测方法的FPGA资源消耗主要由3个算法模块构成:多相FFT算法、时域干扰检测算法和频域干扰检测算法。时频域并行处理的干扰检测方法与传统干扰的能量检测算法的资源消耗对比如表2所示(芯片选型为:XilinxV7-690T)。从表2可以看出,时域-频域并行干扰检测算法消耗的FPGA资源低于传统能量检测算法消耗资源的65%。

表2 FPGA资源消耗表

6 结论

时域-频域并行干扰检测方法的优点是干扰检测速度快、检测干扰种类多、适应宽频段、检测门限低、消耗的FPGA资源少、易于实现,能够同时处理多个干扰,有能力对变化的干扰环境快速反应。时域-频域并行快速干扰检测方法为后续抗干扰策略的制定提供了依据,提高了航天测控链路的生存能力。