一种低温漂系数的高性能基准电压源

2021-07-05段吉海符征裕黄秀玲

徐 江, 段吉海, 符征裕, 崔 鹏, 黄秀玲

(桂林电子科技大学 广西精密导航技术与应用重点实验室, 广西 桂林 541004)

现如今,物联网(IoT)系统的发展,如小型智能传感器,各种电子检测设备等,需要较长的工作时间,因此在IoT应用中,功耗变成衡量模拟集成电路的性能好坏的一个重要指标。另外集成电路的面积也是需要考虑的,因为它决定了芯片的集成度和成本。基准电压电路是IoT系统中集成电路的重要电路之一,为整个系统提供稳定的电流或电压[1]。带隙基准(BGR)由于具有较低的温漂特性而得到了广泛的应用。

传统带隙基准电路需要使用无源电阻和九个或更多的双极晶体管[2],产生基准电压,这样不管是功耗还是面积都是消耗很大。当带隙基准电路工作在纳米级电流时,需要使用较大的电阻器来产生适当的电压降,从而增加电路的面积。因此,传统的方法在纳瓦级功耗的应用中并不实用,如文献[3]采用正负温漂电流系数相互补偿的方法,功耗较大,且温漂性能不佳。文献[4]采用正负电阻补偿原理,得到基准电压及电流,增加电路面积的同时工艺偏差较大。文献[5]基准电压对电源电压较敏感,功耗较大,温漂性能欠佳。文献[6]采用标准的CMOS工艺实现,但芯片面积较大。

为了解决CMOS技术中功耗和芯片尺寸之间的折中问题,提出了一种具有纳瓦级功耗、高性能和无电阻的亚阈值基准电路。采用基准电压补偿电路单元结构,降低了温漂系数。

1 基准电压源架构

图1为整体电路框图。基准电压源包含纳安级电流源参考电路、基准电压产生电路及补偿单元。

图1 整体电路框图

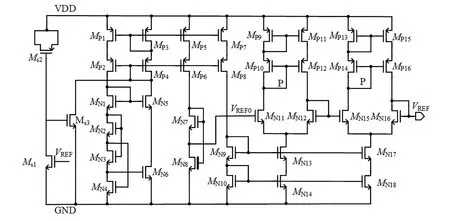

图2为上述电流模式基准电路的具体电路。启动电路先工作,保证电路正常工作,其次参考电流源电路为基准电压产生电路提供稳定的偏置电流,最后经过补偿单元作用,产生更低温漂系数的基准电压。所有基准核心电路晶体管工作在亚阈值区,降低了功耗及对电源电压的需求。

图2 电流模式基准电压源

启动电路由MS1~MS3管组成,使电路摆脱偏置点,进入正常的工作状态。晶体管MS2充当电容的作用,当参考电压为0 V时,电路开始对MS2充电,MS3的栅源电压(VGS3)随电源电压增大而增大,当VGS3大于MS3的阈值电压时,MS3导通,MP2、MP4的栅源电压被下拉到地,电流分别通过各支路晶体管,使得电路由零工作状态转换到正常工作状态,从而摆脱偏置点。当参考电压VREF大于MS1的阈值电压时,MS3的栅源电压被下拉到地,MS3管截止,启动电路到基准电路的电流通路被MS3管隔离,降低了启动电路对基准源的影响,完成整个启动过程。

1.1 亚阈值区电流特性

工作在亚阈值区的MOS管可以产生纳安级的电流,因此可以得到超低功耗的电路。当MOS管的漏源电压VDS约大于0.1 V时,亚阈值区的电流ID表达式为[3]

根据式(1),进一步化简,可得晶体管的栅源电压:

其中:K为晶体管的宽长比(W/L),VTH为晶体管的阈值电压;I0=μCOX(η-1)V2T为工艺参数,μ为电子迁移率,COX=εOX/tOX为栅氧化层电容,εOX为栅氧介电常数,tOX为栅氧厚度;η为损耗层与栅氧间的电容,一般为常数(不同的工艺下有不同的值),由损耗层与栅氧电容决定[3],在高精度应用中必须考虑这点。VT(=kBT/q)为热力学电压,kB为玻尔兹曼常数,T为绝对温度,q为电子电荷。

1.2 纳安级电流源产生电路

基于Oguey电流源[8]结构,且MOS管线性区电阻受工作在亚阈值区的2个MOS管的栅源电压差控制,从而产生稳定的偏置电流。同时采用cascode电流镜结构,改善了电路的电源抑制性能。

电流源参考电路如图2所示,由MP1~MP4、MN1~MN6管组成。MN2管工作在饱和区,采用MN2与MN3栅极相连到MN2漏端的方式,保证了MN3工作在线性区,作为恒定电阻。偏置电流由MN3管的漏源电压和导通电阻决定。此外, 保证除MN2管外其他晶体管都处在亚阈值区。

MN4、MN6管工作在亚阈值区,根据式(2),MN3管的漏源电压为

工作在线性区的MN3晶体管的导通电阻RN3近似为[7]

根据式(3)、(4)及VT=kBT/q,可计算出输出电流[8]:

其中,VON3=VGS3-VTH。从式(5)可看出,基准电流的表达式中只有VON3T1-m与温度相关,且m为介于1.5~2.0的常数[11],故指数因子1-m很小。因此,适当调整KN3ln(KN4/KN6)值,则偏置电流具有较低的温漂系数。

1.3 基准电压产生电路

基准电压产生电路包括MP5~MP6、MN7~MN8如图2所示。MN7管的器件模型的基准电压为1.8 V,MN8管的器件模型的基准电压为3.3 V。亚阈值区的MN7~MN8管由参考电流源产生的电流通过电流镜控制,降低了输出基准电压对温度的敏感。

从图2可知,VREF0由MN7~MN8管的栅源差电压产生,若忽略寄生二极管产生泄露电流[3]I0,根据式(2),假设η8=η7=η,则VREF0表达式为

其中,tOXN7、tOXN8分别为MN7、MN8管的栅氧化层厚度。晶体管阈值电压的温度特性可表示为[10]

忽略第二项后的值,进一步简化的阈值电压表达式为

其中:VTH(T0)为参考温度(T0≈300 K)下的阈值电压值;kt为温度变化的斜率,为负值[4]。根据式(6)、(8),可得:

式(9)中最后2项与温度相关,MN8的斜率|kTn8|远大于MN7的斜率|ktN7|,而VT与温度成正比,即负温漂系数(ktN8-ktN7)可被正温漂系数VT补偿。根据dVREF0/dT=0,适当调节KN7/KN8参数,就可产生对温度不敏感的VREF0表达式:

从式(10)可看出,理论上已经消除了温度对输出电压的影响,但由于高温下参考电压的正负温漂系数的非线性变化,不能完全相互消除。同时阈值电压温度特性的泰勒展开式中只存在低阶项的温度补偿,而忽略高阶项温度对基准电压的影响。因此,最后的基准电压幅度随温度存在一定的波动,需要对基准电压VREF0进一步补偿。

1.4 基准电压补偿单元

图3为基准电压补偿单元,主要由电流镜偏置的差分对组成,当晶体管工作在亚阈值区时,根据式(2),输入对管的栅极电压差可表示为[5]

图3 基准电压补偿单元

其中:KN1、KN2分别为输入对管的MN1、MN2的宽长比;KP1、KP2分别为PMOS电流镜的MP1、MP2的宽长比。通过式(11),可根据KN1KP2/KN2KP1的大小对基准电压进行补偿。

由于基准电压补偿单元每次的补偿精度不宜过大(过补偿会导致温漂性能下降),需要分多个补偿单元进行补偿[17]。当多个补偿单元级联时,其栅极输出电压为

其中:N为补偿单元的个数;KNi和KPi为对应下标晶体管的宽长比。根据式(9)、(12),可得最终的参考电压输出表达式:

式(13)完成了对式(9)的进一步温度补偿,令dVREF/dT=0,取适当的补偿单元个数,就可产生较低温漂系数的基准电压。图2为补偿单元电路,KP2i/KP2i-1=1,且采用Cascode结构,改善了电源抑制比性能[20]。基准电压输出表达式为

2 版图与仿真结果

基于标准 CMOS工艺下,基准电压源的版图如图4所示,面积仅为0.005 4 mm2。

图4 基准电压源的版图

当电源电压1.8 V时,功耗为115.7 nW。对基准电路进行仿真验证,电源抑制比的仿真曲线如图5所示。Cascode结构的补偿单元使得电源抑制比得到提升。在100 Hz时,电源抑制比(PSRR)为-63.5 dB。

图5 电源抑制比的仿真曲线

基准电压的温度曲线如图6所示,在-25~150 ℃温度范围,基准电压平均值为281.9 mV,温漂系数为3.91 ppm/℃。

图6 基准电压的温度曲线

电源电压在1.3~3.3 V范围内,电压调整率的仿真曲线如图7所示。输出基准电压的变化幅度为3.43 mV,电压调整率为0.58%。

图7 电源电压调整率的仿真曲线

图8为室温下基准电压VREF蒙特卡罗仿真结果。从图8可看出,平均值与标准差分别为281.97、23.52 mV。图9为基准电压温漂系数的蒙特卡罗仿真结果。从图9可看出,其温漂系数平均值为3.98 ppm/℃,标准差为3.52 ppm/℃。

图8 室温下VREF蒙特卡罗仿真结果

图9 VREF的温漂系数蒙特卡罗仿真结果

表1为设计的低温漂高性能基准电压源与其他文献的对比。本设计具有较低的温漂系数和电路功耗,温漂仅为3.91×10-6/℃,功耗为115.7 nW,电源抑制比达到了一般的水平,也有较宽的温度范围,比文献[7]稍差。

表1 本设计与其他文献中基准电压源的参数比较

3 结束语

提出了一种电压补偿模式的CMOS基准电源。基于0.18 μm CMOS工艺仿真结果表明,-25 ~150 ℃温度范围时,温度系数为3.91 ppm/℃。电源电压在1.3~3.3 V,有较好的线性调整率,在100 Hz时,PSRR达到-63.5 dB,功耗为115.7 nW。本设计的高性能基准电压源具有较低的温漂系数,较低的功耗,可应用于植入式高精度电路。