广播式自动相关监视信号接收机系统设计

2021-07-05许庆刘洪林

许庆 刘洪林

(航天工程大学士官学校 北京市 102200)

1 引言

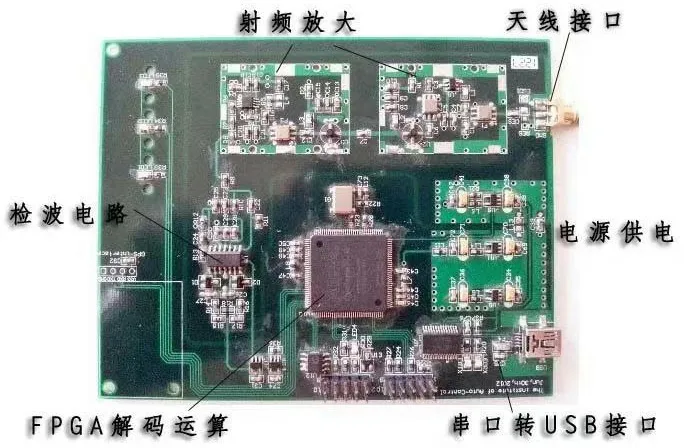

广播式自动相关监视(简称ADS‐B)技术标准是由国际民航组织所提供服务于空中交通管制的监视技术,ADS‐B 的出现对整个空管体系有着深远的影响。ADS‐B 下行方向的信号S 模式1090ES标准是由112 个信息脉冲构成的S 模式ADS‐B 长应答信号格式,内容包括经度、纬度、方位和速度等信息[1]。基于S 模式1090ES数据链的广播式自动相关监视信号接收机系统主要由电源供电、天线接口、射频放大、检波电路、FPGA 解码运算、通信接口5 部分组成[2]。电源供电:为USB 端口提供5V 的电源,经过DC‐DC 电源芯片转换为数字电路需要的3.3V 和1.2V 电源以及模拟电路需要的3.3V 电源;射频放大与检波电路:接收1090MHz 射频信号,经过多级滤波放大、检波、比较器等得到消息脉冲信号,输出给数组处理器;FPGA 解码运算:主要对消息脉冲进行处理,提取ADS‐B消息,也可以对GPS 消息进行处理,最终通过串行总线标准将数据发送给通信接口;通信接口:作为数字处理器和上位机之间的桥梁接收来自数字处理器的数据并上传给PC 机。

2 ADS-B接收机系统硬件电路设计

ADS‐B 接收机硬件电路主要分为射频前端和数字信号处理两部分。利用Protel99 se 设计软件实现电路原理图的设计、印制电路板设计、信号分析以及电路仿真等过程。

2.1 电源模块电路设计

电源模块分为3.3V 与1.2V 两部分电源电路。其中3.3V 电源电路选用德州仪器TPS62203 型DC‐DC 电源芯片。数字电源主要作为FPGA 的I/O 电源。模拟电源主要提供给射频放大电路以及检波电路。这款芯片是高精度的2.5‐6V 输入,300mA 同步降压转换器,它的开关频率典型值为1MHz,电压输出精度3%。电感起电源滤波作用,电容起滤除交流电压分量的作用。1.2V 电源选用德州仪器TPS62207 型DC‐DC 电源芯片作为FPGA 的内核供电电源。

2.2 射频前端电路设计

射频前端电路由三级带通滤波电路、两级MMIC 放大电路以及噪声放大电路共6 部分组成。第一级带通滤波电路,选用中心频率为1090MHz 的专用带通滤波集成芯片TA0970A。该芯片的输入和负载阻抗典型值为50Ω,输入功率最大值为20dBm,在1075~1105MHz 带宽内插入损耗典型值为2.3dB,纹波系数典型值为0.25dB,带内驻波比为1.8,带外衰减大于30dB 低噪声信号放大器高频电路,用于实现在不产生失真的条件情况下快速放大非常微弱的噪声信号,选用MAX2649 芯片。这种芯片设计可以有效保证系统能够在低频放大微弱音频信号时大大减少内部噪声系数,提高信号输出端的信噪比。它在3V 电源电压下的功耗电流应不得小于3.5mA,工作频率范围为400MHz~2500MHz,功率增益应不得大于14dB,噪声系数应不得小于1.3dB。

第二级带通滤波电路,后半段为第一级单片微波集成放大器电路选用SGA‐2486Z 芯片,该芯片为高性能的SiGe HBT MMIC 放大器,当输入频率为1950MHz 时,其增益为16.7dB。通过查阅芯片手册得到C8 的值为22pF,L2 的值为22nH。其外围元器件参数根据信号频率1090MHz 进行设计。第二级的单片微波集成放大器电路和第三级的带通滤波电路。芯片选择和外围设计同上。

2.3 检波模块电路设计

检波模块中的对数检波电路选用AD 公司的AD8313 型对数检波器芯片。该芯片工作频带为0.1GHz‐2.5GHz,可利用8 个级联的带宽为3.5GHz、增益为8dB 的限幅放大单元.在每个放大器的输出通过一个检波器将射频信号变换成基带。第9 个检波器设置在AD8313 的输入端,这9 个检波器的输出相加后具有分段的近似对数特性,然后再通过一个阻抗变换电元(兼低通滤波)转换成低阻抗电压棋式输出。

二阶滤波和峰值检波电路选用ST 公司的带四路运算放大器集成芯片TSH74CD。其中低通滤波器电路,主要用来滤除信号中无用的频率成分。芯片右侧部分分别设置了一个峰值信号测量检波控制电路。它这次采用了一个新的功率峰值计算机就是能够实时地跟踪记忆每个输入输出信号的功率峰值控制电路,输出每个信号的输入电压和输出频率,一直能够跟踪检测到每个输入输出信号的功率峰值,并始终能够保持跟踪到每个输入输出信号的最高功率峰值。

比较器和缓冲电路中的比较器选用了德州仪器的LMV7239 集成芯片,它的两个比较端分别是二级低通滤波的原始信号和经过峰值检波后的信号,两者比较得出有效脉冲,输出给右端的缓冲电路,再输出给数字处理器FPGA,这样可有效预防烧坏FPGA的I/O引脚。

2.4 通信接口电路设计

数据通信接口电路选用了串口转USB 的方式,主要完成USB对板卡供电和串口格式信息与USB 数据转换的功能,选用了FTDI公司FT232RL 芯片。该系统芯片设计采用的技术是一个单块实现USB 信号转换的异步低速串行通信接口设计芯片,它在内部外嵌USB 通信协议和总线,无需再自行编写用于USB 通信应用程序的任何固件,为低速异步串行数据通信接口系统设计提供了一个安全可靠的USB 通信解决模式方案。UART 两个接口器件可以同时支持8 比特的变频数据,1 位或2 位的数据停止位,奇、偶或复位没有信号校验;外部通讯波特率从300bps‐3mbps;内置256byte接收发送缓存接收传输缓存和128byte 接收发送缓存接受接收缓存;内部设计集成了1024biteeprom,它们还可以分别用来同时存储USBVID、PID、编号及其他相关电子产品的英文字符等;外部支持通用USB 直流供电、自主设备系统供电和通用总线式设备供电,此处理器采用的是USB 直流供电;为了更方便于与它和USB 两个接口器件进行互相匹配,内部分别设计集成了3.3v‐v 高压逻辑电平直流变频输入转换器;外部集成了1.8v‐5v 高压逻辑输入电压水平变频转换器,可以方便地与它和UART 两个接口器件进行互相匹配;外部支持5v/3.3v/2.8v/1.8v 复位电平变频输出复位电平变频输入;内部集成了一个上下供电复位电平控制电路;全内部变频时钟,不必外部时钟振荡器。芯片的串口通信端(1,5 引脚)与FPGA 的I/O 引脚连接,USB 端(15,16 引脚)与PC 机连接,(22,23 引脚)连接两个发光二极管指示灯。

2.5 FPGA数字逻辑电路设计

FPGA 数字逻辑电路的功能是对所收到的信号做进一步检测预处理。数字处理器采用Altera 公司的EP2C8T144I8 芯片,优势之处在于该芯片具备资源调用功能并且可以重复进行设计和修改。数据处理器的外围电路主要由时钟、复位、配置、以及存储等部分组成。其中工作时钟频率设定为 50MHz ,由50MHz 的晶体振荡器和处理器的时钟引脚进行连接。由于FPGA 是采用低电平的复位,因此在其中复位引脚通过一个复位电阻将输出端连接到3.3v ,另外输出端则通过一个复位按钮将输出端接地。Altera 可编程逻辑器件选用配主动配置和JTAG方式的串行配置器件EPCS16,优势在于成本较低,电路简单,安装便捷。存储电路采用SDRAM 作为大容量数据存储器,用于存储实时采集数据。最小系统电路原理图由官方提供,并不需要设计。数字逻辑电路主要包括消息提取模块、异步FIFO、串口通讯模块。

3 ADS-B接收机系统测试

为确定ADS‐B 接收机系统的有效性,通过硬件调试与联机测试验证接收机系统能够实时、连续地跟踪飞行目标。

3.1 系统硬件调试

接收机板卡的任务是通过带通滤波将天线上接收到的微弱高频回波信号从伴随的干扰和噪声中选择出来,并经放大和检波,最后解调出所需要的脉冲信号后送到终端设备。利用高频微波信号发生器输入可控的脉冲信号来代替接收天线充当微波信号源。设置在1.09GHz 的中心频率上,调节高频信号功率大小,观察板卡能否可以对数据进行正常接收和放大。输入信号功率在‐50dBm 条件下,测量射频放大的前端的脉冲信号证明可以有效接收。脉冲信号在示波器上很清晰地显示出来。

动态范围是接收机能够正常工作所允许的输入信号强度变化范围。用接收机前端最大允许输入功率与最小可检测功率之差表示。但通常情况下,对接收机有意义的是线性工作区,即线性动态范围,用接收机机开始出现过载时的输入功率与最小可检测功率之差表示。通过信号源测试,观察在输入不同的信号功率下,得到射频前端的线性变化区域在‐33dBm~‐89dBm 之间。当输入信号功率在‐80dBm 或更低时,接收机射频前端无法有效接收高频脉冲信号;当输入信号功率在‐80dBm~‐33dBm 之间时,接收机可以有效接收脉冲信号,并随输入信号功率的增加而线性放大;当输入信号功率超过‐33dBm 后,接收机不再线性放大从而进入饱和区。在测试过程中,我们测量了接收机前端对输入最大功率的耐受度,输入加至24dBm(信号源最大可能输出功率)时,前端仍未烧毁,但可以看到,接收机已明显饱和。

解调模块主要任务是将脉冲信号解调成完整形状的方波,通过调整信号源的输入信号功率,观察经解调后的脉冲信号发现,当输入信号低于‐75dBm 以后,解调模块虽然可以解调出有效的脉冲信号,但误码率明显增大,已经无法满足正常需求。

灵敏度表示接收机接收微弱信号的能力。通过测量射频末端最小可检测信号功率从而得到接收机实际灵敏度。调整输入信号功率通过观察射频前端的脉冲信号显示来确定接收机射频模块的灵敏度。通过测量发现,随着输入信号功率的减小,噪声增多,接收脉冲越不清晰。当功率为‐83dBm 时接收机无法正常接收输入脉冲信号,达到最小可检测信号功率。

带通特性的观察是利用信号发生器扫频的方式,通过频谱分析仪可以很清晰地看到解调模块的带通范围,噪声频谱图可以测量得到带内平坦度约为10dB。在接收天线输入广播式脉冲报文时,接收机板卡可以有效的接收信号脉冲。在连接接收天线的条件下,利用示波器测量板卡的FPGA 解码模块末端。通过示波器所显示的脉冲信号与1090ES 数据链的报文标准相比对,证明了接收板卡可以有效地对脉冲信号进行编解码得到正确的ADS‐B 报文信息。

3.2 系统联机调试

从分析的角度看,实时、精确、连续四在终端界面显示出ADS‐B 接收机跟踪飞机轨迹是研究最重要的部分。为此,针对系统功能的需求,在对ADS‐B 消息接收解码和跟踪滤波研究的基础上,基于ADS‐B 空情监测系统应用软件进行ADS‐B 接收机系统的联机测试。

ADS‐B 空情监测系统的最终目标是在指挥终端界面上实时、准确地显示航迹消息,因此ADS‐B 接收系统应满足实时管理跟踪的目标、模拟雷达显控终端显示、数据记录和回放等要求。在数字地图上叠加动态的飞机位置信息和航迹点、航道、空域等信息,实现对目标飞机的实时监控。该软件主要分为目标航迹显示区、目标信息显示区以及目标高度显示区。用户可以任意选择当前跟踪到的飞机来对其进行重点监控。在目标航迹显示区可设置为单一目标跟踪,显示区域的方位可以人工控制进行旋转,以方便指挥员下达训练调度指令。系统连接完成后,运行上位机预装好的ADS‐B 空情监视系统软件,系统就会进入正常工作状态。由于本文设计的ADS‐B接收机板卡中没有嵌入集成GPS 芯片,所以需要手动对本地的经纬度坐标进行预置,以确定目标航迹显示区的中心位置。参数设置完成后,开启系统就会对监测范围内的飞机目标进行实时跟踪。被跟踪的目标航迹、实时的位置(纬度、经度、高度)、飞机识别码等信息就会在目标监视界面的指定区域清晰地显示出来。

4 小结

本文提出了1090ES 数据链模式下ADS‐B 硬件接收机的设计思路。利用Protel 软件分析射频前端电路、通信接口电路、FPGA 数字逻辑电路及电源模块电路进行电路设计和功能介绍。基于ADS‐B接收机的结构和电路设计,开发了一种ADS‐B 接收机板卡,如图1所示,ADS‐B 接收机板卡采用4 层结构设计,层主要元件面,底层是辅助元件面,中间两层分别是接地层和电源层。其中与天线的接口为ARINC 429,与PC 机的接口为USB 2.0。通过硬件测试与联机测试,验证了ADS‐B 接收机系统的可行性与有效性。

图1:ADS-B 接收机系统板卡